ข่าว

ยุค DDR5 กำลังใกล้เข้ามาและไม่สามารถเพิกเฉยต่อความท้าทายใหม่ ๆ ได้

- ผู้เขียน:ROGER

- เผยแพร่เมื่อ:2023-12-04

ในความคลั่งไคล้ของปัญญาประดิษฐ์ (AI), การเรียนรู้ของเครื่อง (ML) และการขุดข้อมูลความต้องการในการประมวลผลข้อมูลของเราแสดงการเติบโตของดัชนีที่ไม่เคยเกิดขึ้นมาก่อนเมื่อเผชิญกับโอกาสนี้ความกว้างของแบนด์วิดท์หน่วยความจำได้กลายเป็น "หลอดเลือดแดง" ในยุคดิจิตอลในหมู่พวกเขาเทคโนโลยี DDR (Double Data Rate) ซึ่งเป็นที่รู้จักสำหรับอัตราการส่งข้อมูลสองครั้งและแบนด์วิดท์ที่สูงขึ้นเป็นหน่วยความจำการเข้าถึงแบบสุ่มแบบไดนามิก (DRAM) ได้ส่งเสริมการปรับปรุงประสิทธิภาพของคอมพิวเตอร์อย่างมากตั้งแต่แรกเกิดของเทคโนโลยี DDR รุ่นแรกในปี 2000 ถึง DDR5 ในปี 2020 เทคโนโลยี DDR แต่ละรุ่นได้รับการปรับปรุงอย่างมีนัยสำคัญในด้านต่าง ๆ เช่นแบนด์วิดท์ประสิทธิภาพและการใช้พลังงาน

วันนี้ไม่ว่าจะเป็นพีซีแล็ปท็อปหรือปัญญาประดิษฐ์อุตสาหกรรมต่าง ๆ กำลังเร่งตัวไปสู่ยุคใหม่ของ DDR5ในปีนี้ตลาด Generation AI กำลังเฟื่องฟูและเซิร์ฟเวอร์ AI ที่ใช้ในแอพพลิเคชั่นขนาดใหญ่ได้ส่งเสริมความต้องการ DDR5 อย่างจริงจังด้วยการฟื้นตัวของความต้องการตลาดหน่วยความจำซัพพลายเออร์ชิปหน่วยความจำได้แสดงกำลังการผลิตของ DDR5 ในไตรมาสที่สี่ของปีนี้เพื่อค่อยๆเปลี่ยน DDR4 ปัจจุบัน

ยุคใหม่ของ DDR5 มาถึงแล้วความท้าทายบางอย่างได้ขัดขวางการพัฒนาอุตสาหกรรมต่อไป

DDR5 ERA: ความท้าทายในการออกแบบเบื้องหลังประสิทธิภาพสูงสุด -ความเร็วสูง

ในเดือนกรกฎาคม 2563 มาตรฐานเทคโนโลยีหน่วยความจำ DDR5 ได้รับการปล่อยตัวอย่างเป็นทางการโดยทำเครื่องหมายว่าเทคโนโลยีหน่วยความจำเปิดบทใหม่DDR5 ได้รับความสนใจอย่างกว้างขวางด้วยแบนด์วิดท์และประสิทธิภาพที่สูงขึ้นเมื่อเทียบกับ DDR4 ก่อนหน้านี้ข้อได้เปรียบที่ใหญ่ที่สุดของ DDR5 คือมันได้ลดการใช้พลังงานอย่างมีนัยสำคัญและเพิ่มแบนด์วิดท์เป็นสองเท่าโดยเฉพาะอัตราสูงสุดของโปรโตคอลการเปิดตัวในปัจจุบันของ DDR5 ได้มาถึงแล้ว 6.4Gbpsความถี่สัญญาณนาฬิกาเพิ่มขึ้นจาก 1.6GHz เป็น 3.2GHz

เมื่อเราสำรวจรายละเอียดเพิ่มเติมของ DDR5 เรายังพบว่าเทคโนโลยีใหม่นี้ได้นำความท้าทายทางเทคนิคเพิ่มเติมมาบ้างตัวอย่างเช่นแรงดันไฟฟ้าของแหล่งจ่ายไฟของ DDR5 จะลดลง 0.1V โดย 1.2V จาก DDR4 ถึง 1.1V แม้ว่าแรงดันไฟฟ้าที่ลดลงจะช่วยลดการใช้พลังงานและยืดอายุการใช้งานแบตเตอรี่ ความท้าทายเช่นความท้าทายทางเทคนิคเช่นความท้าทายทางเทคนิคเช่นความท้าทายทางเทคนิคเช่นความท้าทายทางเทคนิคเช่นความท้าทายทางเทคนิคเช่นความท้าทายทางเทคนิคเช่น ความท้าทายทางเทคนิคบางอย่างเช่นความท้าทายทางเทคนิคเช่นความท้าทายทางเทคนิคบางอย่างตัวอย่างเช่นมีแนวโน้มที่จะถูกรบกวนด้วยเสียงรบกวนซึ่งทำให้ความสมบูรณ์ของสัญญาณมีความท้าทายมากขึ้นเนื่องจากปริมาณเสียงระหว่างแรงดันไฟฟ้า ระหว่างแรงดันไฟฟ้าระหว่างสวิตช์สัญญาณน้อยกว่าและอาจส่งผลต่อการออกแบบ

การเปลี่ยนแปลงที่สำคัญอีกประการหนึ่งของ DDR5 นั้นแตกต่างจากวิธีการจัดการชิปการจัดการพลังงาน (PMIC) ของ DDR4 ถูกรวมเข้ากับเมนบอร์ด DDR5 ถ่ายโอน IC การจัดการพลังงาน (PMIC) จากเมนบอร์ดไปยังโมดูลหน่วยความจำโดยตรงคู่ (DIMM)สิ่งนี้ช่วยให้การจัดการพลังงาน, การควบคุมแรงดันไฟฟ้าและลำดับพลังงาน -ตามลำดับไปยังทางกายภาพใกล้กับอุปกรณ์จัดเก็บข้อมูลบนโมดูลซึ่งยังช่วยให้มั่นใจว่าความสมบูรณ์ของแหล่งจ่ายไฟ (PI) และปรับปรุงการควบคุมวิธีการดำเนินงาน PMIC

นอกจากนี้เมื่อจำนวนบิตข้อมูลทั้งหมดยังคงไม่เปลี่ยนแปลงจำนวนช่องสัญญาณ DIMM จาก 1 ช่องไปยัง 2 ช่องทางก็เป็นความคืบหน้าสำคัญเช่นกันโดยการส่งข้อมูลไปยังการส่งช่องทางแคบสองช่องมันสามารถสร้างได้อย่างมีประสิทธิภาพและสร้างได้อย่างมีประสิทธิภาพมากขึ้น สัญญาณนาฬิกาเพื่อปรับปรุงความสมบูรณ์ของสัญญาณ

เห็นได้ชัดว่าการพัฒนามาตรฐาน DDR5 ได้คำนึงถึงปัญหาความสมบูรณ์ของสัญญาณและการถ่ายโอน PMIC ไปยังโมดูลจะออกแรงข้อได้เปรียบที่สอดคล้องกันอย่างไรก็ตามนักออกแบบยังคงต้องพิจารณาผลกระทบโดยรวมของความสมบูรณ์ของสัญญาณของแหล่งจ่ายไฟดังที่ได้กล่าวมาแล้ว DDR5 มีอัตราข้อมูลสูงถึง 6.4Gbps และความถี่นาฬิการะบบ 3.2GHz เสียงรบกวนพลังงานอาจทำให้เกิดปัญหาที่ชัดเจนมากขึ้นในการดำเนินการความเร็วสูงนี้ซึ่งจะส่งผลกระทบต่อประสิทธิภาพของระบบและความเสถียรของระบบหากวิเคราะห์ความสมบูรณ์ของพลังงานและความสมบูรณ์ของสัญญาณแยกกันปัญหาของเสียงรบกวนของแหล่งจ่ายไฟอาจพลาดได้

ดังนั้นเพื่อให้การเล่นเต็มรูปแบบกับประสิทธิภาพของ DDR5 จุดสำคัญทั้งหมดของระบบจะต้องรวมถึงชิปบรรจุภัณฑ์และ PCB สำหรับการวิเคราะห์ความสมบูรณ์ของสัญญาณของอิทธิพลของแหล่งจ่ายไฟอย่างไรก็ตามการวิเคราะห์ระดับนี้เป็นงานที่ซับซ้อนมันมีข้อกำหนดสูงสำหรับเครื่องมือฮาร์ดแวร์และซอฟต์แวร์ที่ใช้สำหรับการวิเคราะห์การจำลองสำหรับแพลตฟอร์มการคำนวณพื้นฐานความยากและความซับซ้อนของการออกแบบ

ปลดปล่อยศักยภาพของ DDR5, Cadence อย่างเต็มที่

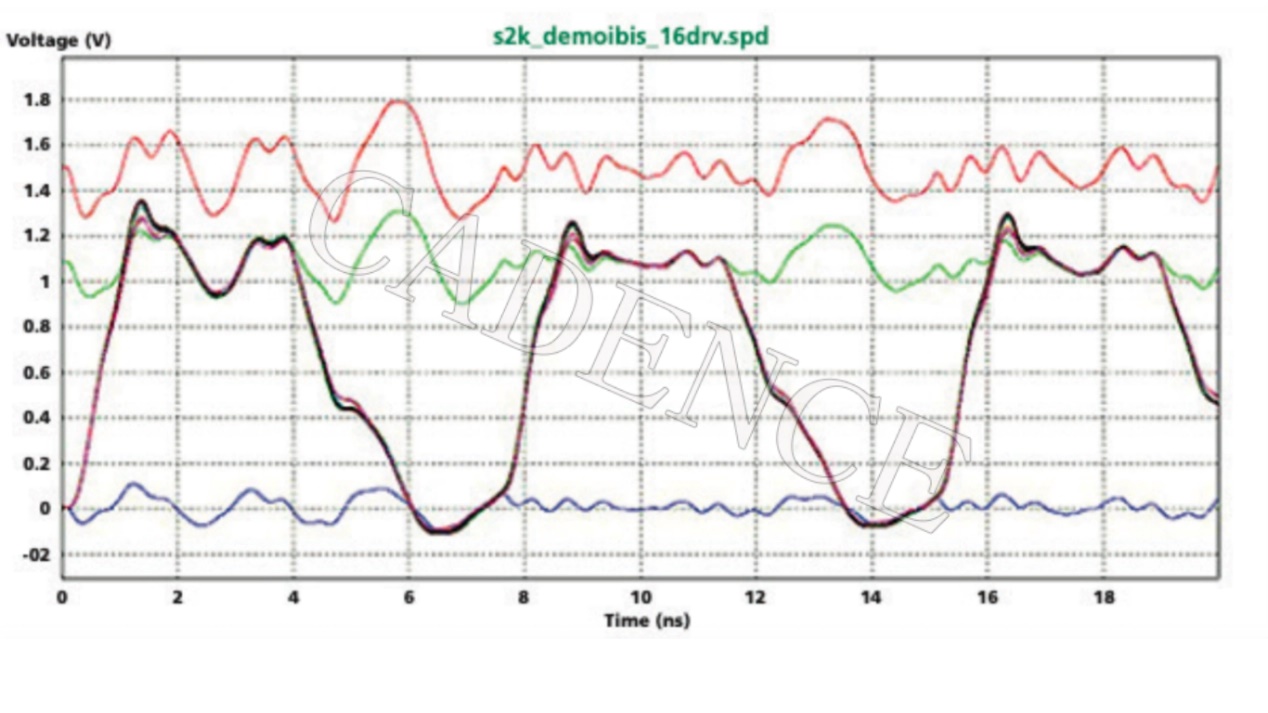

เร็วเท่าที่ปี 2005 แนวคิดของ "การคำนึงถึงอิทธิพลของแหล่งจ่ายไฟ" เปิดตัวเป็นครั้งแรกมันเป็นวิธีการจำลองความสมบูรณ์ของสัญญาณขั้นสูงที่สามารถวิเคราะห์สัญญาณและเสียงรบกวนในเวลาเดียวกัน (รูปที่ 1)โซลูชันความสมบูรณ์ของสัญญาณที่คำนึงถึงอิทธิพลของแหล่งจ่ายไฟจะต้องพิจารณาการสะท้อนการสต็อกลำดับและเอฟเฟกต์อื่น ๆ และพร้อมกับการจำลองที่สอดคล้องกันและเทคนิคการตรวจสอบกฎเป็นที่น่าสังเกตว่าเพื่อให้การจำลองความสมบูรณ์ของสัญญาณมีประสิทธิภาพซึ่งคำนึงถึงผลกระทบของแหล่งจ่ายไฟจำเป็นต้องดำเนินการในขั้นตอนการวิเคราะห์หลังจากการตรวจสอบและการเดินสายเป็นประจำเนื่องจากการโต้ตอบ/การมีเพศสัมพันธ์ของเครื่องบินและสัญญาณเกิดขึ้น หลังจากการเดินสายเสร็จสมบูรณ์

ดังนั้นจึงต้องมีการแก้ปัญหาที่สมบูรณ์ซึ่งคำนึงถึงอิทธิพลของแหล่งจ่ายไฟมักจะต้องมีให้:

l ชุดของโซลูชันการตรวจสอบที่รวดเร็วสำหรับการลดทอนสัญญาณและแหล่งจ่ายไฟบนสัญญาณ

l สามารถจำลองเวลาจำลองโดเมนของวงจรขนาดใหญ่ (ผลลัพธ์ของเครือข่ายสัญญาณหลายเครือข่ายและเครือข่ายพลังงาน)

l เครือข่ายพลังงานและการสร้างแบบจำลองเครือข่ายสัญญาณ

l สูง -ระดับอินพุต/เอาต์พุต (I/O) การสร้างแบบจำลองบัฟเฟอร์

รูปที่ 1: ผลลัพธ์ของความสมบูรณ์ของสัญญาณของทั้งสองอิทธิพลของแหล่งจ่ายไฟ

แม้ว่าเครื่องมือจำนวนมากในตลาดจะสนับสนุนมาตรฐานการสร้างแบบจำลอง I/O พื้นฐานที่คำนึงถึงอิทธิพลของแหล่งจ่ายไฟด้วยการพัฒนาเทคโนโลยีอินเทอร์เฟซหน่วยความจำอย่างต่อเนื่องความต้องการของตลาดสำหรับเครื่องมือความสมบูรณ์ของสัญญาณก็เพิ่มขึ้นเช่นกัน สัญญาณการมีเพศสัมพันธ์แหล่งจ่ายไฟและสัญญาณภาคพื้นดินบน PCB นั้นหายาก

ในเรื่องนี้ในฐานะองค์กรชั้นนำในด้านการจำลอง EDA เทคโนโลยี Sigrity X ที่เปิดตัวโดย Cadence ให้การวิเคราะห์ความสมบูรณ์ของสัญญาณของอิทธิพลของแหล่งจ่ายไฟสำหรับ DDR4 และ DDR5

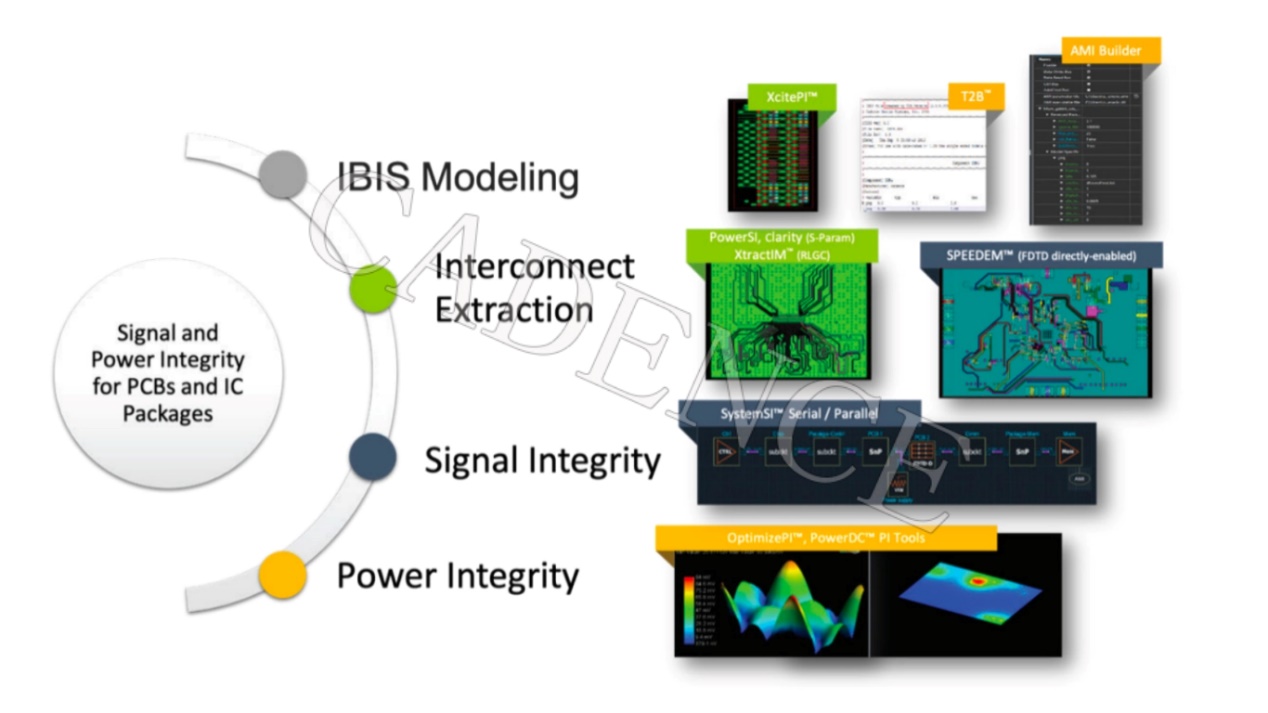

เทคโนโลยี Sigrity X ไม่เพียง แต่ตระหนักถึงการสกัดที่แม่นยำของสัญญาณคู่, แหล่งจ่ายไฟและสัญญาณพื้นดินบนชิป, บรรจุภัณฑ์และ PCB แต่ยังสามารถทำการจำลองที่มีประสิทธิภาพในการสะท้อนการสูญเสีย bandidal และ synchronous switch output (SSO) ที่เดียวกัน เวลา.นักออกแบบที่ใช้เทคโนโลยี Sigrity สามารถแปลงโมเดลระดับทรานซิสเตอร์ให้เป็นแบบจำลอง IBIS ระดับพฤติกรรมที่พิจารณาถึงอิทธิพลของพลังงานอย่างรวดเร็วดังนั้นภายในไม่กี่ชั่วโมงก็สามารถให้การจำลองผลกระทบของแหล่งจ่ายไฟซึ่งภายในไม่กี่ชั่วโมง ลดจำนวนเดิมของการกำหนดหมายเลขเดิมวงจรการออกแบบท้องฟ้า(รูปที่ 2)

รูปที่ 2: เครื่องมือความสมบูรณ์ของสัญญาณจังหวะและความสมบูรณ์ของพลังงานสำหรับบรรจุภัณฑ์ PCB และ IC

เทคโนโลยี Sigrity X ช่วยให้เวิร์กโฟลว์ง่ายขึ้นให้การจำลองแบบซิงโครนัสการออกแบบและความแม่นยำของระดับการลงนามสำหรับการตรวจสอบขั้นสุดท้ายสัญญาณไฟและปัญหาความร้อนสามารถแก้ไขได้ในแต่ละขั้นตอนการออกแบบซึ่งจะช่วยลดจำนวนการวนซ้ำระหว่างทีมการออกแบบและการวิเคราะห์นักออกแบบสามารถใช้งานเครื่องยนต์ระดับนิวเคลียร์ในการออกแบบผ้าวาดภาพสำหรับการจำลองที่มีความแม่นยำสูงจึงให้การออกแบบคุณภาพสูงสำหรับทีมวิเคราะห์เพื่อตรวจสอบต่อมาทีมวิเคราะห์ใช้กลไกการจำลองแบบขนานขนาดใหญ่ของ Sigrity เพื่อทำการจำลองระบบเต็มรูปแบบเพื่อให้แน่ใจว่าทั้งหมด "Chip-Packaging-PCB-Shell" ตรงตามข้อกำหนดการออกแบบและเตรียมพร้อมสำหรับการลงนาม

ข้อดีเหล่านี้ทำให้ Sigrity X เป็นทางออกที่ดีที่สุดสำหรับหน่วยความจำ DDR5 และอินเตอร์เฟส 112Gการสร้างแบบจำลองการเชื่อมต่อระหว่างกันสีทองของมันเป็นการรวมการจำลองโดเมนเวลา (การจำลองวงจรและช่องสัญญาณ) ของการวิเคราะห์อนุกรม/โซลูชัน (SERDES) และสนับสนุนอินเตอร์เฟสการสร้างแบบจำลองอัลกอริทึมของไอบิสอัลกอริทึม (AMI) ซึ่งให้ข้อได้เปรียบที่ไม่ซ้ำกัน โซลูชั่นที่สมบูรณ์

นอกจากนี้ Sigrity Xtractim และ Clarity 3D Solver Technology สามารถใช้ร่วมกันซึ่งช่วยให้วิศวกรสามารถสร้างโมเดลบรรจุภัณฑ์ที่สมบูรณ์ซึ่งมีสัญญาณการมีเพศสัมพันธ์แหล่งจ่ายไฟและแบบจำลองการเชื่อมต่อระหว่างกันสำหรับบรรจุภัณฑ์ประเภทต่างๆซึ่งประกอบขึ้นอย่างมีประสิทธิภาพสำหรับการออกแบบบรรจุภัณฑ์และคุณสมบัติบรรจุภัณฑ์ ช่องว่างระหว่าง

นอกจากนี้เทคโนโลยี Sigrity Systemsi ยังสนับสนุนโมเดล IBIS ที่สามารถเชื่อมต่อกับอิทธิพลของแหล่งจ่ายไฟและโมเดลการเชื่อมต่อโครงข่ายที่คำนึงถึงอิทธิพลของแหล่งจ่ายไฟอย่างรวดเร็วนักออกแบบสามารถกำหนดสถานการณ์ที่เลวร้ายที่สุดได้อย่างรวดเร็วผ่านเทคโนโลยีนี้และเปรียบเทียบกับ มาตรฐาน JEDEC เพื่อให้แน่ใจว่า DDR4/DDR5 อินเทอร์เฟซ (รวมถึงข้อกำหนดอัตรารหัสบิตที่ไม่มีบิต) เป็นไปตามข้อกำหนดที่เกี่ยวข้องทั้งหมด

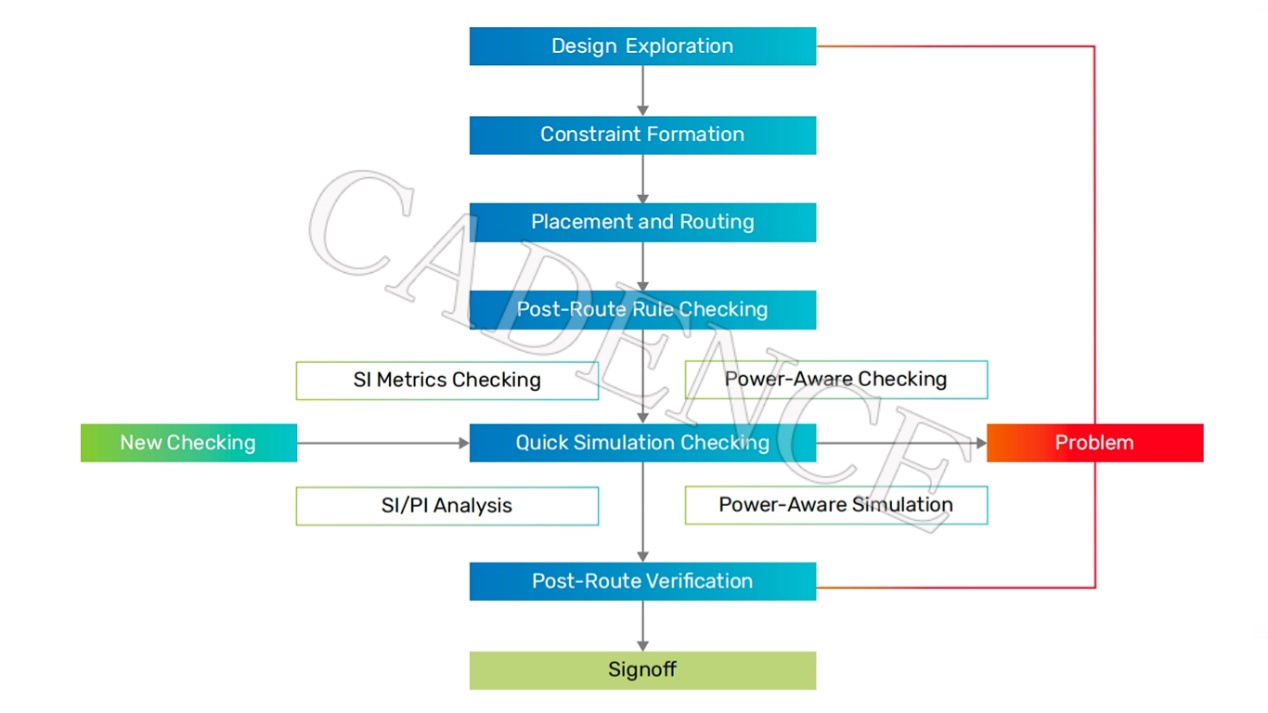

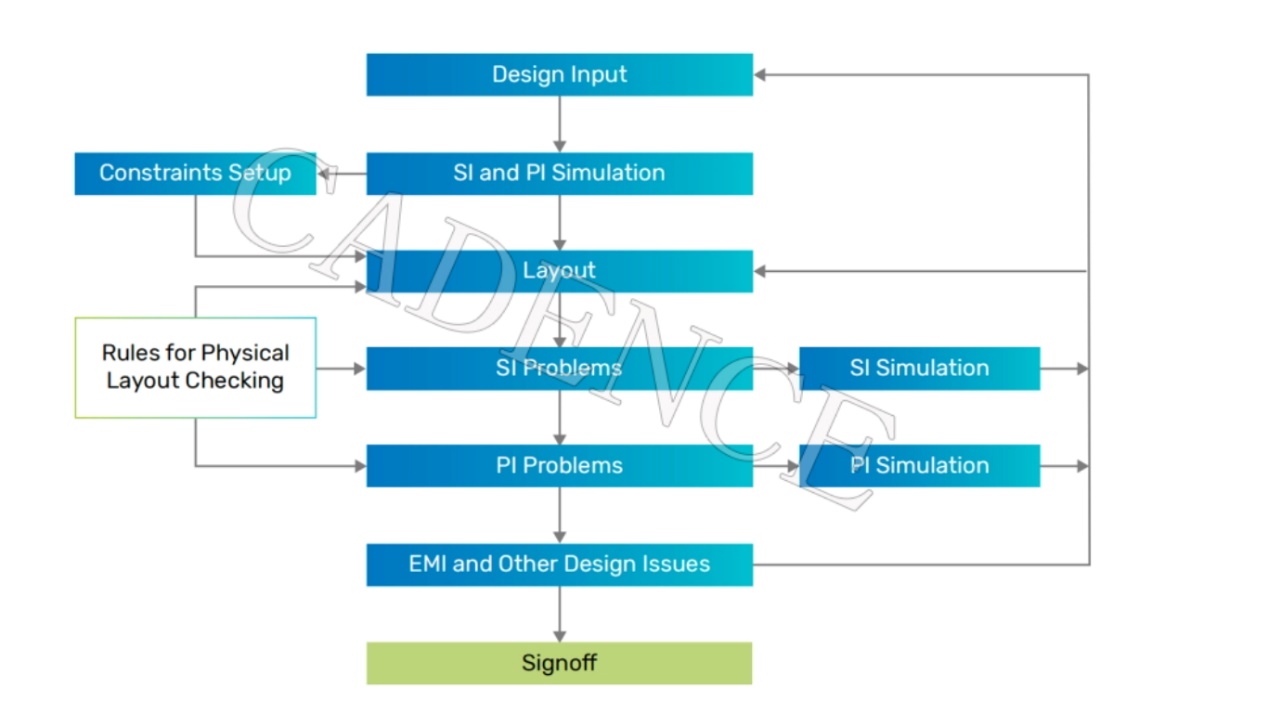

รูปที่ 3 คือกระบวนการตรวจสอบและจำลองสถานการณ์ที่คำนึงถึงอิทธิพลของแหล่งจ่ายไฟซึ่งตรงกันข้ามกับกระบวนการออกแบบข้อ จำกัด แบบดั้งเดิม (รูปที่ 4)กระบวนการออกแบบของตัวขับเคลื่อนข้อ จำกัด แบบดั้งเดิมส่วนใหญ่ประกอบด้วยสี่ส่วน: การเดินสายไฟล่วงหน้าการสร้างข้อ จำกัด การตรวจสอบกฎและการตรวจสอบการเดินสายโพสต์

รูปที่ 3: จังหวะคำนึงถึงกระบวนการขับเคลื่อนข้อ จำกัด ของอิทธิพลของแหล่งจ่ายไฟ

VS

รูปที่ 4: ตัวอย่างกระบวนการออกแบบไดรเวอร์ข้อ จำกัด แบบดั้งเดิม

ในบรรดาเทคโนโลยีการจำลองในปัจจุบันจำนวนมากมักจะมีการตัดการเชื่อมต่อระหว่างการวิเคราะห์สัญญาณและเครือข่ายการกระจายพลังงาน (PDN) และมีข้อบกพร่องอื่น ๆภายใต้สถานการณ์ปกติตามความซับซ้อนของแบบจำลองเครื่องเทศบางครั้งใช้การจำลองโดเมนเวลาเพื่อสร้างแบบจำลองความต้านทาน/การเหนี่ยวนำ/ตัวเก็บประจุที่แม่นยำ (RLC) และบางครั้งก็ถือว่าเป็นระนาบพื้นในอุดมคติโมเดลโดเมนเวลาที่ได้รับจากสิ่งนี้ขึ้นอยู่กับการตอบสนองความถี่อย่างง่ายของการสกัดการจำลองแม้ว่ามันจะสะดวกกว่า แต่ก็ไม่เพียงพอเล็กน้อยในแง่ของความแม่นยำสำหรับความถี่ที่สูงขึ้นวิศวกรจะใช้พารามิเตอร์ S ที่สร้างขึ้นโดยอุปกรณ์แก้ผสม

ในความเป็นจริงยังมีวิธีการที่มีประสิทธิภาพในการรวมวิธีการที่แตกต่างกันอย่าง จำกัด เวลาโดเมน (FDTD) เข้ากับอุปกรณ์แก้ผสมเพื่อขยายความครอบคลุมไปยังสัญญาณแหล่งจ่ายไฟและสายดิน

กรณีการปฏิบัติที่ประสบความสำเร็จของวิธีนี้คือเครื่องมือเครื่องยนต์ Sigrity Speed2000 ของ Cadence มันรวมและรวมเอาท์พุทของโซลูชันหลายอย่างเพื่อแก้ปัญหาการเดินสายวงจรสายส่งและปัญหาสนามแม่เหล็กไฟฟ้า ครั้ง.และใช้วิธี FDTD เพื่อวิเคราะห์เค้าโครงของบรรจุภัณฑ์ IC และ PCBมันให้พื้นฐานการอ้างอิงที่สำคัญสำหรับการเพิ่มประสิทธิภาพของการออกแบบวงจรเพิ่มเติม

เมื่อเข้าสู่ขั้นตอนการลงนามขั้นสุดท้ายวิศวกรมักจะใช้วิธีการสร้างแบบจำลอง 3D แบบเต็มรูปแบบเพื่อให้ได้ความแม่นยำสูงขึ้นแต่สิ่งนี้จะใช้ทรัพยากรการคำนวณมากขึ้นและเพิ่มเวลาการจำลองเพื่อบรรเทาปัญหานี้สามารถใช้เทคโนโลยีการหารและการทำให้ขนานกันได้ในเรื่องนี้โดยการใช้ตัวแก้ปัญหาความชัดเจน 3D สำหรับการวิเคราะห์การวิเคราะห์องค์ประกอบไฟไนต์ (FEM) จากนั้นรวมเทคโนโลยี Sigrity Xtractim ผลลัพธ์ของการวิเคราะห์แต่ละครั้งจะถูกรวมเข้าด้วยกันเพื่อสร้างแบบจำลองพารามิเตอร์ S ตามการตอบสนองความถี่ ระบบทั้งหมดไปยังระบบทั้งหมดหรือในเชิงลึกและการวิเคราะห์การออกแบบที่แม่นยำ

สรุป

ในเวลาเดียวกันกับการก้าวกระโดดทางเทคโนโลยีเทคโนโลยีได้รับการปรับปรุงและเป็นสิ่งที่หลีกเลี่ยงไม่ได้ที่จะวางความท้าทายใหม่สำหรับนักออกแบบระหว่างทางไปสู่หน่วยความจำ DDR5 และความท้าทายใหม่ ๆ ด้วย "ใบมีดคม" ที่คมชัดของ Cadence Sigrity X วิศวกรสามารถรับมือกับปัญหาที่ซับซ้อนของความสมบูรณ์ของสัญญาณได้อย่างสงบ ประสิทธิภาพเพิ่มอิฐอีกแห่งหนึ่งไปยังถนนแห่งนวัตกรรมในอนาคต