Новини

Ерата на DDR5 се приближава и новите предизвикателства не могат да бъдат игнорирани

- автор:ROGER

- Освободете се:2023-12-04

В яростта на изкуствения интелект (AI), машинното обучение (ML) и извличането на данни желанието ни за обработка на данни показва безпрецедентен растеж на индекса.Изправен пред тази перспектива, ширината на честотната лента на паметта се превърна в ключова „артерии“ в дигиталната ера.Сред тях технологията DDR (двойна скорост на данни), известна с двойни скорости на предаване на данни и по -висока честотна лента като динамична памет за произволен достъп (DRAM), значително насърчи подобряването на компютърната производителност.От раждането на първото поколение DDR технология през 2000 г. до DDR5 през 2020 г., всяко поколение DDR технологии постигна значителни подобрения в различни аспекти като честотна лента, производителност и консумация на енергия.

Днес, независимо дали става въпрос за компютър, лаптоп или изкуствен интелект, различни индустрии се ускоряват да преминат към новата ера на DDR5.Тази година пазарът на AI Generation процъфтява и AI сървърите, използвани в приложения за големи модели, енергично насърчават търсенето на DDR5.С възстановяването на пазара на търсенето на памет, доставчиците на чипове на паметта показаха производствения капацитет на DDR5 през четвъртото тримесечие на тази година, за да заменят постепенно текущия DDR4.

Новата ера на DDR5 пристигна, но някои предизвикателства също възпрепятстват по -нататъшното развитие на индустрията.

DDR5 ERA: предизвикателства за дизайна зад ултра -висока ефективност

През юли 2020 г. официално беше публикуван стандартът за технологии за памет DDR5, отбелязвайки, че технологията на паметта отвори нова глава.DDR5 привлече широко внимание с по -голяма честотна лента и производителност.В сравнение с предишния DDR4, най -голямото предимство на DDR5 е, че той има значително намалена консумация на енергия и удвои честотната лента.По -конкретно, най -високата скорост на текущия протокол за освобождаване на DDR5 е достигнала 6.4GbpsЧестотата на часовника също се увеличава от 1,6GHz до 3.2GHz.

Когато изследваме повече подробности за DDR5, откриваме също, че тази нова технология е донесла някои допълнителни технически предизвикателства.Например, напрежението на захранването на DDR5 намалява с 0,1V с 1,2 V от DDR4, достигайки 1.1V. Въпреки че по -ниското напрежение на захранването намалява консумацията на енергия и удължава живота на батерията, то също носи някои технически предизвикателства, като например технически технически Предизвикателства като технически предизвикателства, като например някои технически предизвикателства, като например някои технически предизвикателства, като например някои технически предизвикателства, като например някои технически предизвикателства, като например като Някои технически предизвикателства, като например технически предизвикателства, като например някои технически предизвикателства. Например, по -вероятно е да се нарушава от шума, което прави целостта на сигнала по -предизвикателна, тъй като количеството шум между напрежението Между напрежението по време на превключвателя на сигнала е по -малко и може да повлияе на дизайна.

Друга основна промяна на DDR5 е различна от начина, по който чипът за управление на захранването (PMIC) на DDR4 е интегриран на дънната платка. DDR5 прехвърли IC за управление на захранването (PMIC) от дънната платка към модула за директна памет с двойна колона (DIMM).Това дава възможност за управление на мощността, регулиране на напрежението и последователност на мощност до физическо по -близо до устройството за съхранение на модула, което също помага да се гарантира целостта на захранването (PI) и да се подобри контрола на метода на PMIC работа.

В допълнение, когато общият брой битове на данни остава непроменен, броят на DIMM канали от 1 канал до 2 канала също е важен напредък. Чрез предаване на данни в две тесни канали, той може да бъде по -ефективно генериран и генериран по -ефективно присвояване Часовник сигнали за подобряване на целостта на сигнала.

Очевидно разработването на стандарта DDR5 също е взел предвид проблема с целостта на сигнала, а прехвърлянето на PMIC към модула също ще упражнява съответните предимства.Въпреки това, дизайнерите все още трябва да вземат предвид цялостния ефект от целостта на сигнала на захранването.Както бе споменато по -горе, DDR5 има скорост на данни до 6,4 Gbps и 3,2GHz системен часовник честота. Силата шум може да причини по -очевидни проблеми при тази висока работа с висока скорост, което ще повлияе на работата и стабилността на системата.Ако целостта на мощността и целостта на сигнала се анализират отделно, проблемът с шума от захранването може да бъде пропуснат.

Следователно, за да се даде пълна игра на производителността на DDR5, всички ключови точки на системата трябва да включват чипове, опаковки и PCB за анализ на целостта на сигнала за влиянието на захранването.Анализът на това ниво обаче е сложна задача. Той има високи изисквания за хардуерните и софтуерните инструменти, използвани за симулационен анализ за основната компютърна платформа. Трудността и сложността на дизайна.

Напълно освободете потенциала на DDR5, каданс

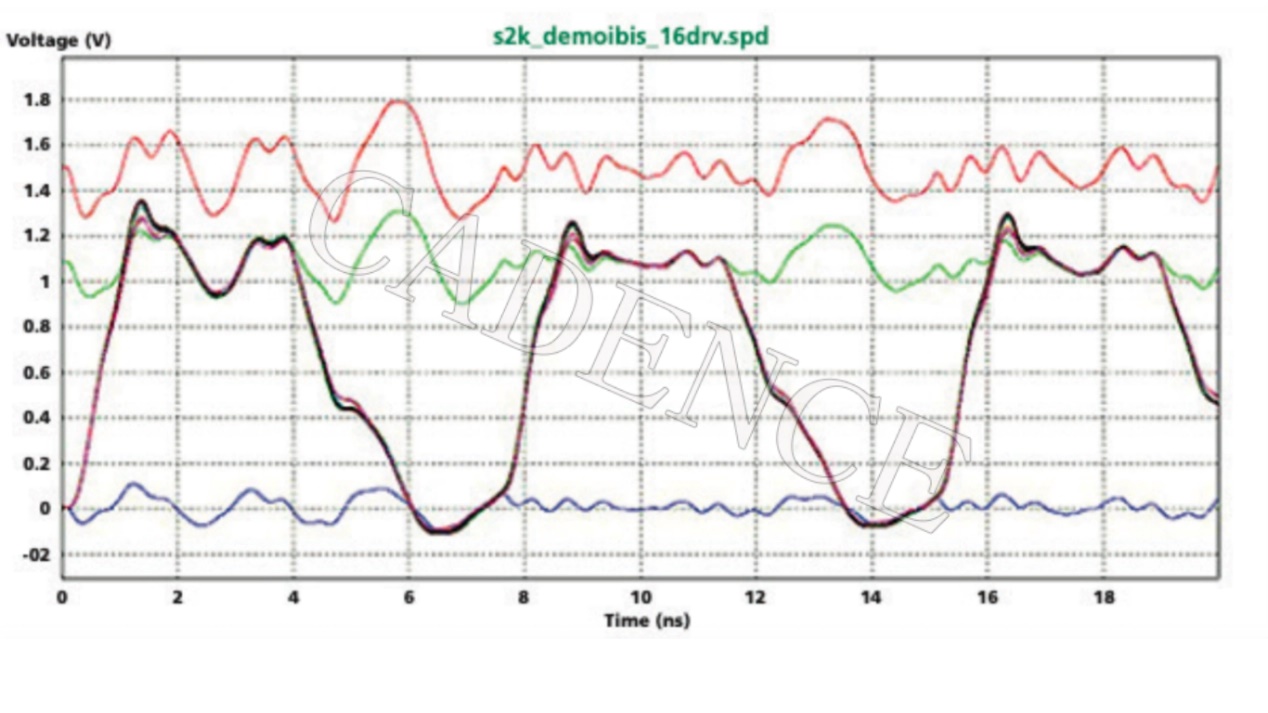

Още през 2005 г. концепцията за „отчитане на влиянието на захранването“ дебютира за първи път. Това е метод за симулация на усъвършенствана сигнализация, който може да анализира сигналите и шума на мощността едновременно (Фигура 1).Решението за целостта на сигнала, което отчита влиянието на захранването, трябва да обмисли отражение, нанизване, последователни и други ефекти и оборудвано със съответните техники за проверка на симулацията и правилата.Заслужава да се отбележи, че за ефективно прилагане на симулацията на целостта на сигнала, която отчита въздействието на захранването, е необходимо да се извърши във фазата на анализ след редовна проверка и окабеляване, тъй като възникването на взаимодействието/свързването на равнината и сигнала се случва След приключване на окабеляването.

Следователно, пълно решение, което отчита влиянието на захранването, често трябва да се предоставя:

l Набор от решения за бърза проверка за затихване на сигнала и захранване на сигнали

l Може да симулира симулатора на времеви домейни на големи вериги (резултатите от множество сигнални мрежи и захранващи мрежи)

L моделиране на захранваща мрежа и сигнална мрежа

l Вход/изход на високо ниво (I/O) Буферно моделиране

Фигура 1: Резултатът от целостта на сигнала както на влиянието на захранването

Въпреки че много инструменти на пазара поддържат основните стандарти за моделиране на I/O, които отчитат влиянието на захранването, с непрекъснатото развитие на технологията на интерфейса на паметта, изискванията на пазара за инструменти за цялостност на сигнала също се увеличават. Точният инструмент за извличане на инструмента за извличане на инструмента за извличане на инструмента за извличане на инструмента за извличане на инструмента за извличане на инструмента за извличане на инструмента за точна извличане на инструмента за извличане на инструмента за извличане на точния инструмент за извличане на инструмента за извличане на точния извличане на инструмента за извличане на точния инструмент за извличане на точното извличане на инструмента за извличане. Свързващият сигнал, захранващ и заземен сигнал на PCB е рядкост.

В тази връзка, като водещо предприятие в областта на симулацията на EDA, технологията Sigrity X, стартирана от Cadence, предоставя анализ на целостта на сигнала на влиянието на захранването за DDR4 и DDR5.

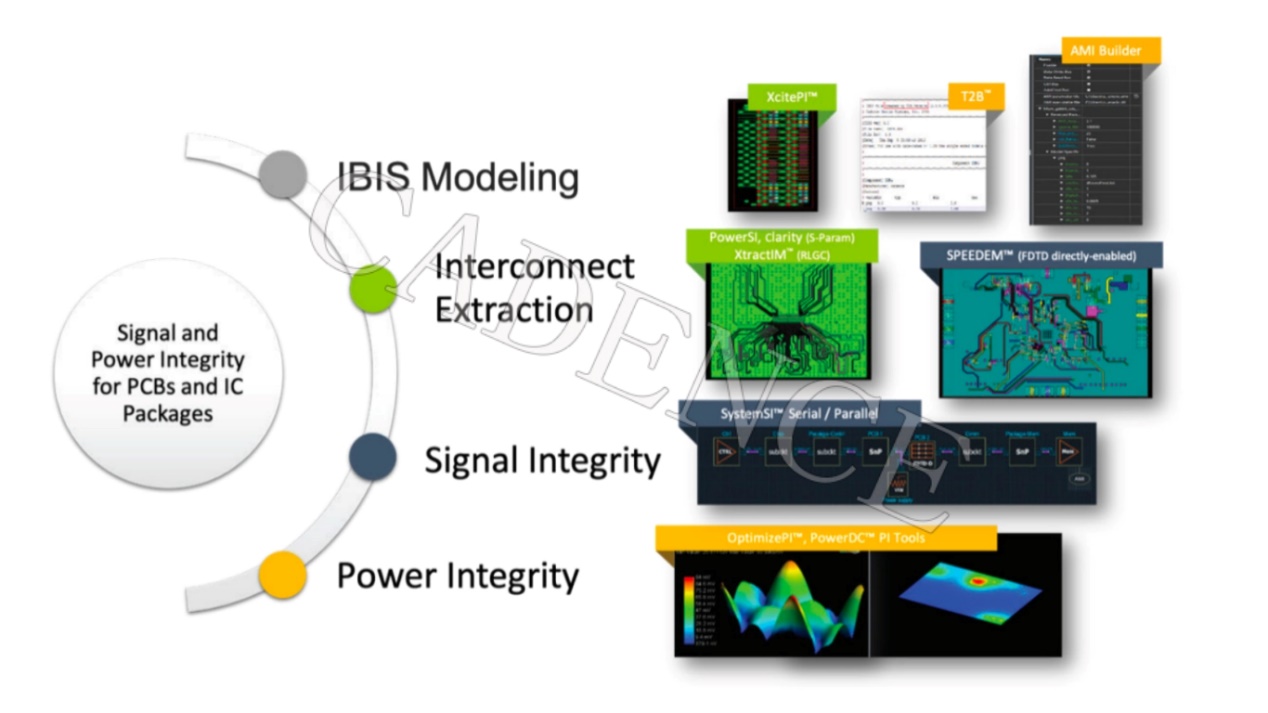

Технологията Sigrity X не само осъзнава точното извличане на свързани сигнали, сигнали за захранване и заземяване на чипове, опаковки и печатни платки, но също така може също да направи ефективна симулация на отражение, загуба, бандидал и синхронни резултати (SSO) на същите при същите ефекти време.Дизайнерите, използващи технологията на SIGRITY, могат бързо да преобразуват модела на ниво транзистор в модел на IBIS в поведенческо ниво, който разглежда влиянието на мощността, така че в рамките на няколко часа, той може да осигури прецизно, ефективно и всеобхватно, като се има предвид симулирането на ефектите на захранване, което значително може Скъпи първоначалния брой първоначално трябва да бъде номериран. Цикъл на дизайн на небето.(Фигура 2)

Фигура 2: Инструмент за целостта на сигнала и целостта на мощността за PCB и IC опаковки

Технологията Sigrity X опростява работния процес, осигурява дизайнерска синхронна симулация и точността на нивото на подписване за окончателна проверка.Сигналите, мощността и топлинните проблеми могат да бъдат решени на всеки етап на проектиране, като по този начин намаляват броя на повторенията между екипите за проектиране и анализ.Дизайнерите могат да управляват двигателя на ядреното ниво в дизайна на чертежния плат за симулация с висока точност, като по този начин осигуряват висококачествен дизайн на екипите за анализ, които да проверят.По-късно екипът за анализ използва мащабния паралелен симулационен двигател на SIGRITY, за да направи пълна симулация на системата, за да гарантира, че целият "чип-пакета-PCB-черупка" отговаря на спецификациите на дизайна и се подготвя за подписването.

Тези предимства правят SIGRITY X най -доброто решение за DDR5 памет и 112G интерфейс.Неговото златно стандартно моделиране на взаимосвързаност комбинира симулацията на времеви домейни (симулация на верига и канал) на анализа на серийния/разтвор (SERDES) и поддържане на интерфейса за моделиране на алгоритмите на IBI Пълни решения.

Освен това, технологията Sigrity Xtractim и Clarity 3D Solver може да се използва съвместно, което позволява на инженерите да създават пълни модели за опаковане, съдържащи сигнали за свързване, модели за захранване и заземяване на модели за различни видове опаковки, които ефективно съставляват дизайна на опаковките и пакетите Разликата между.

В допълнение, технологията Sigrity Systemi поддържа модела IBIS, който може бързо да се свърже с влиянието на захранването и модела на взаимосвързаност, който отчита влиянието на захранването. Дизайнерът може бързо да определи най -лошата ситуация чрез тази технология и да я сравни с Jedec стандарт, за да се гарантира, че DDR4/DDR5 Интерфейсът (включително изискванията за скорост на битовия код) отговаря на всички подходящи спецификации.

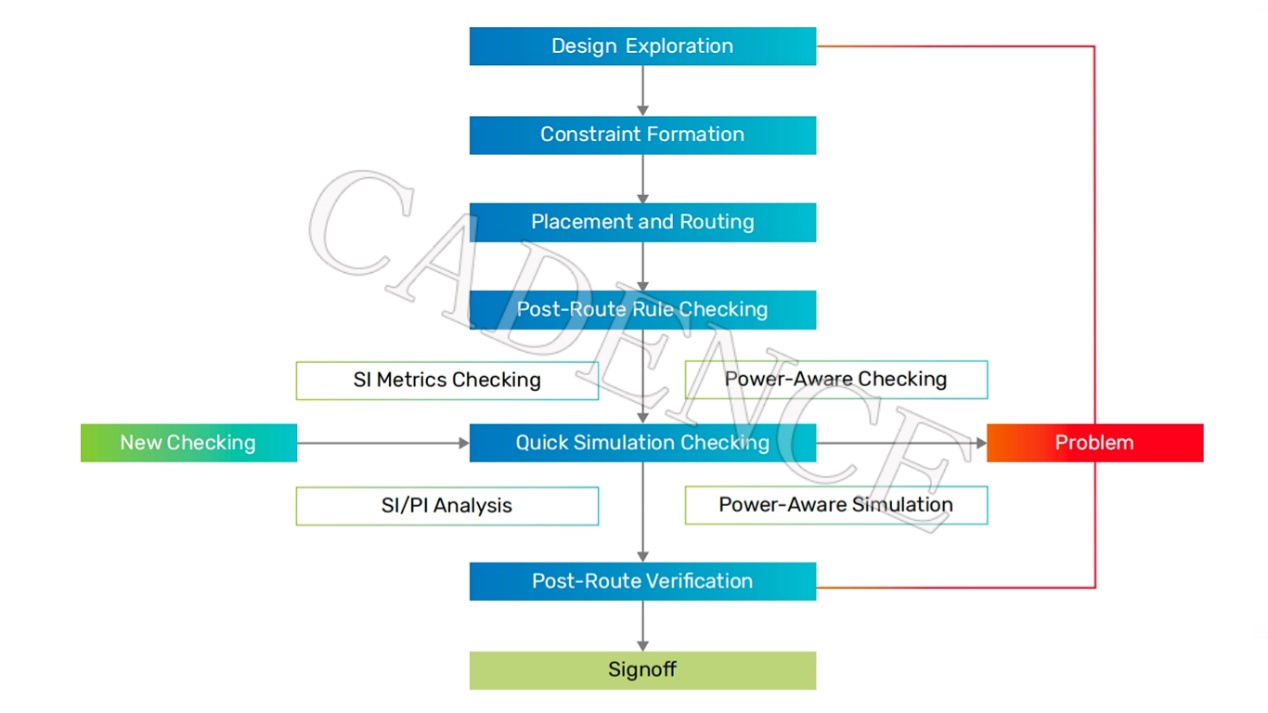

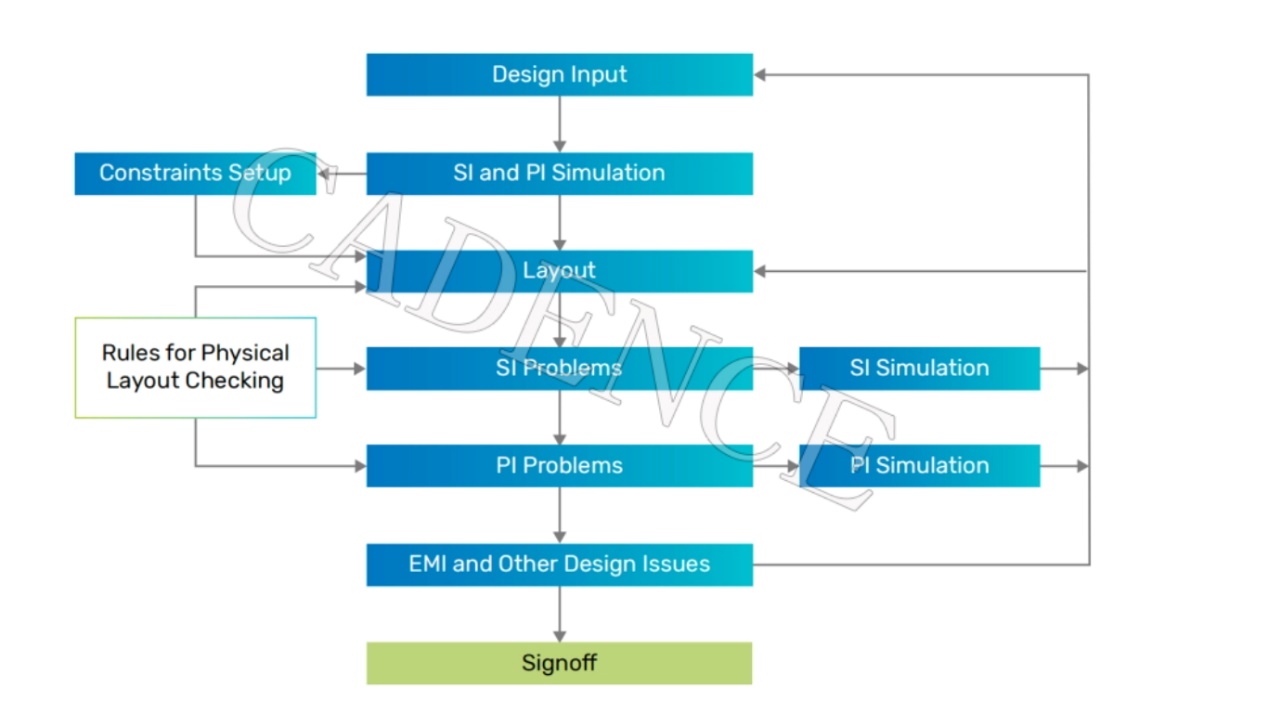

Фигура 3 е процесът на проверка и симулация, който отчита влиянието на захранването, което е в рязък контраст с традиционния процес на проектиране, насочен към ограничения (Фигура 4).Процесът на проектиране на традиционните драйвери за ограничения включва главно четири части: окабеляване преди -проверка на проверката, проверка на правилата и проверка след извършване.

Фигура 3: Каданството взема предвид процеса на ограничаване на двигателя на влиянието на захранването

СРЕЩУ

Фигура 4: Пример за традиционен процес на проектиране на драйвери за ограничаване

Сред многото текущи симулационни технологии често има прекъсвания между анализ на сигнала и мрежа за разпределение на мощността (PDN) и има някои други недостатъци.При нормални обстоятелства, според сложността на модела SPICE, понякога използвайте симулация на времеви домейни, за да генерирате точна модели на съпротивление/индуктивност/кондензатори (RLC), а понякога предполага идеална земна равнина.Моделът във времевата област, получен от това, се основава на простата честотна характеристика на извличането на симулация. Въпреки че е по -удобен, той е леко недостатъчен по отношение на точността. За по -високите честоти инженерите ще използват параметрите на S, създадени от смесено устройство за решаване.

Всъщност има и ефективен метод за комбиниране на метода на ограничената разлика във времето (FDTD) с устройството за смесено решаване, за да се разшири покритието до сигнал, захранване и заземяване.

Успешният случай на практика на този метод е двигателният инструмент на Cadence Sigrity Speed2000. Той интегрира и интегрира изхода на няколко решения за решаване на проводника на веригата, предавателни линии и проблеми с електромагнитното поле и може по -добре да покаже взаимодействието на данните и мощността/наземната равнина при различно пъти.И използвайте метода FDTD, за да анализирате оформлението на IC опаковката и PCB.Той предоставя важна референтна основа за по -нататъшното оптимизиране на дизайна на веригата.

При влизане в крайния етап на подписване, инженерите обикновено са склонни да използват 3D методи за моделиране с пълна вълна, за да получат по -висока точност.Но това ще консумира повече изчислителни ресурси и ще увеличи времето за симулация.За да се облекчи този проблем, може да се приеме технологията за разделяне и паралелизация.В тази връзка, като се използва Clarity 3D Solver за анализ на анализ на крайни елементи (FEM) и след това комбиниране на технологията Sigrity Xtractim, резултатите от всеки анализ се пренасочват, за да образуват параметричен модел въз основа на честотната реакция, като по този начин се постигат CONTE Цяла система за цялата система или в -задължителна и прецизен анализ на дизайна.

Обобщавайте

В същото време като технологичния скок технологията е подобрена и е неизбежно да се поставят нови предизвикателства за дизайнерите.По пътя към паметта на DDR5 и новите предизвикателства, с рязкото "рязко острие" на Cadence Sigrity X, инженерите могат спокойно да се справят със сложните проблеми на целостта на сигнала, като гарантират, че продуктът не само съответства на спецификациите. Той също свети в Изпълнение, добавяне на още една тухла към пътя на бъдещите иновации.