ニュース

DDR5 ERAが近づいており、新しい課題は無視できません

- 著者:ROGER

- 発行::2023-12-04

人工知能(AI)、機械学習(ML)、およびデータマイニングの狂乱では、データ処理に対する私たちの欲求は、前例のないインデックスの成長を示しています。この見通しに直面して、メモリ帯域幅の幅は、デジタル時代の重要な「動脈」になりました。その中で、DDR(ダブルデータレート)テクノロジーは、ダブルデータ伝送レートとダイナミックランダムアクセスメモリ(DRAM)としての帯域幅の高いことで知られており、コンピューターパフォーマンスの改善を大幅に促進しています。2000年の第1世代のDDRテクノロジーの誕生から2020年のDDR5まで、DDRテクノロジーの各世代は、帯域幅、パフォーマンス、消費電力などのさまざまな側面で大幅な改善を達成しました。

今日、それがPC、ラップトップ、人工知能であろうと、さまざまな産業がDDR5の新しい時代に向かって移動するために加速しています。今年、Generation AI市場は活況を呈しており、大規模なモデルアプリケーションで使用されるAIサーバーはDDR5の需要を激しく促進しました。メモリ市場の需要の回復に伴い、メモリチップサプライヤーは、今年の第4四半期にDDR5の生産能力を示して、現在のDDR4を徐々に交換しています。

DDR5の新しい時代が到着しましたが、いくつかの課題が業界のさらなる発展を妨げています。

DDR5 ERA:超高速パフォーマンスの背後にあるデザインの課題

2020年7月、DDR5メモリテクノロジースタンダードが公式にリリースされ、メモリテクノロジーが新しい章を開設したことを示しました。DDR5は、より高い帯域幅とパフォーマンスで広範囲にわたる注目を集めています。以前のDDR4と比較して、DDR5の最大の利点は、消費電力を大幅に削減し、帯域幅を2倍にしたことです。具体的には、DDR5の現在のリリースプロトコルの最高レートが達成されました 6.4Gbpsクロック周波数も1.6GHzから3.2GHzに増加しました。

DDR5の詳細を調査すると、この新しいテクノロジーがいくつかの追加の技術的課題をもたらしたことがわかります。たとえば、DDR5の電源電圧は、DDR4から0.1V緩め、1.1Vに達します。技術的な課題など、技術的な課題など、技術的な課題など、技術的な課題など、技術的な課題など、技術的な課題など、技術的な課題など、技術的な課題など、技術的な課題など、技術的な課題など、技術的な課題など、技術的な課題などの課題などの課題などの課題などの課題などの課題などの課題は、技術的な課題など、ような技術的な課題など、技術的な課題など、技術的な課題などの技術的な課題がいくつかあります。たとえば、電圧間のノイズの量が多いため、シグナルの整合性をより挑戦的にするノイズによって妨害される可能性が高くなります。信号スイッチ中の電圧間は少なくなり、設計に影響を与える可能性があります。

DDR5のもう1つの大きな変化は、DDR4の電源管理チップ(PMIC)がマザーボードに統合される方法とは異なります。DDR5は、マザーボードからデュアルカラムダイレクトメモリモジュール(DIMM)にマザーボードから電源管理IC(PMIC)を転送しました。これにより、モジュール上のストレージデバイスに近い物理に対する電力管理、電圧調整、電力のシーケンスが可能になり、電源の整合性(PI)を確保し、PMIC操作法の制御を強化します。

さらに、データビットの総数が変更されていない場合、1チャネルから2チャネルへのDIMMチャネルの数も重要な進歩です。2つの狭いチャネル伝送にデータを送信することにより、より効果的に生成され、より効果的に生成される可能性があります。信号の完全性を改善するためのクロック信号。

明らかに、DDR5標準の開発も信号の整合性の問題を考慮しており、PMICのモジュールへの転送も対応する利点を発揮します。ただし、設計者は依然として電源の信号整合性の全体的な効果を考慮する必要があります。上記のように、DDR5には最大6.4Gbpsと3.2GHzシステムクロック周波数のデータレートがあります。電源ノイズは、この高い速度操作でより明らかな問題を引き起こす可能性があり、システムのパフォーマンスと安定性に影響します。電力の完全性と信号の完全性が個別に分析されると、電源のノイズの問題が見逃される可能性があります。

したがって、DDR5のパフォーマンスを完全にプレイするために、システムのすべての重要なポイントには、電源の影響の信号整合性分析のためにチップ、パッケージ、PCBを含める必要があります。ただし、このレベルの分析は複雑なタスクです。基礎となるコンピューティングプラットフォームのシミュレーション分析に使用されるハードウェアおよびソフトウェアツールには、高い要件があります。設計の難しさと複雑さ。

DDR5、ケイデンスの可能性を完全に放出します

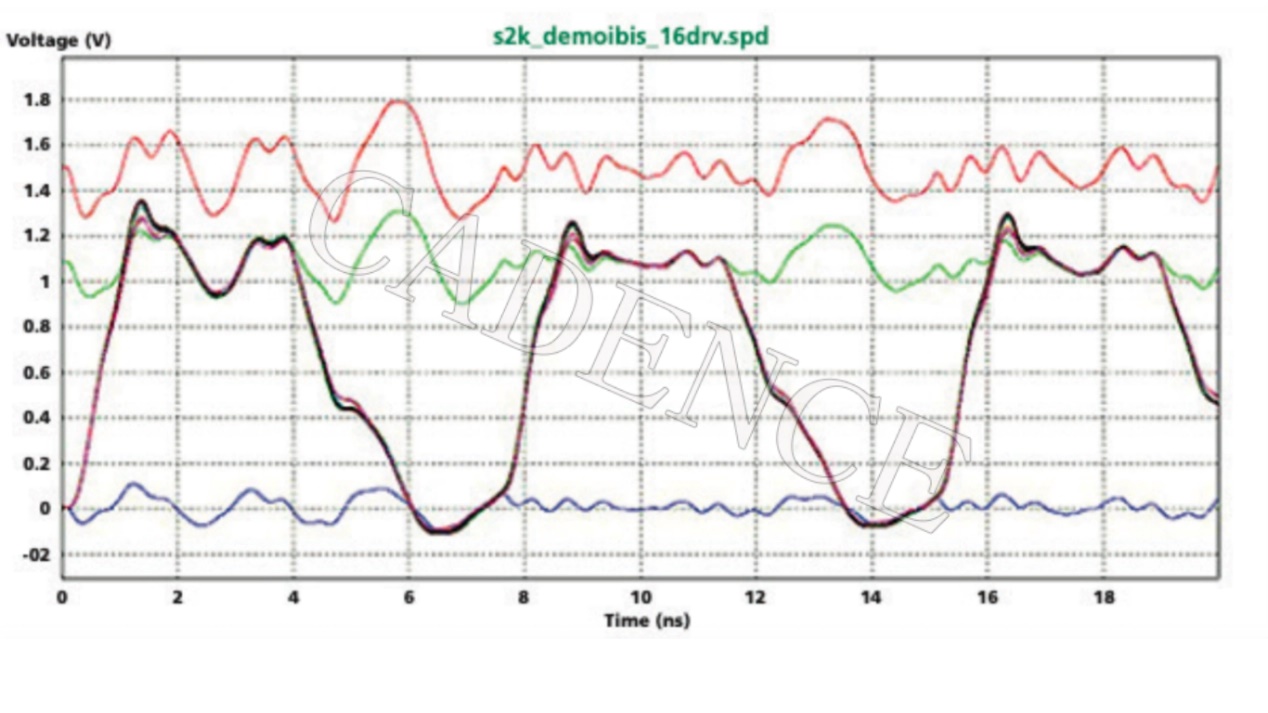

2005年には、「電源の影響を考慮に入れる」という概念は、初めてデビューしました。これは、同時に信号と電力ノイズを分析できる高度な信号整合性シミュレーション方法です(図1)。電源の影響を考慮した信号整合性ソリューションは、反射、ストリング、シーケンシャル、その他の効果を考慮し、対応するシミュレーションおよびルール検査手法を装備する必要があります。電源の影響を考慮した信号整合性シミュレーションを効果的に実装するには、平面と信号の相互作用/カップリングが発生するため、定期的な検査と配線後に分析段階で実行する必要があることに注意してください。配線が完了した後。

したがって、電源の影響を考慮した完全なソリューションは、しばしば提供する必要があります。

l信号の信号減衰と電源のための一連の高速検査ソリューション

Lは、大規模な回路のタイムドメインシミュレーターをシミュレートできます(複数の信号ネットワークと電源ネットワークの結果)

Lパワーネットワークおよび信号ネットワークモデリング

l高レベルの入出力(I/O)バッファモデリング

図1:電源の両方の影響の信号整合性の結果

市場の多くのツールは、電源の影響を考慮した基本的なI/Oモデリング基準をサポートしていますが、メモリインターフェイステクノロジーの継続的な開発により、信号整合性ツールに対する市場の要件も増加しています。 PCBの結合信号、電源、地上信号はまれです。

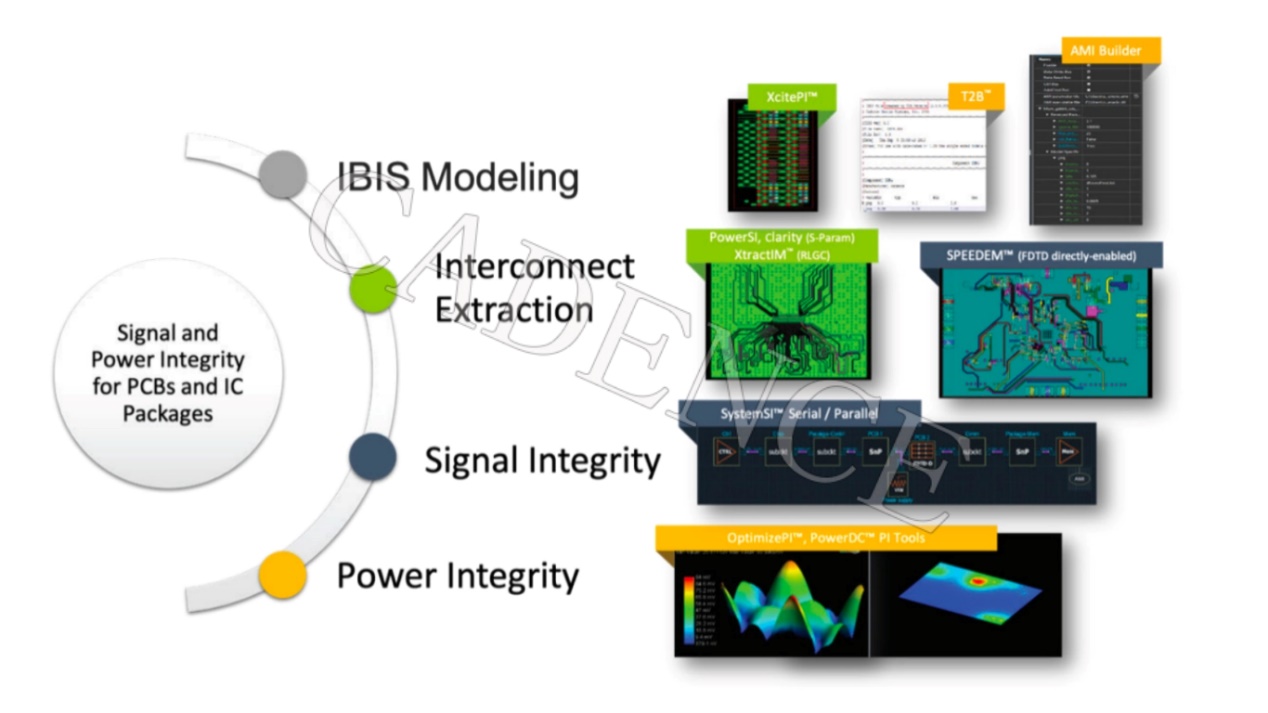

この点で、EDAシミュレーションの分野の主要な企業として、Cadenceによって開始されたSigrity Xテクノロジーは、DDR4およびDDR5の電源の影響に関する信号整合性分析を提供します。

Sigrity Xテクノロジーは、結合信号、チップ、パッケージング、PCBの電源シグナル、接地信号の正確な抽出を実現するだけでなく、反射、損失、帯域、同期スイッチ出力(SSO)効果を同じように効率的にシミュレーションすることもできます。時間。Sigrityテクノロジーを使用する設計者は、トランジスタレベルモデルを迅速に電力の影響を考慮する行動レベルのIBIモデルに迅速に変換できます。元々の元の数字を短縮する必要があります。スカイデザインサイクル。(図2)

図2:PCBおよびICパッケージのためのケイデンス信号の整合性と電力整合性ツール

Sigrity Xテクノロジーは、ワークフローを簡素化し、最終検証のために設計同期シミュレーションと署名レベルの精度を提供します。各設計段階で信号、電源、および熱の問題を解決できるため、設計チームと分析チーム間の反復回数が減少します。設計者は、高精度シミュレーションのために描画布の設計で核レベルのエンジンを実行することができ、それにより分析チームが検証するための高品質の設計を提供できます。その後、分析チームはSigrityの大規模な並列シミュレーションエンジンを使用して、完全なシステムシミュレーションを作成し、「チップパッケージ-PCB-shell」全体が設計仕様を満たし、署名の準備をしていることを確認しました。

これらの利点により、Sigrity XはDDR5メモリと112Gインターフェイスに最適なソリューションになります。そのゴールデン標準の相互接続モデリングは、シリアル/ソリューション(SERDES)分析のタイムドメインシミュレーション(回路とチャネルシミュレーション)を組み合わせて、IBISアルゴリズムモデリングインターフェイス(AMI)をサポートします。完全なソリューション。

さらに、Sigrity XtractimおよびClarity 3Dソルバーテクノロジーを組み合わせて使用できます。これにより、エンジニアは、さまざまなタイプのパッケージのカップリングシグナル、電源、接地の接続モデルを含む完全なパッケージモデルを作成できます。間のギャップ。

さらに、Sigrity Systemsi Technologyは、電源の影響と電源の影響を考慮した相互接続モデルの影響に迅速に接続できるIBISモデルをサポートしています。設計者は、このテクノロジーを通じて最悪の状況を迅速に判断し、それを比較できます。 JEDEC標準DDR4/DDR5インターフェイス(ビットレスコードレート要件を含む)がすべての関連する仕様を満たしていることを確認します。

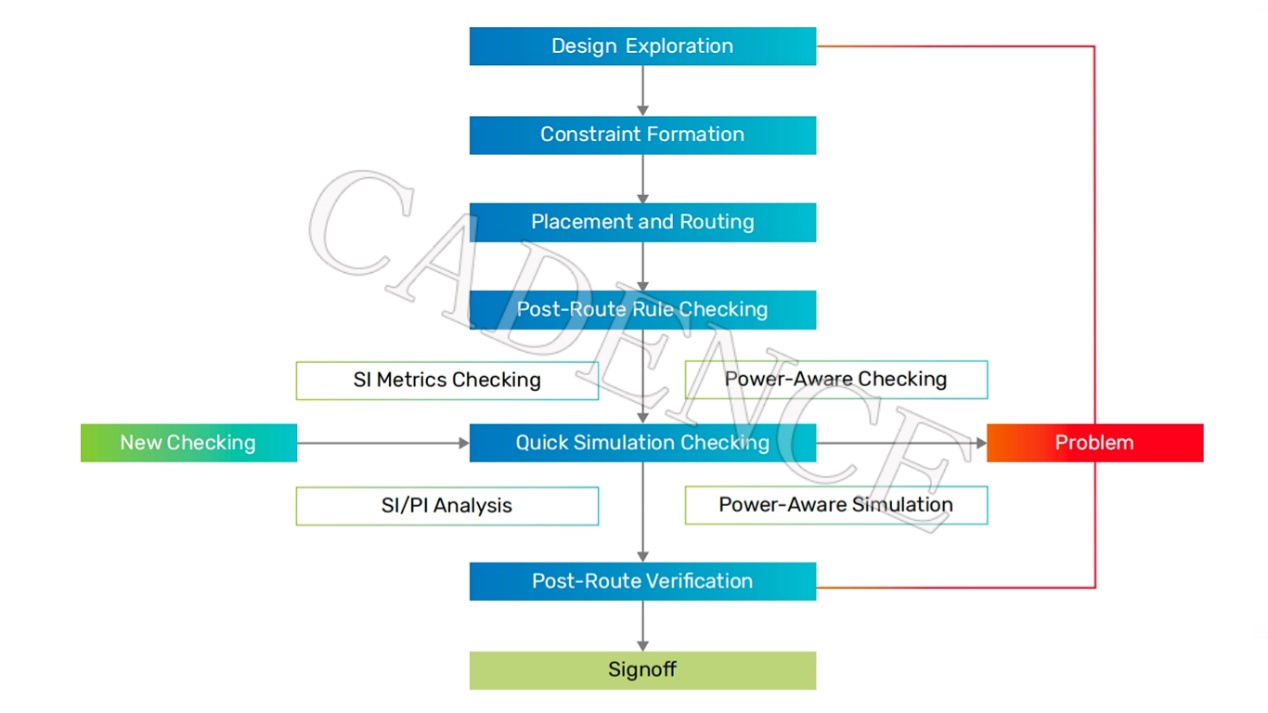

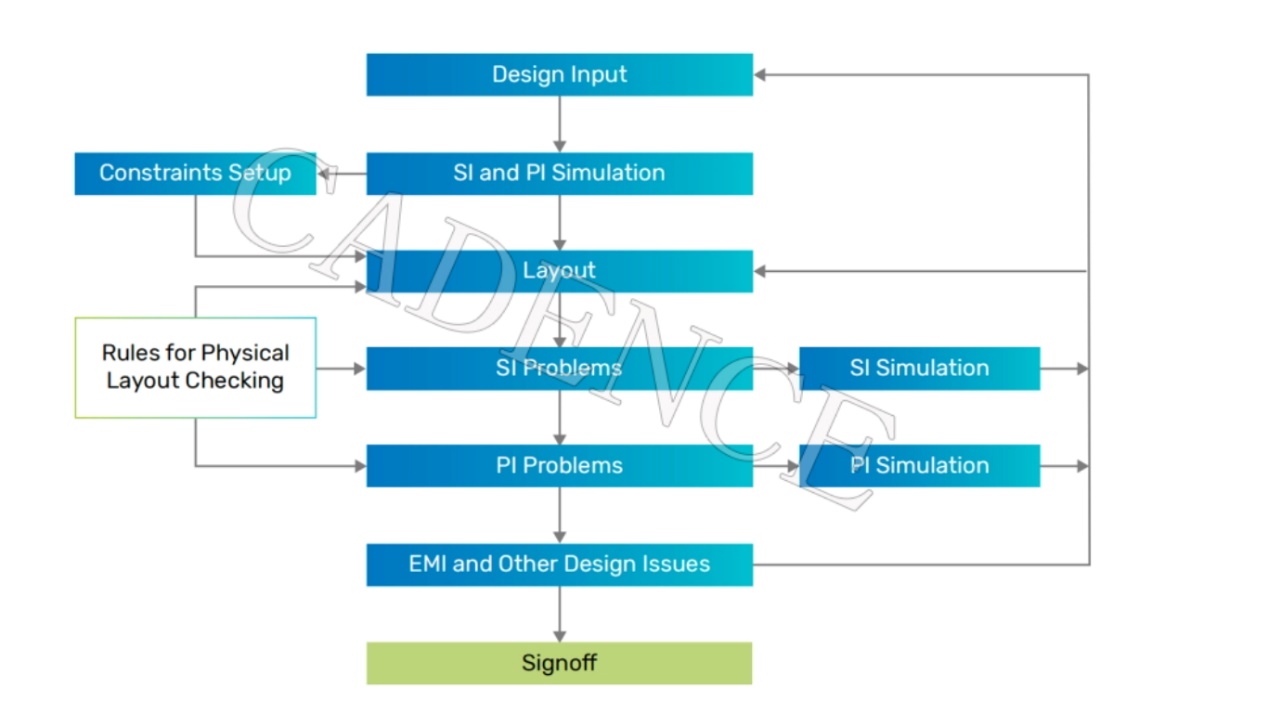

図3は、電源の影響を考慮した検査およびシミュレーションプロセスです。これは、従来の制約駆動型設計プロセスとは対照的です(図4)。従来の制約ドライバーの設計プロセスには、主に4つの部分の4つの部分が含まれています。レイアウト配線、制約形成、規則検査、および配線後の検証です。

図3:ケイデンスは、電源の影響の制約ドライバーのプロセスを考慮しています

vs

図4:従来の制約ドライバー設計プロセスの例

多くの現在のシミュレーションテクノロジーの中には、信号分析と配電ネットワーク(PDN)の間に切断されることが多く、他にも欠点があります。通常の状況では、スパイスモデルの複雑さに応じて、時間ドメインシミュレーションを使用して正確な抵抗/インダクタンス/コンデンサ(RLC)モデルを生成する場合があり、理想的な接地面を想定することもあります。これから得られた時間領域モデルは、シミュレーション抽出の単純な周波数応答に基づいています。より便利ですが、精度の点ではわずかに不十分です。より高い周波数の場合、エンジニアは混合解決装置によって作成されたSパラメーターを使用します。

実際、限られた差分時間ドメイン(FDTD)メソッドと混合解決装置を組み合わせて、カバレッジを信号、電源、接地ラインに拡張する効率的な方法もあります。

この方法の成功した練習ケースは、CadenceのSigrity Speed2000エンジンツールです。いくつかのソリューションの出力を統合および統合して、回路配線、伝送ライン、電磁界の問題を解決し、異なる異なるものでデータと電源/グランドプレーンの相互作用をよりよく表示できます。時代。FDTDメソッドを使用して、ICパッケージとPCBのレイアウトを分析します。回路設計のさらなる最適化のための重要な参照基盤を提供します。

最終的な署名段階に入ると、エンジニアは通常、3Dフル波モデリング方法を使用してより高い精度を得る傾向があります。しかし、これにより、より多くのコンピューティングリソースが消費され、シミュレーション時間が増えます。この問題を軽減するために、分割および並列化技術を採用することができます。この点で、Clarity 3D Solverを有限要素分析(FEM)分析に使用し、Sigrity Xtractimテクノロジーを組み合わせることにより、各分析の結果を再構成して、周波数応答に基づいてSパラメーターモデルを形成し、それにより達成します。システム全体またはシステム全体、または設計の詳細かつ正確な分析。

要約します

技術の飛躍と同時に、技術は改善されており、デザイナーにとって新たな課題を築くことは避けられません。DDR5メモリと新たな課題に向かう途中で、Cadence Sigrity Xの鋭い「シャープブレード」により、エンジニアは信号の完全性の複雑な問題に冷静に対処でき、製品が仕様と一致するだけでなく、輝いています。パフォーマンス、将来のイノベーションの道に別のレンガを追加します。