Nachrichten

Die DDR5 -Ära nähert sich und neue Herausforderungen können nicht ignoriert werden

- Autor:ROGER

- Freigabe auf:2023-12-04

In der Raserei der künstlichen Intelligenz (KI), des maschinellen Lernens (ML) und des Data Mining zeigt unser Wunsch nach Datenverarbeitung ein beispielloses Indexwachstum.Angesichts dieser Aussicht ist die Breite der Speicherbandbreite zu einer wichtigen "Arterien" im digitalen Zeitalter geworden.Unter ihnen hat die DDR -Technologie (Double Data Rate), die für Doppeldatenübertragungsraten und höhere Bandbreite als DRAM (Dynamic Random Access Memory) bekannt ist, die Verbesserung der Computerleistung erheblich gefördert.Von der Geburt der ersten Generation der DDR -Technologie im Jahr 2000 bis zu DDR5 im Jahr 2020 hat jede Generation der DDR -Technologie erhebliche Verbesserungen in verschiedenen Aspekten wie Bandbreite, Leistung und Stromverbrauch erzielt.

Egal, ob es sich um PC-, Laptop- oder künstliche Intelligenz handelt, verschiedene Branchen beschleunigen, um sich in Richtung der neuen Ära von DDR5 zu bewegen.In diesem Jahr boomt der Generations -KI -Markt, und KI -Server, die in großen Modellanwendungen verwendet werden, haben die Nachfrage nach DDR5 energisch gefördert.Mit der Erholung der Nachfrage nach Speichermarkt haben Speicherchip -Lieferanten im vierten Quartal dieses Jahres die Produktionskapazität von DDR5 gezeigt, um den aktuellen DDR4 nach und nach zu ersetzen.

Die neue Ära von DDR5 ist jedoch eingetreten, einige Herausforderungen haben jedoch auch die Weiterentwicklung der Branche behindert.

DDR5 ERA: Designherausforderungen hinter der Leistung von Ultra -Hochgeschwindigkeit

Im Juli 2020 wurde der Standard für DDR5 Memory Technology offiziell veröffentlicht und markiert, dass die Gedächtnistechnologie ein neues Kapitel eröffnete.DDR5 hat mit höherer Bandbreite und Leistung weit verbreitete Aufmerksamkeit erregt.Im Vergleich zum vorherigen DDR4 besteht der größte Vorteil von DDR5 darin, dass es den Stromverbrauch erheblich verringert und die Bandbreite verdoppelt hat.Insbesondere hat die höchste Rate des aktuellen Freisetzungsprotokolls von DDR5 erreicht 6,4 Gbit / sDie Taktfrequenz stieg auch von 1,6 GHz auf 3,2 GHz.

Wenn wir weitere Details von DDR5 untersuchen, stellen wir auch fest, dass diese neue Technologie einige zusätzliche technische Herausforderungen mitgebracht hat.Beispielsweise nimmt die Stromversorgungsspannung von DDR5 um 1,2 V von DDR4 um 0,1 V ab, obwohl die niedrigere Stromversorgungsspannung den Stromverbrauch verringert und die Akkulaufzeit verlängert, aber auch einige technische Herausforderungen, wie z. B. technische Herausforderungen wie technische Herausforderungen wie einige technische Herausforderungen wie einige technische Herausforderungen wie einige technische Herausforderungen wie einige technische Herausforderungen, wie z. Einige technische Herausforderungen, wie z. zwischen der Spannung während des Signalschalters ist geringer und kann das Design beeinflussen.

Eine weitere wichtige Änderung von DDR5 unterscheidet sich von der Art und Weise, wie der Power Management -Chip (PMIC) von DDR4 in das Motherboard integriert ist. DDR5 übertragen das Power Management IC (PMIC) vom Motherboard in das Dual -Column Direct Memory Modul (DIMM).Dies ermöglicht die Stromverwaltung, die Spannungsregulation und die Leistung -die Abfolge von Stromversorgungsanlagen an das Speichergerät des Moduls, wodurch auch die Stromversorgungsintegrität (PI) gewährleistet ist und die Kontrolle der PMIC -Betriebsmethode verbessert.

Wenn die Gesamtzahl der Datenbits unverändert bleibt, ist die Anzahl der DIMM -Kanäle von 1 Kanal auf 2 Kanäle ebenfalls ein wichtiger Fortschritt. Durch die Übertragung von Daten in zwei Schmalkanalübertragungen kann sie effektiver generiert und effektiver zugewiesen werden Taktsignale zur Verbesserung der Signalintegrität.

Offensichtlich hat die Entwicklung des DDR5 -Standards auch das Problem der Signalintegrität berücksichtigt, und die Übertragung von PMIC in das Modul wird auch die entsprechenden Vorteile ausüben.Designer müssen jedoch den Gesamteffekt der Signalintegrität der Stromversorgung weiterhin berücksichtigen.Wie oben erwähnt, hat DDR5 eine Datenrate von bis zu 6,4 Gbit / s und die 3,2 -GHz -Systemtaktfrequenz. Stromrauschen kann in diesem hohen Geschwindigkeitsbetrieb offensichtlichere Probleme verursachen, was die Systemleistung und -stabilität beeinflusst.Wenn die Leistungsintegrität und die Signalintegrität separat analysiert werden, kann das Problem des Rauschens der Netzteil versäumt werden.

Um die Leistung von DDR5 vollständig zu verleihen, müssen alle wichtigen Punkte des Systems Chips, Verpackungen und PCB für die Signalintegritätsanalyse des Einflusses der Stromversorgung enthalten.Die Analyse dieser Ebene ist jedoch eine komplexe Aufgabe. Sie hat hohe Anforderungen für die Hardware- und Softwaretools, die für die Simulationsanalyse für die zugrunde liegende Computerplattform verwendet werden. Die Schwierigkeit und Komplexität des Designs.

Das Potenzial von DDR5, Trittfrequenz vollständig freigeben

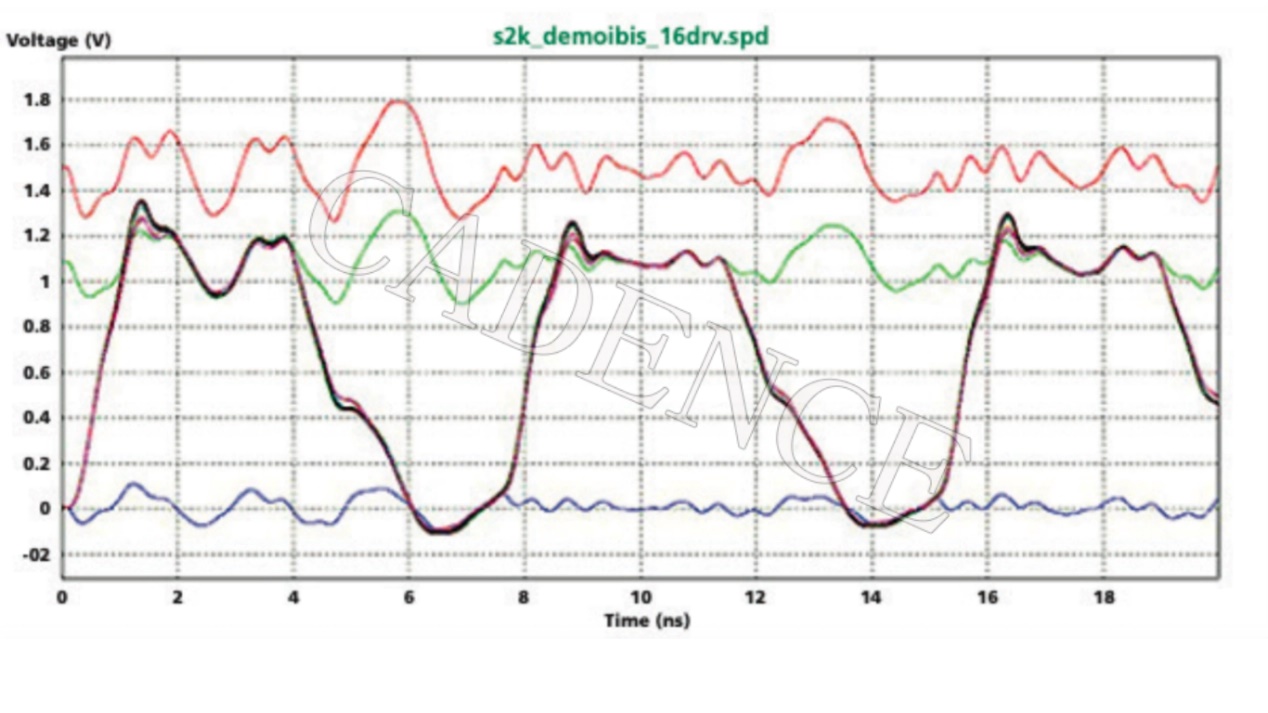

Bereits 2005 debütierte das Konzept "den Einfluss der Stromversorgung" zum ersten Mal. Es handelt sich um eine fortschrittliche Signalintegritätssimulationsmethode, die gleichzeitig Signale und Stromrauschen analysieren kann (Abbildung 1).Die Signalintegritätslösung, die den Einfluss der Stromversorgung berücksichtigt, muss Reflexions-, String-, Sequenti- und andere Effekte berücksichtigen und mit entsprechenden Simulations- und Regelnsinspektionstechniken ausgestattet werden.Es ist erwähnenswert Nach Abschluss der Verkabelung.

Daher muss häufig eine vollständige Lösung berücksichtigt werden, die den Einfluss der Stromversorgung berücksichtigt, häufig bereitgestellt werden:

l Eine Reihe schneller Inspektionslösungen für die Signaldämpfung und die Stromversorgung bei Signalen

L kann den Zeitdomänensimulator großer Schaltungen simulieren (die Ergebnisse mehrerer Signalnetzwerke und Leistungsnetzwerke)

L Leistungsnetzwerk- und Signalnetzwerkmodellierung

l hohe Eingangs-/Ausgangs- (E/O) -Puffermodellierung mit hoher Ebene

Abbildung 1: Das Ergebnis der Signalintegrität sowohl des Einflusses des Netzteils

Obwohl viele Tools auf dem Markt die grundlegenden E/A -Modellierungsstandards unterstützen, die den Einfluss der Stromversorgung berücksichtigen, steigen die Anforderungen des Marktes für die Signalintegritätstools mit der kontinuierlichen Entwicklung der Speicher -Schnittstelle -Technologie. Das genaue Extraktionstool für die Kopplungssignal, Stromversorgung und Bodensignal auf der Leiterplatte sind selten.

In dieser Hinsicht bietet die Sigrity X -Technologie, die von Cadence gestartet wurde, als führende Unternehmen im Bereich der EDA -Simulation eine Signalintegritätsanalyse des Einflusses der Stromversorgung auf DDR4 und DDR5.

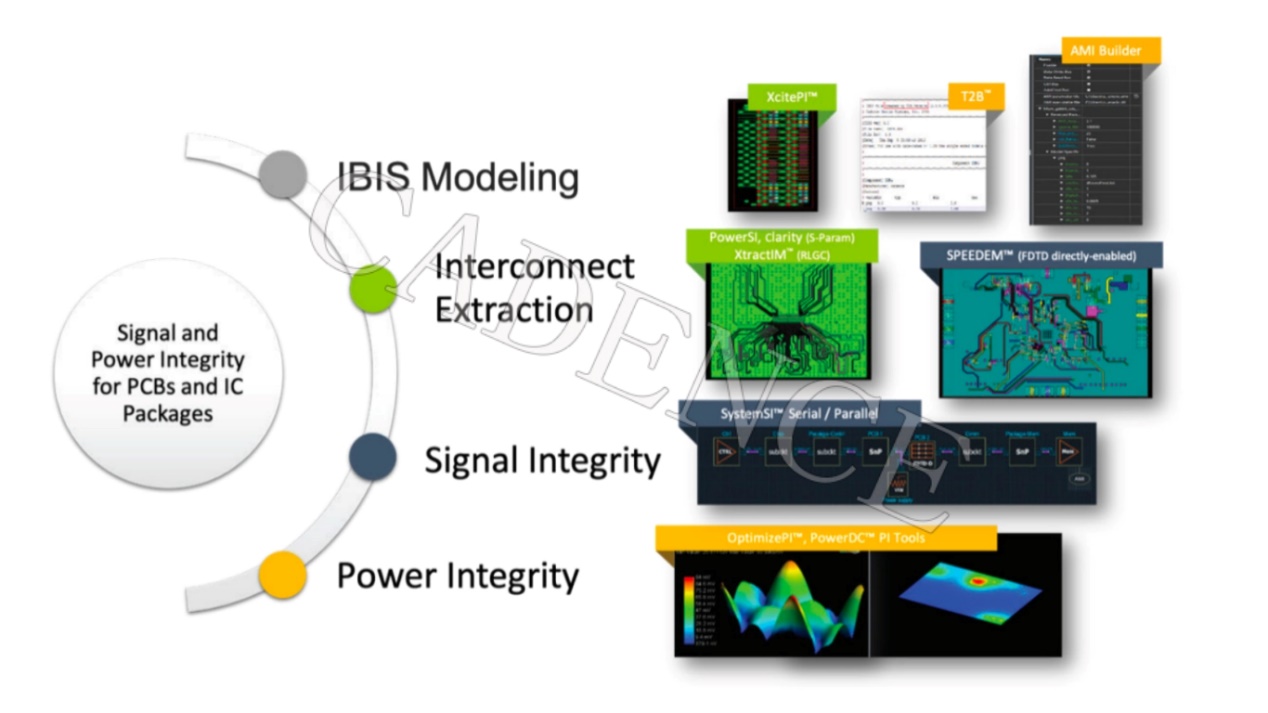

Die Sigrity X -Technologie realisiert nicht nur die genaue Extraktion von gekoppelten Signalen, Stromversorgungs- und Bodensignalen auf Chips, Verpackungen und PCB, sondern kann auch effiziente Simulation bei Reflexion, Verlust, Bandideen und Synchron -Switch -Ausgang (SSO) -Effekten gleichzeitig gleich machen Zeit.Designer, die Sigrity -Technologie verwenden Verkürzen Sie die ursprüngliche Anzahl der ursprünglich nummerierten. Sky Design -Zyklus.(Figur 2)

Abbildung 2: Cadence -Signalintegrität und Stromintegritätstool für PCB- und IC -Verpackungen

Die Sigrity X Technology vereinfacht den Workflow, bietet Designsynchronsimulation und die Genauigkeit der Signierstufe für die endgültige Überprüfung.Signale, Leistung und Wärmeprobleme können in jeder Entwurfsphase gelöst werden, wodurch die Anzahl der Iterationen zwischen den Design- und Analyseteams verringert wird.Designer können den Nuclear -Level -Motor im Design des Zeichenstuchs für die Simulation mit hoher Präzision durchführen und so ein Design von hohem Qualitätsdesign für Analyseteams zur Überprüfung bereitstellen.Später verwendete das Analyse-Team die groß angelegte parallele Simulationsmotor von Sigrity, um die vollständige Systemsimulation zu erstellen, um sicherzustellen, dass die gesamte "Chip-Packaging-PCB-Shell" den Entwurfsspezifikationen erfüllt und sich auf die Unterzeichnung vorbereitet.

Diese Vorteile machen Sigrity X zur besten Lösung für den DDR5 -Speicher und die 112G -Schnittstelle.Die Modellierung der goldenen Standard -Interconnect -Modellierung kombiniert die Zeitdomänensimulation (Schaltung und Kanalsimulation) der seriellen/Lösung (SERDES) -Analyse und unterstützt die IBIS -Algorithmus -Modellierungsschnittstelle (AMI), die Kadenz einzigartige Vorteile bietet, wodurch die Signiervermittlung von Schnittstellen und Schnittstellen für die Signatur der Schnittstelle zur Verfügung stellt vollständige Lösungen.

Darüber hinaus kann die Sigrity Xtractim und Clarity 3D Solver Technology in Verbindung verwendet werden, mit der Ingenieure vollständige Verpackungsmodelle erstellen können Die Lücke zwischen.

Darüber hinaus unterstützt die Sigrity Systemsi -Technologie das IBIS -Modell, das sich schnell mit dem Einfluss der Stromversorgung und des Verbindungsmodells verbinden kann, das den Einfluss der Stromversorgung berücksichtigt. Der Designer kann die schlimmste Situation durch diese Technologie schnell bestimmen und mit dem vergleichen JEDEC Standard, um sicherzustellen, dass DDR4/DDR5 die Schnittstelle (einschließlich der Bitless -Code -Rate -Anforderungen) alle relevanten Spezifikationen erfüllt.

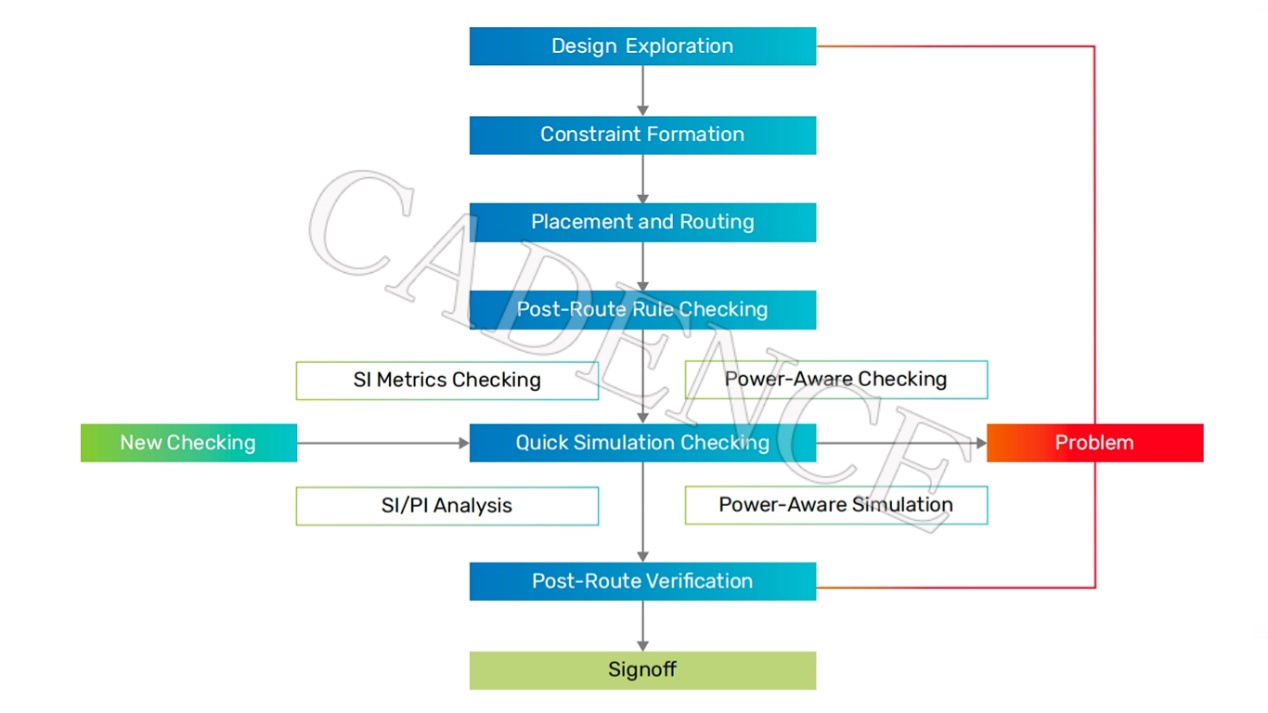

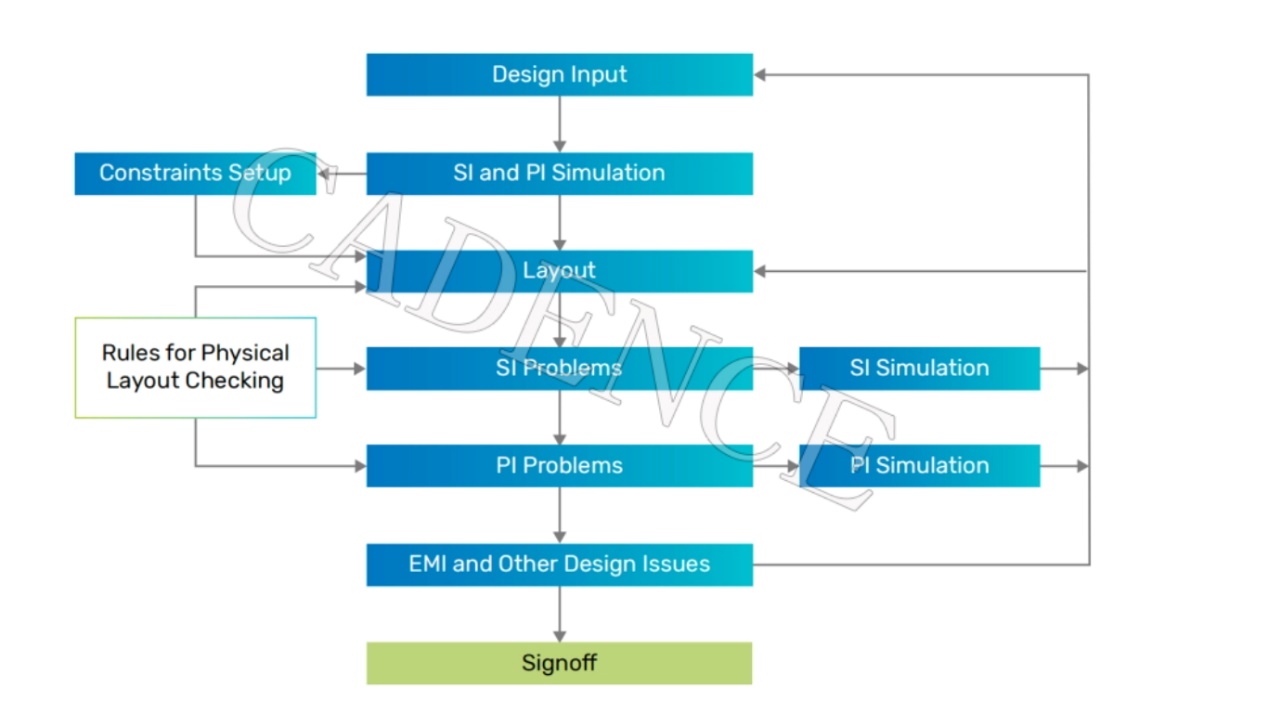

Abbildung 3 ist der Inspektions- und Simulationsprozess, der den Einfluss der Stromversorgung berücksichtigt, der in einem scharfen Kontrast zum traditionellen Einschränkungsprozess steht (Abbildung 4).Der Konstruktionsprozess traditioneller Einschränkungen von Treibern umfasst hauptsächlich vier Teile: Verdrahtung vor dem Layout, die Einschränkung, die Inspektion von Regeln und die Überprüfung der Verdrahtung.

Abbildung 3: Trittfrequenz berücksichtigt den Prozess des Einschränkungstreibers des Einflusses der Stromversorgung

Vs

Abbildung 4: Beispiel für den traditionellen Konstruktionsprozess für Einschränkungen des Treibers

Unter den vielen aktuellen Simulationstechnologien gibt es häufig Unterbrechungen zwischen Signalanalyse und Leistungsverteilungsnetzwerk (PDN), und es gibt einige andere Mängel.Verwenden Sie unter normalen Umständen nach der Komplexität des Gewürzmodells manchmal Zeitdomänensimulation, um genaue Resistenz-/Induktivitäts-/Kondensatoren (RLC) -Modelle (RLC) zu erzeugen, und manchmal wird eine ideale Grundebene angenommen.Das aus diesem Grund erhaltene Zeitdomänenmodell basiert auf dem einfachen Frequenzgang der Simulationsextraktion. Obwohl es bequemer ist, ist es hinsichtlich der Genauigkeit geringfügig unzureichend. Bei höheren Frequenzen verwenden die Ingenieure die S -Parameter, die durch ein gemischtes Lösungsgerät erstellt wurden.

Tatsächlich gibt es auch eine effiziente Methode, um die Methode für begrenzte Differenzzeitdomänen (FDTD) mit dem gemischten Lösungsgerät zu kombinieren, um die Abdeckung auf Signal-, Stromversorgungs- und Erdungslinie zu erweitern.

Der erfolgreiche Praxisfall dieser Methode ist das Sigrity Speed2000 -Motor -Tool von Cadence. Sie integriert und integriert die Ausgabe mehrerer Lösungen, um die Kreisverkabelung, Übertragungsleitungen und elektromagnetische Feldprobleme zu lösen, und kann die Daten- und Leistungs-/Bodenebene -Wechselwirkung bei unterschiedlichem Anteil besser anzeigen mal.Und verwenden Sie die FDTD -Methode, um das Layout von IC -Verpackungen und PCB zu analysieren.Es bietet eine wichtige Referenzbasis für die weitere Optimierung des Schaltungsdesigns.

Beim Eintritt in die endgültige Unterzeichnungsstufe neigen Ingenieure normalerweise dazu, 3D -Modellierungsmethoden mit Voll -Wellen -Modell zu verwenden, um eine höhere Genauigkeit zu erzielen.Dies verbraucht jedoch mehr Computerressourcen und erhöht die Simulationszeit.Um dieses Problem zu lindern, können Teilung und Parallelisierungstechnologie eingesetzt werden.In dieser Hinsicht werden durch die Verwendung des Clarity 3D Solver für eine Finite -Elemente -Analyse (FEM -Analyse) und die Kombination der Sigrity Xtractim -Technologie die Ergebnisse jeder Analyse wieder zusammengefasst, um ein S -Parametermodell basierend auf dem Frequenzgang zu bilden, wodurch das erreicht wird Ganzes System zum gesamten System oder im Depot und eine präzise Analyse des Designs.

Zusammenfassen

Gleichzeitig mit dem technologischen Sprung wurde die Technologie verbessert und es ist unvermeidlich, den Designern neue Herausforderungen zu stellen.Auf dem Weg zum DDR5 -Gedächtnis und neuen Herausforderungen können Ingenieure mit der scharfen "scharfen Klinge" von Cadence Sigrity X die komplexen Probleme der Signalintegrität ruhig bewältigen und sicherstellen, dass das Produkt nicht nur mit den Spezifikationen übereinstimmt. Leistung, fügen Sie dem Weg der zukünftigen Innovation einen weiteren Ziegel zu.