Uutiset

DDR5 -aikakausi on lähestymässä, ja uusia haasteita ei voida sivuuttaa

- kirjailija:ROGER

- Vapauta:2023-12-04

Keinotekoisen älykkyyden (AI), koneoppimisen (ML) ja tiedon louhinnan vimmuudessa tietojenkäsittelyhalu osoittaa ennennäkemättömän hakemiston kasvun.Tämän mahdollisuuden kohdalla muistin kaistanleveydestä on tullut keskeinen "valtimo" digitaaliaikakaudella.Niiden joukossa DDR (kaksinkertainen datanopeus) -tekniikka, joka tunnetaan kaksinkertaisesta tiedonsiirtonopeudesta ja korkeampi kaistanleveys dynaamisena satunnaisena pääsyn muistina (DRAM), on edistänyt huomattavasti tietokoneen suorituskyvyn parantamista.DDR -tekniikan ensimmäisen sukupolven syntymästä vuonna 2000, DDR5: een vuonna 2020, jokainen DDR -tekniikan sukupolvi on saavuttanut merkittäviä parannuksia eri näkökohdissa, kuten kaistanleveys, suorituskyky ja virrankulutus.

Nykyään, olipa kyse sitten PC-, kannettavan tietokoneen tai tekoälyn, eri toimialat kiihtyvät siirtymään kohti DDR5: n uutta aikakautta.Tänä vuonna Generation AI -markkinat kukoistavat, ja suurissa mallisovelluksissa käytetyt AI -palvelimet ovat edistäneet voimakkaasti DDR5: n kysyntää.Muistimarkkinoiden kysynnän palauttamisen myötä muistin sirujen toimittajat ovat osoittaneet DDR5: n tuotantokapasiteetin tämän vuoden viimeisellä neljänneksellä nykyisen DDR4: n korvaamiseksi.

DDR5: n uusi aikakausi on saapunut, mutta jotkut haasteet ovat myös estäneet teollisuuden jatkokehitystä.

DDR5 -aikakausi: Suunnitteluhaasteet Ultra -Korkea -nopeuden suorituskyvyn takana

Heinäkuussa 2020 DDR5 -muistiteknologiastandardi julkaistiin virallisesti, ja se merkitsi kyseistä muistitekniikkaa avasi uuden luvun.DDR5 on herättänyt laajaa huomiota korkeamman kaistanleveyden ja suorituskyvyn kanssa.Verrattuna edelliseen DDR4: ään, DDR5: n suurin etu on, että se on vähentänyt huomattavasti virrankulutusta ja kaksinkertaistanut kaistanleveyden.Erityisesti DDR5: n nykyisen vapautumisprotokollan korkein nopeus on saavuttanut 6,4 gbpsKellotaajuus kasvoi myös 1,6 GHz: stä 3,2 GHz: iin.

Kun tutkimme lisätietoja DDR5: stä, havaitsemme myös, että tämä uusi tekniikka on tuonut joitain muita teknisiä haasteita.Esimerkiksi DDR5: n virtalähteen jännite pienenee 0,1 V: llä 1,2 V: llä DDR4: stä, saavuttaen 1,1 V. Vaikka alempi virtalähteen jännite vähentää virrankulutusta ja pidentää akun käyttöikää, se tuo myös joitain teknisiä haasteita, kuten esimerkiksi tekninen Haasteet, kuten esimerkiksi tekniset haasteet, kuten jotkut tekniset haasteet, kuten jotkut tekniset haasteet, kuten jotkut tekniset haasteet, kuten jotkut tekniset haasteet, kuten esimerkiksi, kuten esimerkiksi Jotkut tekniset haasteet, kuten esimerkiksi tekniset haasteet, kuten jotkut tekniset haasteet. Esimerkiksi melu häiritsee todennäköisemmin, mikä tekee signaalin eheydestä haastavamman, koska jännitteen välinen melu Jännitteen välillä signaalikytkimen aikana on vähemmän ja voi vaikuttaa suunnitteluun.

Toinen suuri DDR5: n muutos on erilainen kuin DDR4: n virranhallintapiiri (PMIC) emolevyssä. DDR5 siirsi virranhallinnan IC (PMIC) emolevystä kaksikerroksiseen suoran muistimoduuliin (DIMM).Tämä mahdollistaa virranhallinnan, jännitteen säätelyn ja tehon sekvenssin fyysiseen lähemmäksi moduulin tallennuslaitetta, mikä myös auttaa varmistamaan virtalähteen eheyden (PI) ja parantaa PMIC -operaatiomenetelmän hallintaa.

Lisäksi, kun databittien kokonaismäärä pysyy muuttumattomana, DIMM -kanavien lukumäärä 1 kanavasta 2 kanavaan on myös tärkeä edistyminen. Lähettämällä tiedot kahteen kapeaan kanavan lähetykseen, se voidaan luoda tehokkaammin ja luoda tehokkaammin määritetään tehokkaammin Kellosignaalit signaalin eheyden parantamiseksi.

On selvää, että DDR5 -standardin kehitys on myös ottanut huomioon signaalin eheysongelman, ja PMIC: n siirto moduuliin myös vastaa vastaavia etuja.Suunnittelijoiden on kuitenkin vielä otettava huomioon virtalähteen signaalin eheyden kokonaisvaikutus.Kuten edellä mainittiin, DDR5: n tiedonsiirtonopeus on enintään 6,4 Gbps ja 3,2 GHz: n järjestelmän kellotaajuus. Tehon melu voi aiheuttaa selvempiä ongelmia tässä suuressa nopeudessa, mikä vaikuttaa järjestelmän suorituskykyyn ja vakauteen.Jos tehon eheys ja signaalin eheys analysoidaan erikseen, virtalähteen melun ongelma voidaan jättää väliin.

Siksi DDR5: n suorituskyvyn täydellisen pelaamisen, järjestelmän kaikkien avainkohtien on sisällettävä sirut, pakkaukset ja piirilevy signaalin eheysanalyysiin virtalähteen vaikutuksesta.Tämän tason analyysi on kuitenkin monimutkainen tehtävä. Sillä on korkeat vaatimukset laitteisto- ja ohjelmistotyökaluille, joita käytetään taustalla olevan laskentaalustan simulaatioanalyysiin. Suunnittelun vaikeus ja monimutkaisuus.

Vapauta täysin DDR5: n, poljinnopeuden potentiaali

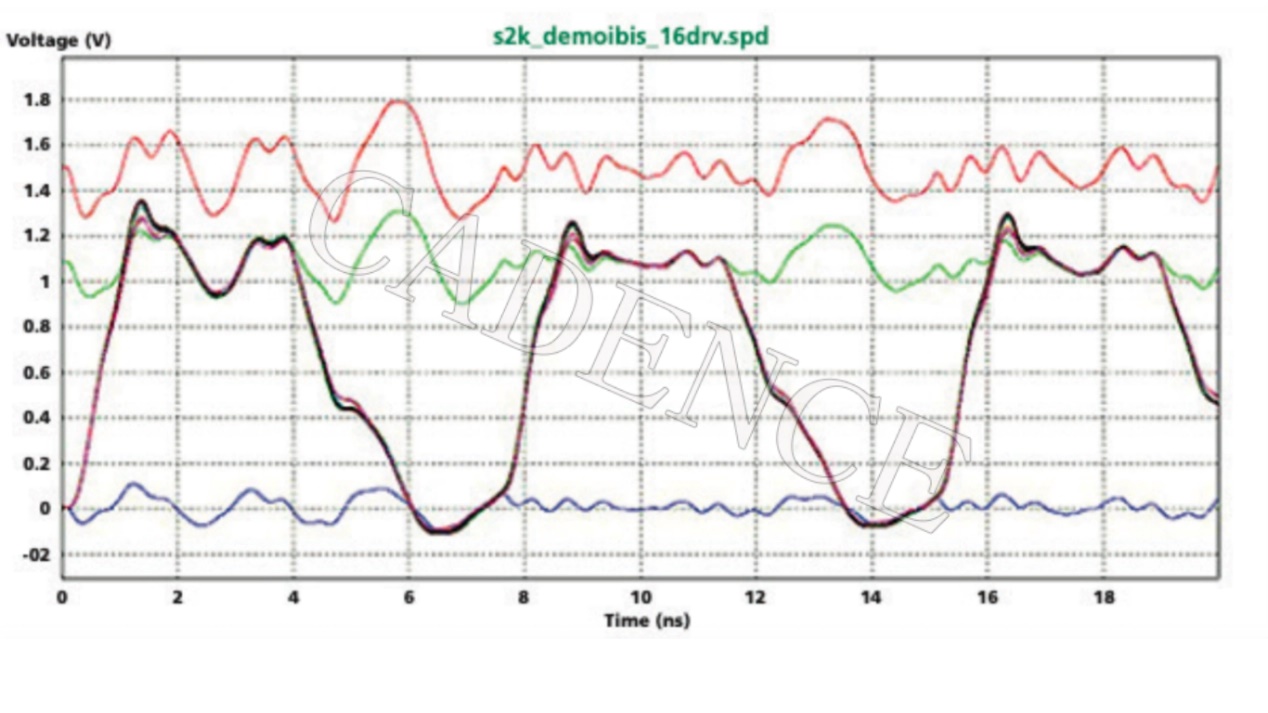

Jo vuonna 2005 käsite "Virtalähteen vaikutuksen huomioon ottaminen" debytoi ensimmäistä kertaa. Se on edistynyt signaalin eheyden simulointimenetelmä, joka voi analysoida signaaleja ja tehonmelua samanaikaisesti (kuva 1).Signaalin eheysratkaisussa, jossa otetaan huomioon virtalähteen vaikutukset, on harkittava heijastusta, merkkijonoa, peräkkäisiä ja muita vaikutuksia ja varustettu vastaavilla simulaatioilla ja sääntöjen tarkastustekniikoilla.On syytä huomata, että signaalin eheyden simulaation tehokkaaseen toteuttamiseksi, jossa otetaan huomioon virtalähteen vaikutukset, on välttämätöntä suorittaa analyysivaiheessa säännöllisen tarkastuksen ja johdotuksen jälkeen, koska tason vuorovaikutus/kytkentä ja signaali tapahtuu Kun johdotus on valmis.

Siksi on tarjottava täydellinen ratkaisu, jossa otetaan huomioon virtalähteen vaikutus:

l Signaalin vaimenemisen ja virtalähteen nopeat tarkastusratkaisut signaaleilla

L voi simuloida suurten piirien aika -alueen simulaattoria (useiden signaaliverkkojen ja tehoverkkojen tulokset)

L Power Network- ja signaaliverkon mallinnus

l Korkea -tason tulo/lähtö (I/O) puskurin mallintaminen

Kuva 1: Virtalähteen vaikutuksen signaalin eheyden tulos

Vaikka monet markkinoiden työkalut tukevat I/O Kytkentäsignaali, virtalähde ja maadoitussignaali PCB: llä on harvinaista.

Tältä osin johtavana yrityksenä EDA -simulaation alalla Sighty X -teknologia on Cadenssilla käynnistänyt signaalin eheysanalyysi DDR4: n ja DDR5: n virtalähteen vaikutuksesta.

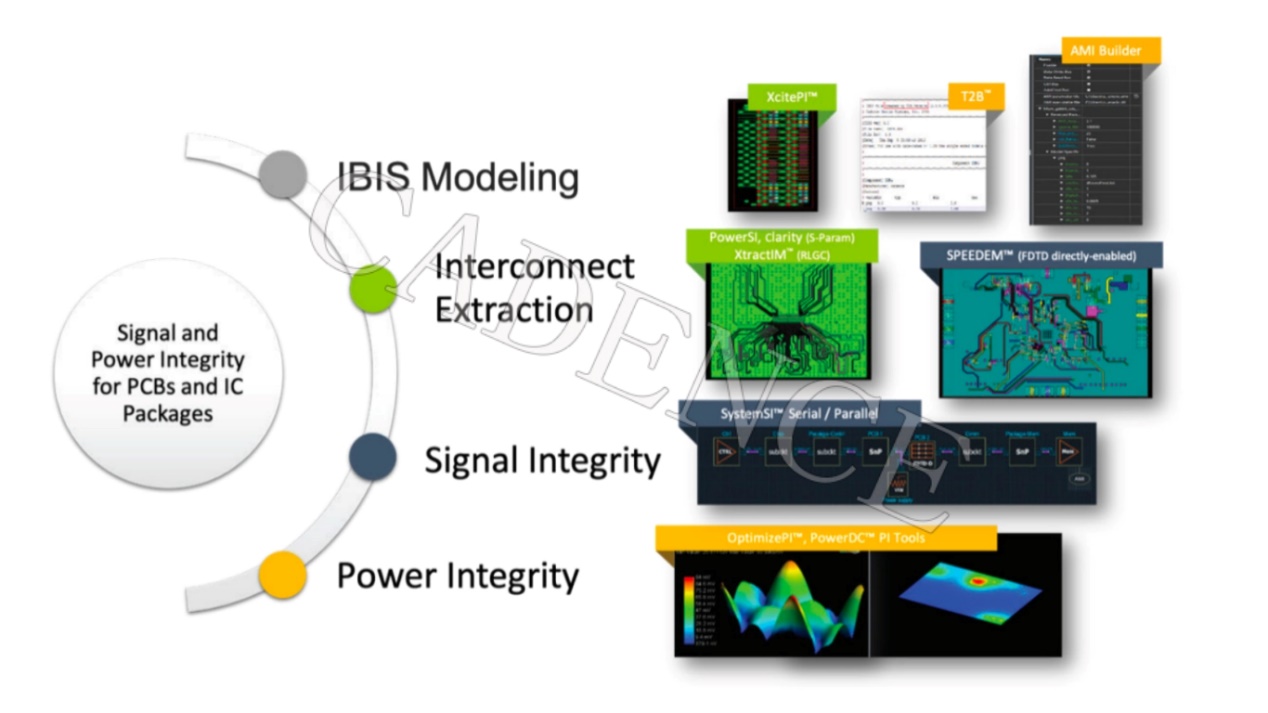

SIGRITY X -tekniikka ei vain ymmärrä kerrostettujen signaalien, virtalähteen ja maaserkkien tarkkaa uuttamista siruihin, pakkauksiin ja piirilevyihin, mutta voi myös tehdä tehokasta simulointia heijastus-, häviö-, bandidal- ja synkronisen kytkentälähtöjen (SSO) vaikutuksissa samalla tavalla kuin samalla tavalla aika.Sighty -tekniikkaa käyttävät suunnittelijat voivat nopeasti muuntaa transistorin -tason mallin käyttäytymistason IBIS -malliksi, joka harkitsee vallan vaikutusta, joten muutaman tunnin sisällä se voi tarjota tarkan, tehokkaan ja kattavan ottaen huomioon virransyöttövaikutusten simulointi, joka suuresti lyhentää alkuperäistä alun perin lukumäärää. Sky Design -sykli.(Kuva 2)

Kuva 2: Pecb- ja IC -pakkauksen polvenssisignaalin eheys ja tehon eheystyökalu

Sigrity X -tekniikka yksinkertaistaa työnkulkua, tarjoaa suunnittelun synkronisen simulaation ja allekirjoittamisen tarkkuuden lopulliseen varmennukseen.Signaalit, voima- ja lämpöongelmat voidaan ratkaista jokaisessa suunnitteluvaiheessa, mikä vähentää suunnittelu- ja analyysiryhmien välillä olevien iteraatioiden lukumäärää.Suunnittelijat voivat suorittaa ydintason moottorin piirustuskankaan suunnittelussa korkean tarkistuksen simulaatioon, tarjoamalla siten korkealaatuisen suunnittelun analysointiryhmille.Myöhemmin analyysiryhmä käytti Sighty-järjestelmän laajamittaista rinnakkaisimulaatiomoottoria täydellisen järjestelmän simulaation tekemiseen varmistaakseen, että koko "sirupakkaus-PCB-kuori" täyttää suunnittelumääritykset ja valmistautuu allekirjoitukseen.

Nämä edut tekevät Sighty X: stä parhaan ratkaisun DDR5 -muistiin ja 112G -rajapinnalle.Sen kultainen standardiyhteysmallinnus yhdistää sarja-/ratkaisuanalyysin (SerDES) analyysin aika -alueen simulaation (piirin ja kanavan simulointi) ja IBIS -algoritmin mallinnusliittymän (AMI) tukemisen, joka antaa kadenssin ainutlaatuisia etuja, siten voi purkaa ja rajapinnan noudattamisen allekirjoittamisen Täydelliset ratkaisut.

Lisäksi Sighity Xtractim- ja Clarity 3D Solver -tekniikkaa voidaan käyttää yhdessä, mikä antaa insinöörien luoda täydellisiä pakkausmalleja, jotka sisältävät kytkentäsignaaleja, virtalähdettä ja maadoitusyhteysmalleja erityyppisille pakkauksille, jotka korvaavat tehokkaasti pakkaussuunnittelun ja pakettiominaisuudet Aukko välillä.

Lisäksi SIGRITY SystemsI -tekniikka tukee IBIS -mallia, joka voi nopeasti muodostaa yhteyden virtalähteen vaikutukseen, ja yhdistämismalliin, jossa otetaan huomioon virtalähteen vaikutukset. Suunnittelija voi nopeasti määrittää pahimman tilanteen tämän tekniikan kautta ja verrata sitä kanssa JEDEC -standardi varmistaakseen, että DDR4/DDR5 -rajapinta (mukaan lukien Bitless -koodinopeusvaatimukset) täyttää kaikki asiaankuuluvat eritelmät.

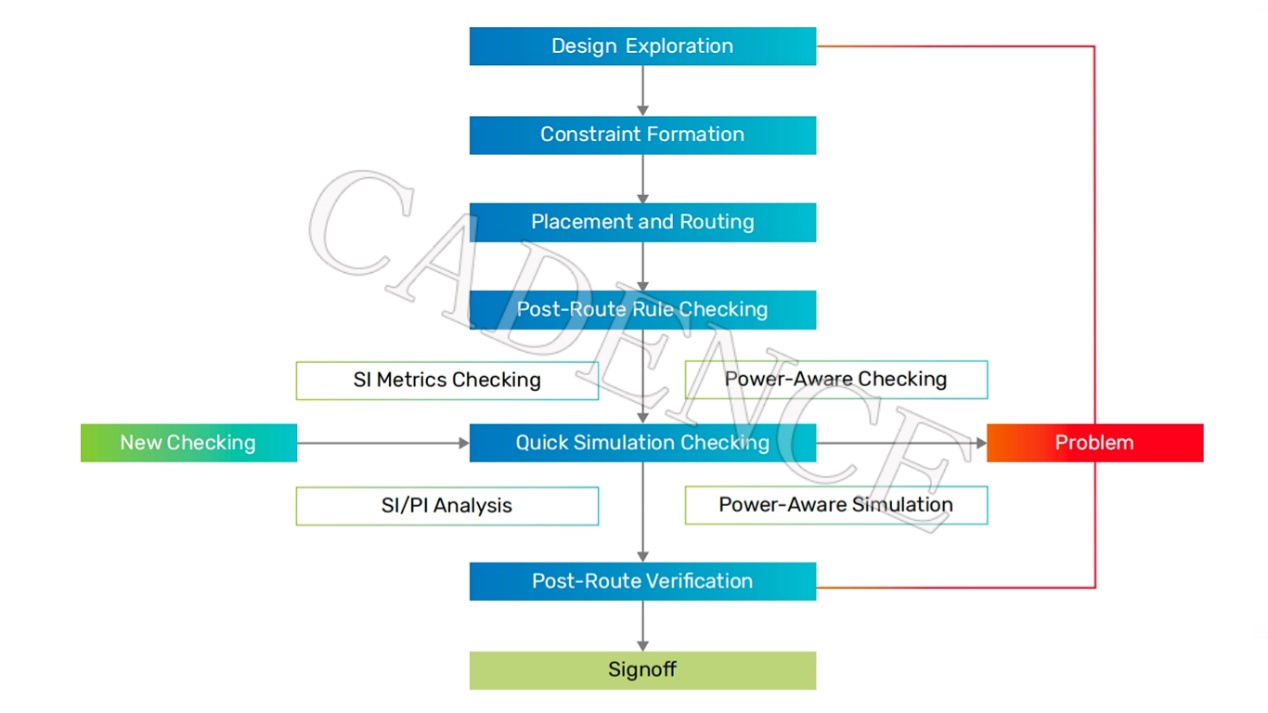

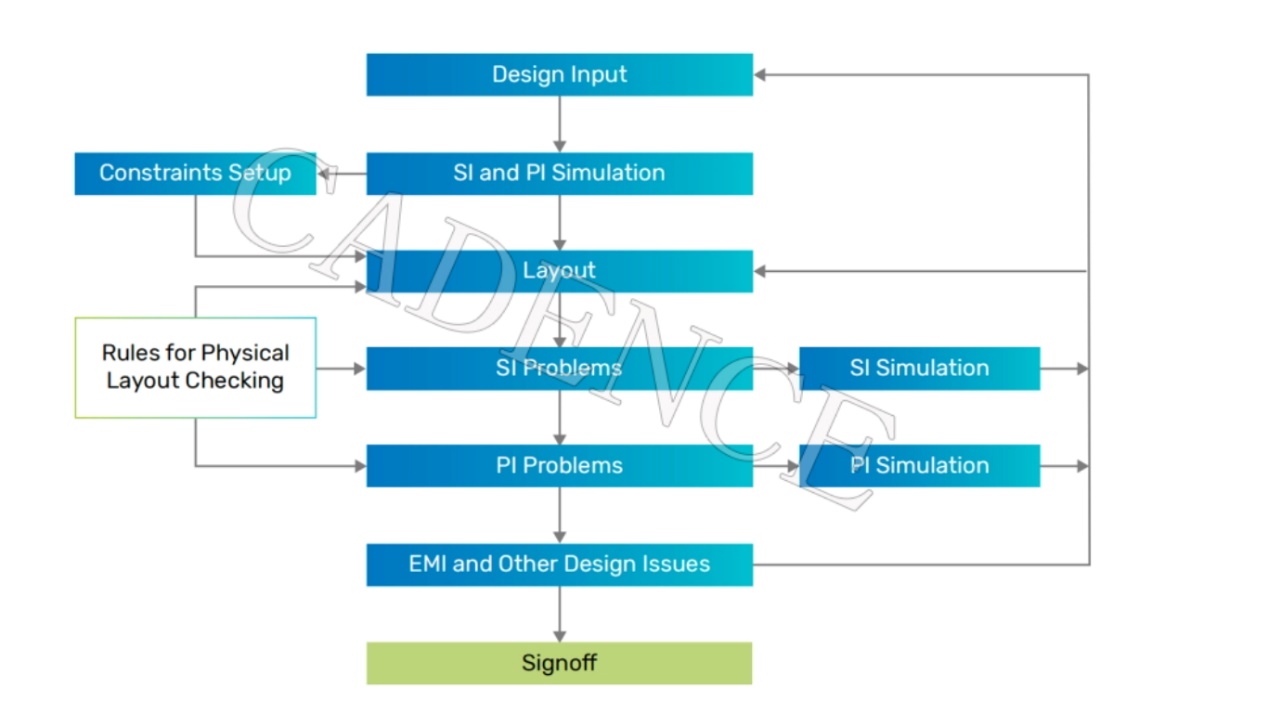

Kuvio 3 on tarkastus- ja simulaatioprosessi, joka ottaa huomioon virtalähteen vaikutuksen, joka on terävä vastakohta perinteiseen rajoitusohjattuun suunnitteluprosessiin (kuva 4).Perinteisten rajoitusten ohjaimien suunnitteluprosessi sisältää pääasiassa neljä osaa: Pre -tavan johdotus, rajoitusten muodostuminen, sääntöjen tarkastus ja johdotuksen jälkeinen varmennus.

Kuva 3: Cadence ottaa huomioon virtalähteen vaikutuksen rajoitusohjaimen prosessin

Vs.

Kuva 4: Esimerkki perinteisestä ohjaimen suunnitteluprosessista

Monien nykyisten simulaatioteknologioiden joukossa signaalianalyysin ja tehonjakeluverkon (PDN) välillä on usein irrotettu yhteys, ja on joitain muita puutteita.Normaaliolosuhteissa maustemallin monimutkaisuuden mukaan käytä joskus aikataulu -simulointia tarkan resistenssin/induktanssi-/kondensaattorien (RLC) mallien tuottamiseksi ja joskus se edellyttää ihanteellisen maatason.Tästä saatu aika -alueen malli perustuu simulaation uuttamisen yksinkertaiseen taajuusvasteeseen. Vaikka se on helpompaa, se ei ole hiukan riittämätön tarkkuuden suhteen. Korkeammille taajuuksille insinöörit käyttävät Sekoitetun ratkaisulaitteen luomia S -parametreja.

Itse asiassa on myös tehokas menetelmä yhdistää rajoitetun eron aika -domeenin (FDTD) menetelmä sekoitettuun ratkaisulaitteeseen kattavuuden laajentamiseksi signaaliin, virtalähteeseen ja maadoituslinjaan.

Tämän menetelmän onnistunut käytäntötapaus on Cadence's Sighty Speed2000 -moottorityökalu. Se integroi ja integroi useiden ratkaisujen lähdön piirin johdotuksen, voimansiirtoviivojen ja sähkömagneettisten kenttäongelmien ratkaisemiseksi ja voi paremmin näyttää datan ja tehon/maantason vuorovaikutuksen eri tavalla ajat.Ja käytä FDTD -menetelmää IC -pakkauksen ja piirilevyn asettelun analysointiin.Se tarjoaa tärkeän vertailun piirin suunnittelun lisäoptimoinnille.

Kun siirryt lopulliseen allekirjoitusvaiheeseen, insinöörit yleensä yleensä käyttävät 3D -täysaaltomallinnusmenetelmiä suuremman tarkkuuden saavuttamiseksi.Mutta tämä kuluttaa enemmän laskentaresursseja ja lisää simulaatioaikaa.Tämän ongelman lievittämiseksi voidaan ottaa käyttöön jako- ja rinnakkaistekniikka.Tältä osin käyttämällä selkeyttä 3D -ratkaisijaa äärellisen elementtianalyysianalyysiin (FEM) ja yhdistämällä sitten Sighity Xtractim -tekniikka, kunkin analyysin tulokset yhdistetään uudelleen S -parametrimallin muodostamiseksi taajuusvasteen perusteella, siten saavuttaa Koko järjestelmä koko järjestelmään tai suunnitteluun ja tarkka analyysi.

Tehdä yhteenveto

Samanaikaisesti tekniikkaa tekniikkaa on parantunut, ja on väistämätöntä asettaa uusia haasteita suunnittelijoille.Matkalla kohti DDR5 -muistia ja uusia haasteita kadenssien Sighty X: n terävällä "terävällä terällä", insinöörit voivat rauhallisesti selviytyä signaalin eheyden monimutkaisista kysymyksistä varmistaen, että tuote ei ole vain yhdenmukainen eritelmien kanssa. Se myös loistaa sisään Suorituskyky, lisäämällä uuden tiilen tulevaisuuden innovaatioiden tielle.