Zprávy

ERA DDR5 se blíží a nové výzvy nelze ignorovat

- Autor:ROGER

- Uvolněte:2023-12-04

Ve šílenství umělé inteligence (AI), strojového učení (ML) a dolování dat ukazuje naše touha po zpracování dat bezprecedentní růst indexu.Tváří v tvář této perspektivě se šířka šířky pásma paměti stala klíčovým „tepnami“ v digitálním věku.Mezi nimi technologie DDR (dvojitá datová rychlost), známá rychlostí dvojitého přenosu dat a vyšší šířkou pásma jako dynamická paměť s náhodným přístupem (DRAM), výrazně podporovala zlepšení výkonu počítače.Od narození první generace technologie DDR v roce 2000 až po DDR5 v roce 2020 dosáhla každá generace technologie DDR významná zlepšení v různých aspektech, jako je šířka pásma, výkon a spotřeba energie.

Ať už se jedná o PC, notebook nebo umělá inteligence, různá průmyslová odvětví se zrychlují, aby se posunuly směrem k nové éře DDR5.Letos se generační trh AI rozvíjí a servery AI používané ve velkých modelových aplikacích důrazně podporovaly poptávku po DDR5.Při obnově poptávky po trhu s pamětí dodavatelé paměťových čipů ukázali výrobní kapacitu DDR5 ve čtvrtém čtvrtletí letošního roku, aby postupně nahradili současný DDR4.

Nová éra DDR5 však přišla, některé výzvy však také bránily dalšímu rozvoji odvětví.

ERA DDR5: Výzvy designu za ultra -vysokým výkonem

V červenci 2020 byl oficiálně uvolněn standard technologie paměti DDR5 a označil, že technologie paměti otevřela novou kapitolu.DDR5 přitahoval rozsáhlou pozornost s vyšší šířkou pásma a výkonem.Ve srovnání s předchozím DDR4 je největší výhodou DDR5, že výrazně snížila spotřebu energie a zdvojnásobila šířku pásma.Konkrétně dosáhla nejvyšší míry současného vydání DDR5 6,4 GbpsHodinová frekvence se také zvýšila z 1,6 GHz na 3,2 GHz.

Když prozkoumáme více podrobností o DDR5, také zjistíme, že tato nová technologie přinesla některé další technické výzvy.Například napájecí napětí DDR5 se z DDR4 snižuje o 0,1 V o 1,2 V, dosahuje 1,1 V. Ačkoli nižší napájecí napětí snižuje spotřebu energie a prodlužuje životnost baterie, přináší také některé technické výzvy, jako je například technické výzvy Výzvy, například technické výzvy, jako jsou některé technické výzvy, jako jsou některé technické výzvy, jako jsou některé technické výzvy, jako jsou některé technické výzvy Některé technické výzvy, jako jsou technické výzvy, jako jsou například některé technické výzvy. Například je pravděpodobnější, že bude narušen hlukem, což zvyšuje náročnou integritu signálu, protože množství hluku mezi napětím Mezi napětím během spínače signálu je menší a může ovlivnit konstrukci.

Další významná změna DDR5 se liší od způsobu, jakým je čip pro správu energie (PMIC) DDR4 integrován na základní desce. DDR5 přenesl IC pro správu napájení (PMIC) ze základní desky na modul přímé paměti s dvojitou Column (DIMM).To umožňuje správu napájení, regulaci napětí a sekvence napájení na fyzické blížící se úložnému zařízení na modulu, což také pomáhá zajistit integritu napájení (PI) a zlepšit řízení metody operace PMIC.

Navíc, když celkový počet datových bitů zůstává nezměněn, je důležitým pokrokem také počet kanálů DIMM z 1 kanálu na 2 kanály. Přenosem dat do dvou úzkých přenosu kanálů může být efektivněji generován a generován efektivněji přiřazen Hodinové signály pro zlepšení integrity signálu.

Je zřejmé, že vývoj standardu DDR5 také zohlednil problém integrity signálu a přenos PMIC do modulu také vyvíjí odpovídající výhody.Návrháři však stále musí zvážit celkový účinek integrity signálu napájení.Jak je uvedeno výše, DDR5 má datovou rychlost až 6,4 Gbps a frekvence systémových hodin 3,2 GHz. Šmeta výkonu může způsobit zjevnější problémy v této operaci s vysokou rychlostí, což ovlivní výkon a stabilitu systému.Pokud jsou integrita výkonu a integrita signálu analyzována samostatně, může být problém hluku napájecího zdroje vynechán.

Aby se tedy všechny klíčové body systému daly plné hře na výkon DDR5, musí zahrnovat čipy, balení a PCB pro analýzu integrity signálu vlivu napájení.Analýza této úrovně je však komplexní úkol. Má vysoké požadavky na hardwarové a softwarové nástroje používané pro simulační analýzu pro základní výpočetní platformu. Obtížnost a složitost designu.

Plně uvolněte potenciál DDR5, kadenci

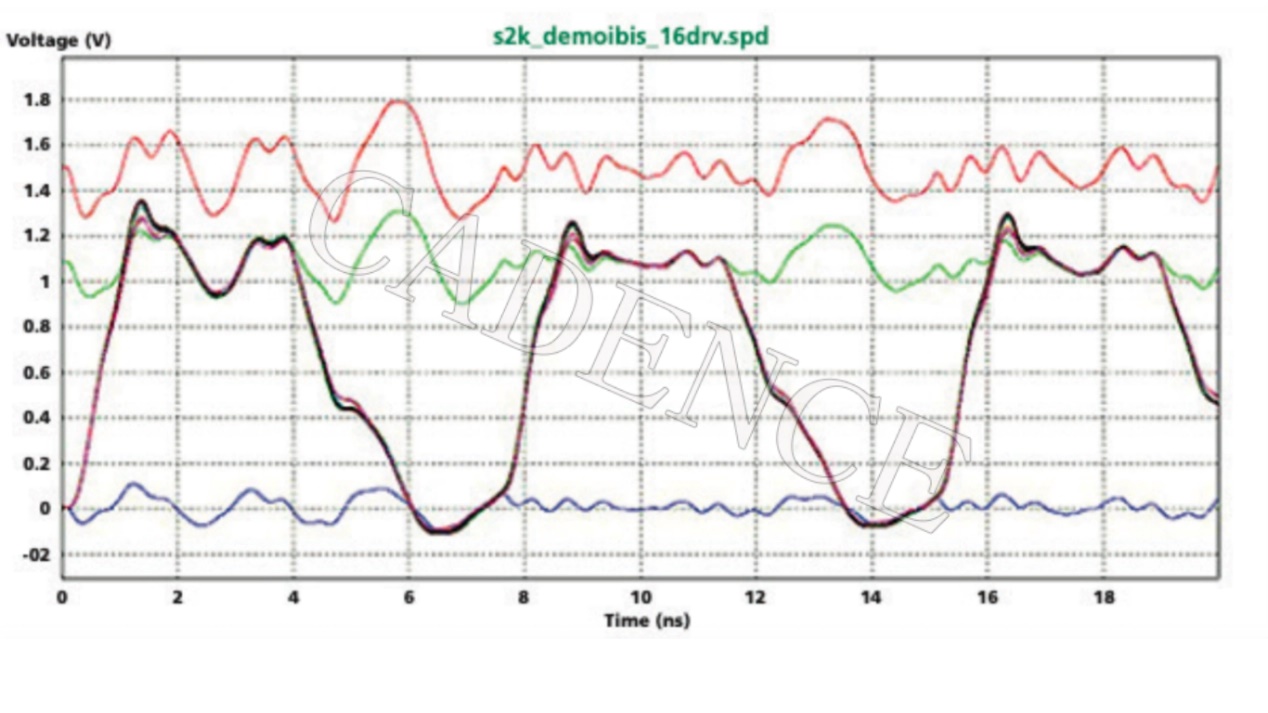

Již v roce 2005 poprvé debutoval koncept „s ohledem na vliv napájení“. Jedná se o metodu simulace pokročilé integrity signálu, která může analyzovat signály a šum výkonu současně (obrázek 1).Řešení integrity signálu, které bere v úvahu vliv napájecího zdroje, musí zvážit odraz, strunné, sekvenční a další efekty a vybavené odpovídajícími simulačními a pravidly technikami kontroly.Stojí za zmínku, že za účelem účinného implementace simulace integrity signálu, která zohledňuje dopad zdroje napájení, je nutné provést ve fázi analýzy po pravidelné kontrole a kabeláži, protože dochází k interakci/spojení roviny a signálu dochází Po dokončení kabelů.

Proto je třeba zajistit úplné řešení, které zohledňuje vliv napájení:

l Sada rychlých inspekčních řešení pro útlum signálu a napájení na signálech

L umím simulovat simulátor časové domény velkých obvodů (výsledky více signálních sítí a energetických sítí)

L Power Network and Signal Network Modeling

l Vysokoúrovňové vstupní/výstup (I/O) Modelování vyrovnávací paměti

Obrázek 1: Výsledek integrity signálu obou vlivu napájení

Ačkoli mnoho nástrojů na trhu podporuje základní standardy I/O modelování, které berou v úvahu vliv napájení, s nepřetržitým vývojem technologie rozhraní paměťového rozhraní, požadavky na nástroje pro integritu signálu se také zvyšují. Přesný nástroj pro extrakci pro Spojovací signál, napájení a pozemní signál na PCB je vzácný.

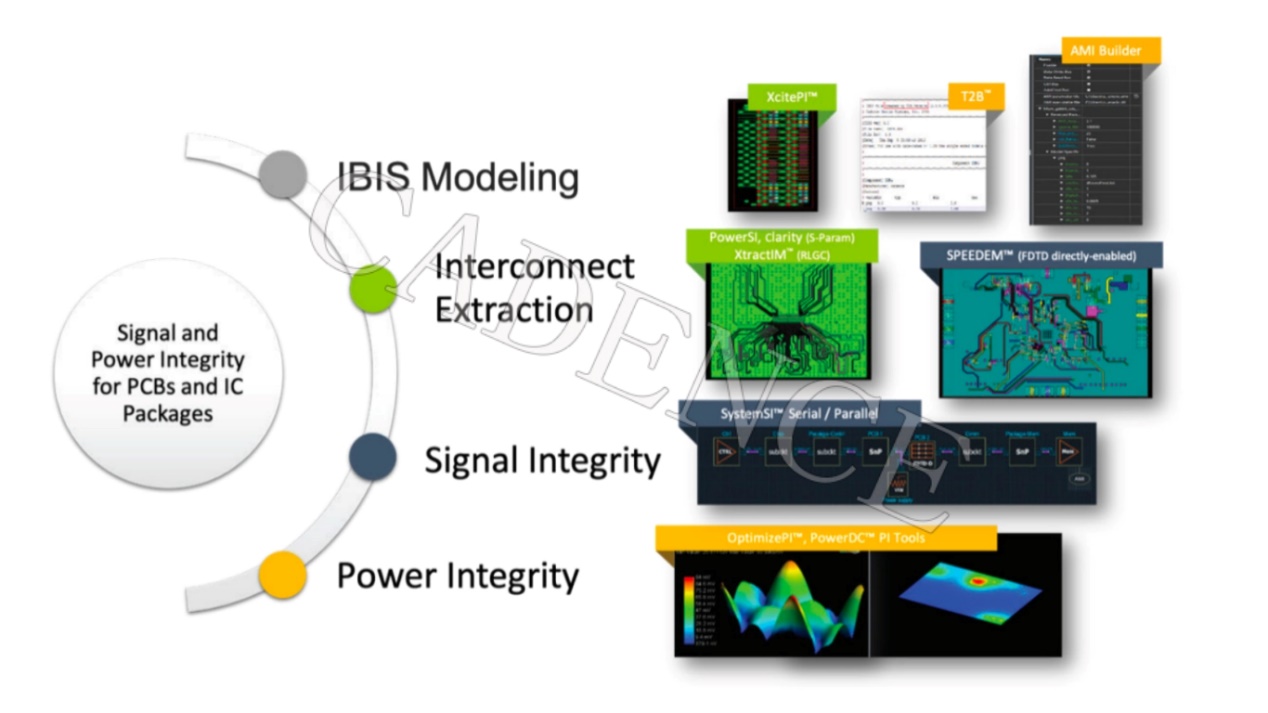

V tomto ohledu jako přední podnik v oblasti simulace EDA poskytuje technologie Sigrity X zahájená Cadence analýza integrity signálu vlivu napájení pro DDR4 a DDR5.

Technologie Sigrity X nejen realizuje přesnou extrakci vázaných signálů, napájecího zdroje a pozemních signálů na žetonech, balení a PCB, ale také může také vytvořit efektivní simulaci na odrazu, ztrátě, bandridálním a synchronním výstupním přepínači (SSO) na stejném čas.Designéři používající technologii sigrity mohou rychle převést model tranzistoru na behaviorální model IBIS, který zvažuje vliv síly, takže během několika hodin může poskytnout přesný, efektivní a komplexní s ohledem na simulaci efektů napájení, což velmi Zkracuje se původní počet původně musí být očíslován. Cyklus designu oblohy.(Obrázek 2)

Obrázek 2: Nástroj pro integritu signálu kadence a integrity energie pro obaly PCB a IC

Technologie Sigrity X zjednodušuje pracovní postup, poskytuje synchronní simulaci designu a přesnost úrovně podpisu pro konečné ověření.Problémy s signály, výkonem a teplem lze vyřešit v každé fázi návrhu, čímž se sníží počet iterací mezi týmy návrhu a analýzy.Návrháři mohou spustit motor jaderného úrovně při navrhování kresleného tkaniny pro simulaci s vysokou nadměrnou prací, čímž poskytují analytické týmy s vysokou kvalitou pro analytické týmy.Později analytický tým použil rozsáhlý paralelní simulační modul sigrity k provedení plné simulace systému, aby se zajistilo, že celý „chip-balení-PCB-shell“ splňuje specifikace designu a připraví se na podpis.

Díky těmto výhodám je sigrity x nejlepší řešení pro paměť DDR5 a rozhraní 112G.Její zlaté standardní propojovací modelování kombinuje simulaci časové domény (simulace obvodu a kanálu) analýzy sériového/roztoku (Serdes) a podporuje rozhraní modelování algoritmu IBIS (AMI), což dává kadenci jedinečné výhody, a proto může extrahovat a podpisovat soulad s rozhraním poskytuje podpisování souladu s rozhraním a poskytuje podpis souladu rozhraní a podpis souladu s rozhraním může extrahovat a podpisovat soulad s rozhraním extrahovat a podpisovat soulad s rozhraním. Kompletní řešení.

Dále, technologie sigrity xtractim a Clarity 3D řešitele lze použít ve spojení, což inženýrům umožňuje vytvářet kompletní modely balení obsahující spojující signály, napájení napájení a uzemnění propojených modelů pro různé typy obalu, které účinně vyrovnávají design balení a charakteristiky balíku, které se balíčky a charakteristiky balíků Mezera mezi.

Technologie sigrity Systemsi navíc podporuje model IBIS, který se může rychle připojit k vlivu napájení a modelu propojení, který bere v úvahu vliv napájení. Návrhář může rychle určit nejhorší situaci touto technologií a porovnat ji s Standard JEDEC, aby se zajistilo, že rozhraní DDR4/DDR5 (včetně požadavků na míru kódu bez bitů) splňuje všechny relevantní specifikace.

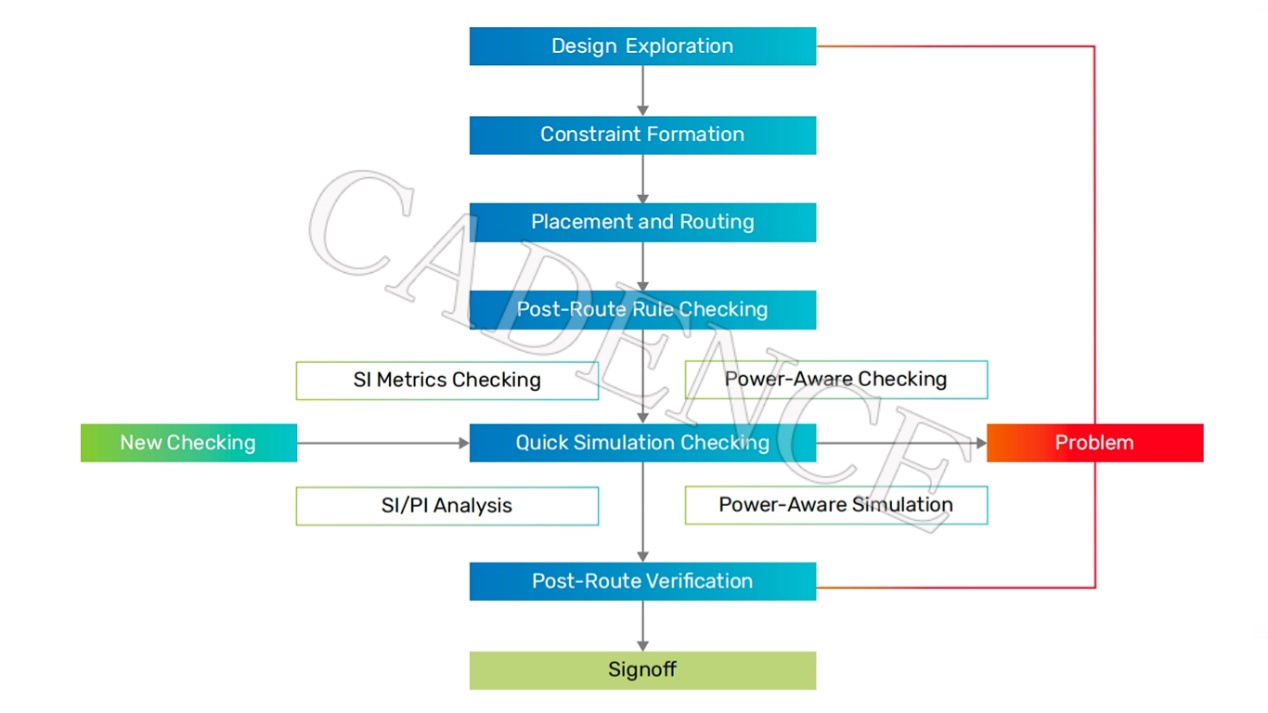

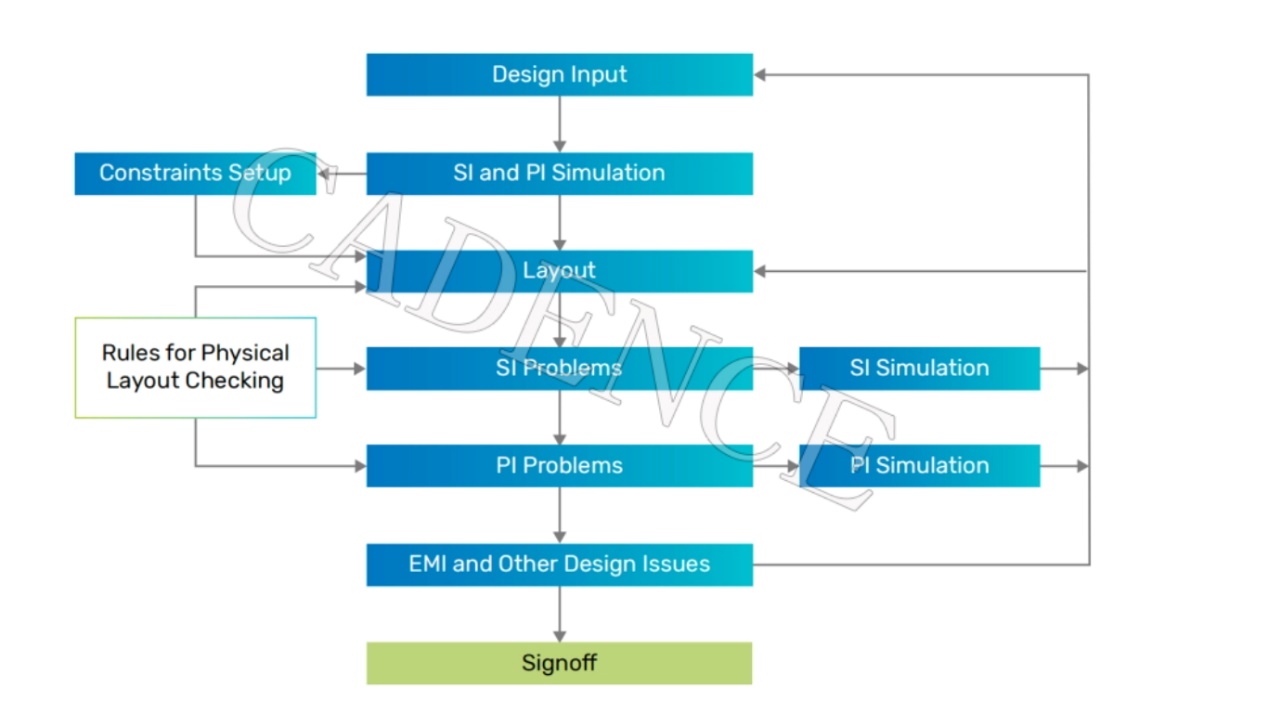

Obrázek 3 je proces inspekce a simulace, který bere v úvahu vliv napájení, který je v ostrém kontrastu s tradičním procesem konstrukce poháněného omezením (obrázek 4).Proces navrhování tradičních ovladačů omezení zahrnuje hlavně čtyři části: zapojení před předáváním, tvorbu omezení, kontrola pravidel a ověření po odepření.

Obrázek 3: Kadence bere v úvahu proces ovladače omezení vlivu napájení

Vs.

Obrázek 4: Příklad procesu navrhování řidiče tradičního omezení

Mezi mnoha současnými simulačními technologiemi jsou často odpojeny mezi analýzou signálu a distribučním sítí distribuce energie (PDN) a existují i další nedostatky.Za normálních okolností, podle složitosti modelu koření, někdy použijte simulaci časové domény k vytvoření přesné rezistence/indukční/kondenzátory (RLC) a někdy předpokládá ideální pozemní rovinu.Model časové domény získaný z toho je založen na jednoduché frekvenční odezvě extrakce simulace. Ačkoli je to pohodlnější, je to mírně nedostatečné z hlediska přesnosti. Pro vyšší frekvence používají inženýři parametry S vytvořené smíšeným řešením řešení.

Ve skutečnosti existuje také efektivní metoda pro kombinování metody domény omezené rozdílné časové domény (FDTD) se smíšeným řešením pro řešení pro rozšíření pokrytí pro signál, napájení a uzemňovací linii.

Úspěšným praxem případem této metody je nástroj Engine Engine Motor Speed2000 Cadence. Integruje a integruje výstup několika řešení pro řešení zapojení obvodu, přenosových vedení a problémů s elektromagnetickým polem a může lépe zobrazit data a interakce napájení/pozemní roviny v různých časy.A použijte metodu FDTD k analýze rozložení balení IC a PCB.Poskytuje důležitý referenční základ pro další optimalizaci návrhu obvodu.

Při vstupu do konečné fáze podpisu inženýři obvykle mají tendenci používat 3D metody modelování plné vlny k získání vyšší přesnosti.To však bude spotřebovat více výpočetních zdrojů a zvětšit dobu simulace.Pro zmírnění tohoto problému lze přijmout divizi a technologii paralelizace.V tomto ohledu je pomocí analýzy 3D řešitele Clarity 3D pro analýzu konečných prvků (FEM) a poté kombinováním technologie sigrity xtractim, výsledky každé analýzy jsou re -biny tak, aby vytvořily model parametru založené na frekvenční odezvě, čímž se dosahuje Celý systém do celého systému nebo v depth a přesné analýze návrhu.

Shrnout

Současně s technologickým skokem byla technologie zlepšena a je nevyhnutelné pro návrháře nové výzvy.Na cestě k paměti DDR5 a novým výzvám, s ostrou „ostrou čepelí“ Cadence Sigrity X, se inženýři mohou klidně vyrovnat se složitými problémy integrity signálu a zajistit, aby produkt nebyl v souladu s specifikacemi. Také svítí. výkon, přidávání další cihly na cestu budoucích inovací.