Balita

Malapit na ang panahon ng DDR5, at hindi maaaring balewalain ang mga bagong hamon

- May-akda:ROGER

- Bitawan:2023-12-04

Sa siklab ng galit ng artipisyal na katalinuhan (AI), pag -aaral ng makina (ML), at pagmimina ng data, ang aming pagnanais para sa pagproseso ng data ay nagpapakita ng hindi pa naganap na paglago ng index.Ang pagharap sa prospect na ito, ang lapad ng bandwidth ng memorya ay naging isang pangunahing "arterya" sa digital na edad.Kabilang sa mga ito, ang teknolohiya ng DDR (Double Data Rate), na kilala para sa dobleng mga rate ng paghahatid ng data at mas mataas na bandwidth bilang isang dynamic na random na memorya ng pag -access (DRAM), ay lubos na na -promote ang pagpapabuti ng pagganap ng computer.Mula sa pagsilang ng unang henerasyon ng teknolohiya ng DDR noong 2000, hanggang sa DDR5 noong 2020, ang bawat henerasyon ng teknolohiya ng DDR ay nakamit ang mga makabuluhang pagpapabuti sa iba't ibang mga aspeto tulad ng bandwidth, pagganap at pagkonsumo ng kuryente.

Ngayon, kung ito ay PC, laptop o artipisyal na katalinuhan, ang iba't ibang mga industriya ay nagpapabilis upang lumipat patungo sa bagong panahon ng DDR5.Ngayong taon, ang henerasyon ng merkado ng AI ay umuusbong, at ang mga server ng AI na ginamit sa mga malalaking aplikasyon ng modelo ay masigasig na na -promote ang demand para sa DDR5.Sa pagbawi ng Demand for Memory Market, ipinakita ng mga supplier ng memorya ng chip ang produksyon ng DDR5 sa ika -apat na quarter ng taong ito upang unti -unting palitan ang kasalukuyang DDR4.

Dumating ang bagong panahon ng DDR5, gayunpaman, ang ilang mga hamon ay humadlang din sa karagdagang pag -unlad ng industriya.

DDR5 ERA: Mga Hamon sa Disenyo sa Likod ng Ultra -High -speed Performance

Noong Hulyo 2020, ang pamantayan ng teknolohiya ng memorya ng DDR5 ay opisyal na pinakawalan, na minarkahan ang teknolohiyang memorya ay nagbukas ng isang bagong kabanata.Ang DDR5 ay nakakaakit ng malawak na pansin na may mas mataas na bandwidth at pagganap.Kung ikukumpara sa nakaraang DDR4, ang pinakamalaking bentahe ng DDR5 ay na makabuluhang nabawasan ang pagkonsumo ng kuryente at doble ang bandwidth.Partikular, ang pinakamataas na rate ng kasalukuyang paglabas ng protocol ng DDR5 ay umabot 6.4GbpsAng dalas ng orasan ay tumaas din mula sa 1.6GHz hanggang 3.2GHz.

Kapag ginalugad namin ang higit pang mga detalye ng DDR5, nalaman din namin na ang bagong teknolohiyang ito ay nagdala ng ilang karagdagang mga hamon sa teknikal.Halimbawa, ang boltahe ng supply ng power ng DDR5 ay bumababa ng 0.1V ng 1.2V mula sa DDR4, na umaabot sa 1.1V. Kahit na ang mas mababang boltahe ng supply ng kuryente Ang mga hamon, tulad ng mga hamon sa teknikal, tulad ng, tulad ng ilang mga hamon sa teknikal, tulad ng, tulad ng ilang mga hamon sa teknikal, tulad ng, tulad ng ilang mga teknikal na hamon, tulad ng, tulad ng ilang mga hamon sa teknikal, tulad ng, tulad ng Ang ilang mga teknikal na hamon, tulad ng, tulad ng mga hamon sa teknikal, tulad ng, tulad ng ilang mga hamon sa teknikal. Halimbawa, mas malamang na maistorbo ng ingay, na ginagawang mas mahirap ang integridad ng signal, dahil ang dami ng ingay sa pagitan ng boltahe sa pagitan ng boltahe sa panahon ng switch ng signal ay mas mababa at maaaring makaapekto sa disenyo.

Ang isa pang pangunahing pagbabago ng DDR5 ay naiiba sa paraan ng Power Management Chip (PMIC) ng DDR4 ay isinama sa motherboard. Inilipat ng DDR5 ang Power Management IC (PMIC) mula sa motherboard hanggang sa dual -column direct memory module (DIMM).Pinapayagan nito ang pamamahala ng kuryente, regulasyon ng boltahe at pagkakasunud -sunod ng kapangyarihan -on sa pisikal na mas malapit sa aparato ng imbakan sa module, na tumutulong din na matiyak ang integridad ng supply ng kuryente (PI) at mapahusay ang kontrol ng pamamaraan ng operasyon ng PMIC.

Bilang karagdagan, kapag ang kabuuang bilang ng mga bits ng data ay nananatiling hindi nagbabago, ang bilang ng mga channel ng DIMM mula sa 1 channel hanggang 2 na mga channel ay isang mahalagang pag -unlad din. Mga signal ng orasan upang mapagbuti ang integridad ng signal.

Malinaw, ang pag -unlad ng pamantayan ng DDR5 ay isinasaalang -alang din ang problema sa integridad ng signal, at ang paglipat ng PMIC sa module ay magpapatuloy din sa kaukulang mga pakinabang.Gayunpaman, kailangan pa ring isaalang -alang ng mga taga -disenyo ang pangkalahatang epekto ng integridad ng signal ng supply ng kuryente.Tulad ng nabanggit sa itaas, ang DDR5 ay may rate ng data na hanggang sa 6.4Gbps at ang dalas ng orasan ng 3.2GHz system. Ang ingay ng kuryente ay maaaring maging sanhi ng mas malinaw na mga problema sa mataas na operasyon na ito, na makakaapekto sa pagganap at katatagan ng system.Kung ang integridad ng kuryente at integridad ng signal ay nasuri nang hiwalay, ang problema ng ingay ng supply ng kuryente ay maaaring makaligtaan.

Samakatuwid, upang mabigyan ang buong pag -play sa pagganap ng DDR5, ang lahat ng mga pangunahing punto ng system ay dapat magsama ng mga chips, packaging, at PCB para sa pagsusuri ng integridad ng signal ng impluwensya ng supply ng kuryente.Gayunpaman, ang pagsusuri ng antas na ito ay isang kumplikadong gawain. Mayroon itong mataas na mga kinakailangan para sa mga tool ng hardware at software na ginamit para sa pagsusuri ng kunwa para sa pinagbabatayan na platform ng computing. Ang kahirapan at pagiging kumplikado ng disenyo.

Ganap na ilabas ang potensyal ng DDR5, cadence

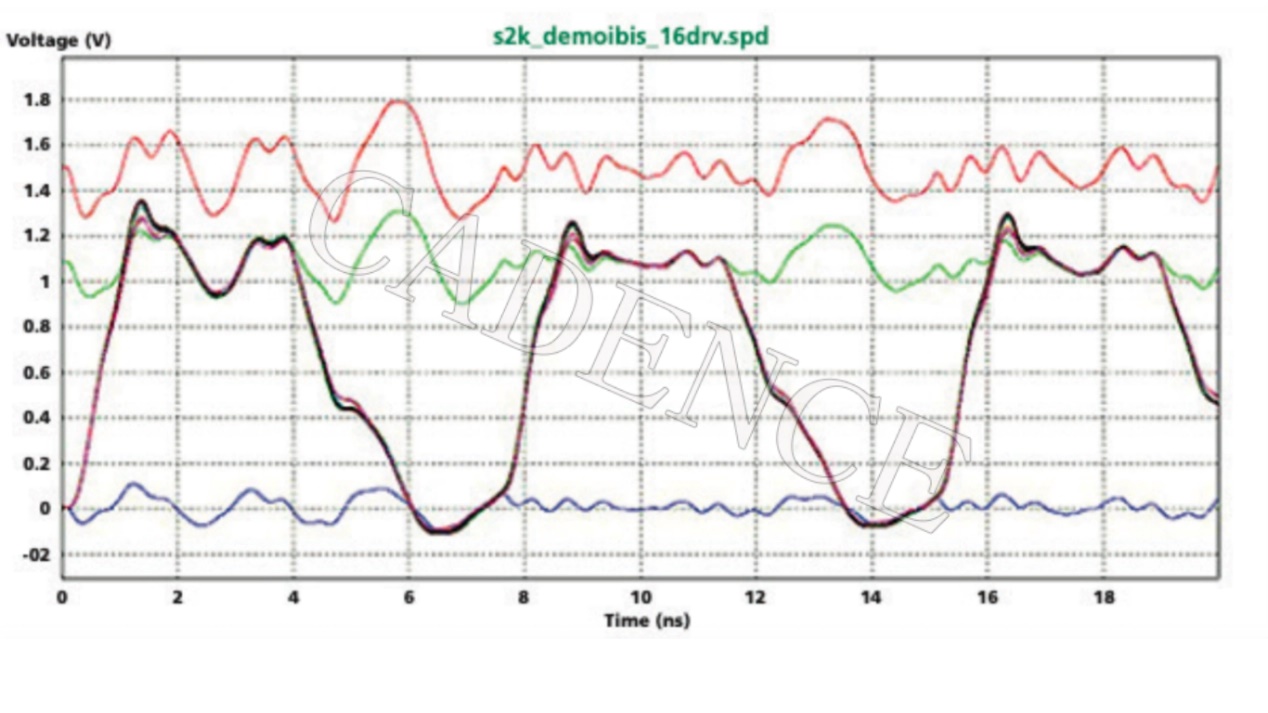

Maaga pa noong 2005, ang konsepto ng "isinasaalang -alang ang impluwensya ng supply ng kuryente" na pinasiyahan sa unang pagkakataon. Ito ay isang advanced na pamamaraan ng simulation ng integridad ng signal na maaaring pag -aralan ang mga signal at ingay ng kuryente nang sabay -sabay (Larawan 1).Ang solusyon sa integridad ng signal na isinasaalang -alang ang impluwensya ng supply ng kuryente ay dapat isaalang -alang ang pagmuni -muni, stringing, sunud -sunod at iba pang mga epekto, at nilagyan ng kaukulang simulation at mga diskarte sa inspeksyon.Kapansin -pansin na upang epektibong maipatupad ang simulation ng signal ng integridad na isinasaalang -alang ang epekto ng suplay ng kuryente, kinakailangan upang maisagawa sa yugto ng pagsusuri pagkatapos ng regular na inspeksyon at mga kable, dahil ang pakikipag -ugnay/pagkabit ng eroplano at signal ay nangyayari Matapos makumpleto ang mga kable.

Samakatuwid, ang isang kumpletong solusyon na isinasaalang -alang ang impluwensya ng supply ng kuryente ay madalas na kailangang ibigay:

l Isang hanay ng mga mabilis na solusyon sa inspeksyon para sa pagpapalambing ng signal at supply ng kuryente sa mga signal

l maaaring gayahin ang oras ng simulator ng domain ng mga malalaking circuit (ang mga resulta ng maraming mga network ng signal at mga network ng kuryente)

L Power Network at Modelong Network ng Signal

l High -level Input/Output (I/O) Pagmomodelo ng Buffer

Larawan 1: Ang resulta ng integridad ng signal ng parehong impluwensya ng supply ng kuryente

Bagaman maraming mga tool sa merkado ang sumusuporta sa pangunahing pamantayan sa pagmomolde ng I/O na isinasaalang -alang ang impluwensya ng suplay ng kuryente, na may patuloy na pag -unlad ng teknolohiya ng interface ng memorya, ang mga kinakailangan ng merkado para sa mga tool ng integridad ng signal ay tumataas din. Ang tumpak na tool ng pagkuha para sa Ang pagsasama ng signal, supply ng kuryente at signal ng lupa sa PCB ay bihirang.

Kaugnay nito, bilang isang nangungunang negosyo sa larangan ng EDA simulation, ang teknolohiya ng Sigrity X na inilunsad ng Cadence ay nagbibigay ng isang signal integridad na pagsusuri ng impluwensya ng supply ng kuryente para sa DDR4 at DDR5.

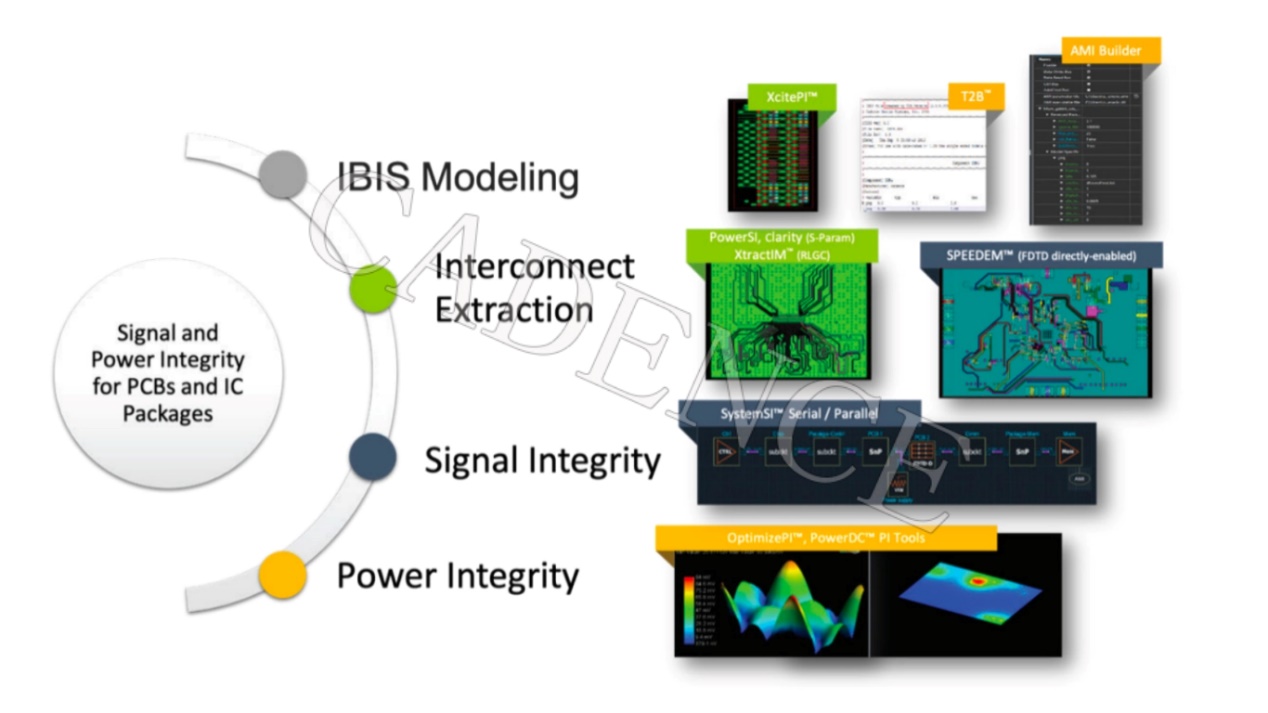

Hindi lamang napagtanto ng Sigrity X Technology oras.Ang mga taga -disenyo na gumagamit ng teknolohiya ng sigrity ay maaaring mabilis na mai -convert ang modelo ng transistor -level sa isang modelo ng pag -uugali -level na IBIS na isinasaalang -alang ang impluwensya ng kapangyarihan, upang sa loob ng ilang oras, maaari itong magbigay ng tumpak, mahusay at komprehensibong pagsasaalang -alang ng kunwa ng mga epekto ng supply ng kuryente, na labis pinaikling ang orihinal na bilang ng orihinal na kailangang mabilang. Sky Design Cycle.(Figure 2)

Larawan 2: Ang integridad ng signal ng cadence at tool ng integridad ng kuryente para sa PCB at IC packaging

Ang teknolohiya ng Sigrity X ay pinapasimple ang daloy ng trabaho, nagbibigay ng disenyo ng kasabay na simulation at ang kawastuhan ng antas ng pag -sign para sa pangwakas na pag -verify.Ang mga senyas, kapangyarihan, at mga problema sa init ay maaaring malutas sa bawat yugto ng disenyo, sa gayon binabawasan ang bilang ng mga iterasyon sa pagitan ng mga koponan ng disenyo at pagsusuri.Maaaring patakbuhin ng mga taga -disenyo ang nuclear -level engine sa disenyo ng tela ng pagguhit para sa mataas na simulation, sa gayon ay nagbibigay ng mataas na disenyo ng mga koponan upang mapatunayan.Nang maglaon, ginamit ng koponan ng pagsusuri ang malakihang kahanay na simulation engine ng sigrity upang makagawa ng buong simulation ng system upang matiyak na ang buong "chip-packaging-PCB-shell" ay nakakatugon sa mga pagtutukoy ng disenyo at maghanda para sa pag-sign.

Ang mga pakinabang na ito ay gumagawa ng Sigrity X ang pinakamahusay na solusyon para sa memorya ng DDR5 at 112G interface.Ang gintong pamantayang interconnect na pagmomolde ay pinagsasama ang oras ng simulation ng domain (circuit at channel simulation) ng pagsusuri ng serial/solution (SEDES) at pagsuporta sa IBIS algorithm modeling interface (AMI), na nagbibigay ng mga natatanging pakinabang, sa gayon ay maaaring kunin at ang pag -sign ng pagsunod sa interface ay nagbibigay Kumpletuhin ang mga solusyon.

Karagdagan, ang Sigrity Xtractim at Clarity 3D Solver Technology ay maaaring magamit kasabay, na nagpapahintulot sa mga inhinyero na lumikha ng kumpletong mga modelo ng packaging na naglalaman ng mga signal ng pagkabit, power supply at grounding interconnect models para sa iba't ibang uri ng packaging, na epektibong bumubuo para sa disenyo ng packaging at mga katangian ng pakete Ang agwat sa pagitan.

Bilang karagdagan, sinusuportahan ng teknolohiya ng mga sistema ng sigrity ang modelo ng IBIS na maaaring mabilis na kumonekta sa impluwensya ng suplay ng kuryente at ang modelo ng magkakaugnay na isinasaalang -alang ang impluwensya ng suplay ng kuryente. Mabilis na matukoy ng taga -disenyo ang pinakamasamang sitwasyon sa pamamagitan ng teknolohiyang ito at ihambing ito sa Ang pamantayan ng JEDEC upang matiyak na ang DDR4/DDR5 ang interface (kabilang ang mga kinakailangan ng rate ng rate ng code) ay nakakatugon sa lahat ng mga kaugnay na pagtutukoy.

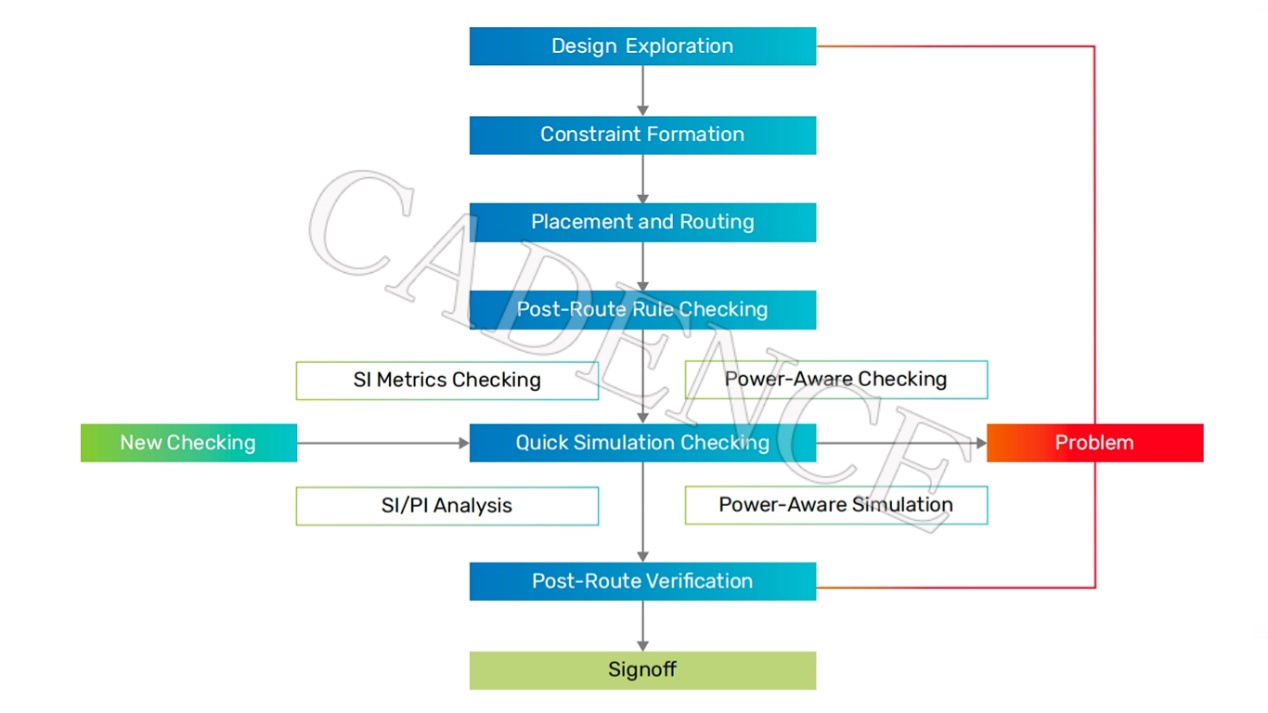

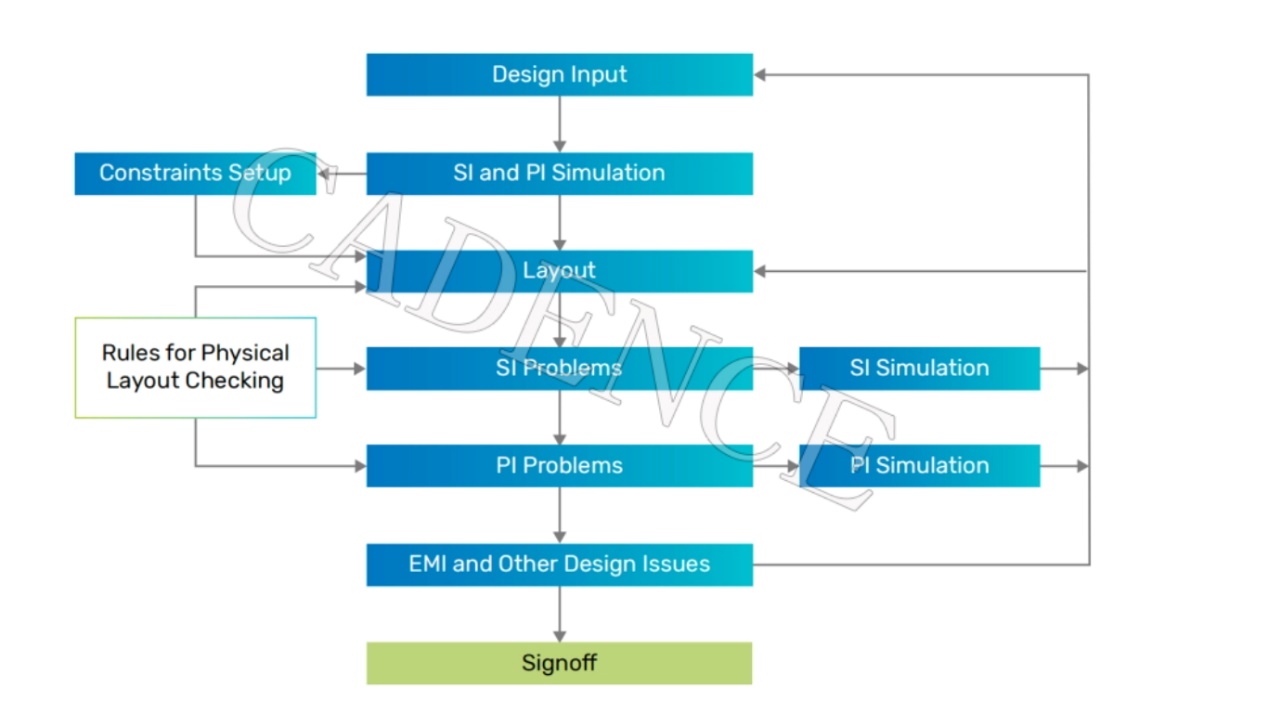

Ang Figure 3 ay ang proseso ng pag -iinspeksyon at kunwa na isinasaalang -alang ang impluwensya ng suplay ng kuryente, na kung saan ay matalim na kaibahan sa tradisyunal na proseso ng pagpilit -driven na disenyo (Larawan 4).Ang proseso ng disenyo ng tradisyonal na mga driver ng pagpilit ay higit sa lahat ay may kasamang apat na bahagi: pre -layout na mga kable, pagbuo ng pagpilit, mga panuntunan inspeksyon, at pag -verify ng pag -post.

Larawan 3: Isinasaalang -alang ni Cadence ang proseso ng pagpilit driver ng impluwensya ng supply ng kuryente

Vs.

Larawan 4: Halimbawa ng tradisyonal na proseso ng disenyo ng driver

Kabilang sa maraming kasalukuyang mga teknolohiya ng simulation, madalas na mga pagkakakonekta sa pagitan ng pagsusuri ng signal at network ng pamamahagi ng kuryente (PDN), at may ilang iba pang mga pagkukulang.Sa ilalim ng normal na mga pangyayari, ayon sa pagiging kumplikado ng modelo ng pampalasa, kung minsan ay gumagamit ng simulation ng oras ng domain upang makabuo ng tumpak na paglaban/inductance/capacitors (RLC) na mga modelo, at kung minsan ay ipinapalagay nito ang isang mainam na eroplano ng lupa.Ang modelo ng oras ng domain na nakuha mula dito ay batay sa simpleng dalas ng pagtugon ng pagkuha ng kunwa. Kahit na mas maginhawa, bahagyang hindi sapat sa mga tuntunin ng kawastuhan. Para sa mas mataas na mga frequency, gagamitin ng mga inhinyero ang mga parameter ng S na nilikha ng isang halo -halong aparato.

Sa katunayan, mayroon ding isang mahusay na pamamaraan upang pagsamahin ang paraan ng limitadong pagkakaiba ng oras ng domain (FDTD) na may halo -halong aparato ng paglutas upang mapalawak ang saklaw sa signal, power supply at grounding line.

Ang matagumpay na kaso ng kasanayan sa pamamaraang ito ay ang tool ng Speed2000 ng Cadence Speed2000. mga oras.At gamitin ang pamamaraan ng FDTD upang pag -aralan ang layout ng IC packaging at PCB.Nagbibigay ito ng isang mahalagang batayan ng sanggunian para sa karagdagang pag -optimize ng disenyo ng circuit.

Kapag pumapasok sa pangwakas na yugto ng pag -sign, ang mga inhinyero ay karaniwang may posibilidad na gumamit ng mga pamamaraan ng pagmomolde ng 3D full -wave upang makakuha ng mas mataas na kawastuhan.Ngunit ito ay kumonsumo ng higit pang mga mapagkukunan ng computing at dagdagan ang oras ng kunwa.Upang maibsan ang problemang ito, maaaring ma -ampon ang dibisyon at pagkakatulad na teknolohiya.Kaugnay nito, sa pamamagitan ng paggamit ng Clarity 3D Solver para sa isang Finite Element Analysis (FEM) na pagsusuri, at pagkatapos ay pagsasama -sama ng teknolohiya ng Sigrity Xtractim, ang mga resulta ng bawat pagsusuri ay muling kinakalkula upang makabuo ng isang modelo ng parameter batay sa dalas na tugon, sa gayon nakamit ang buong sistema sa buong sistema o sa -depth at tumpak na pagsusuri ng disenyo.

Ibuod

Kasabay nito ang paglukso ng teknolohikal, napabuti ang teknolohiya, at hindi maiiwasang maglagay ng mga bagong hamon para sa mga taga -disenyo.Sa daan patungo sa memorya ng DDR5 at mga bagong hamon, na may matalim na "matalim na talim" ng Cadence Sigrity X, ang mga inhinyero ay maaaring mahinahon na makayanan ang mga kumplikadong isyu ng integridad ng signal, tinitiyak na ang produkto ay hindi lamang naaayon sa mga pagtutukoy. Nagniningning din ito sa pagganap, pagdaragdag ng isa pang ladrilyo sa kalsada ng makabagong pagbabago.