Nyheter

DDR5 -eran närmar sig och nya utmaningar kan inte ignoreras

- Författare:ROGER

- Släpp på:2023-12-04

I frenesin av artificiell intelligens (AI), maskininlärning (ML) och data mining visar vår önskan om databehandling enastående indextillväxt.Mot denna möjlighet har bredden på minnesbandbredden blivit en viktig "artärer" i den digitala tidsåldern.Bland dem har DDR -teknik (dubbel datahastighet), känd för dubbla dataöverföringshastigheter och högre bandbredd som ett dynamiskt slumpmässigt åtkomstminne (DRAM), kraftigt främjat förbättringen av datorprestanda.Från födelsen av den första generationen av DDR -teknik 2000, till DDR5 2020, har varje generation av DDR -teknik uppnått betydande förbättringar av olika aspekter som bandbredd, prestanda och kraftförbrukning.

I dag, oavsett om det är PC, bärbar dator eller konstgjord intelligens, accelererar olika branscher för att gå mot den nya eran av DDR5.I år blomstrar Generation AI -marknaden och AI -servrar som används i stora modellapplikationer har kraftfullt främjat efterfrågan på DDR5.Med återhämtningen av efterfrågan på minnesmarknaden har minneschipleverantörer visat produktionskapaciteten för DDR5 under det fjärde kvartalet i år för att gradvis ersätta den nuvarande DDR4.

Den nya eran av DDR5 har anlänt, men vissa utmaningar har också hindrat den vidare utvecklingen av branschen.

DDR5 ERA: Designutmaningar bakom Ultra -High -hastighetsprestanda

I juli 2020 släpptes DDR5 Memory Technology Standard officiellt, vilket markerade att minnetekniken öppnade ett nytt kapitel.DDR5 har väckt omfattande uppmärksamhet med högre bandbredd och prestanda.Jämfört med den tidigare DDR4 är den största fördelen med DDR5 att den har minskat kraftförbrukningen avsevärt och fördubblat bandbredden.Specifikt har den högsta frekvensen av DDR5: s nuvarande frisläppningsprotokoll nått 6.4 GbpsKlockfrekvensen ökade också från 1,6 GHz till 3,2 GHz.

När vi utforskar mer information om DDR5, finner vi också att denna nya teknik har gett några ytterligare tekniska utmaningar.Till exempel minskar strömförsörjningsspänningen för DDR5 med 0,1V med 1,2V från DDR4, och når 1,1V. Även om den lägre strömförsörjningsspänningen minskar strömförbrukningen och förlänger batteritiden, ger det också några tekniska utmaningar, till exempel tekniska Utmaningar, till exempel tekniska utmaningar, till exempel vissa tekniska utmaningar, till exempel vissa tekniska utmaningar, till exempel vissa tekniska utmaningar, till exempel vissa tekniska utmaningar, till exempel, till exempel, till exempel Vissa tekniska utmaningar, till exempel tekniska utmaningar, till exempel vissa tekniska utmaningar. Till exempel är det mer troligt att det störs av brus, vilket gör signalintegriteten mer utmanande, eftersom mängden brus mellan spänningen Mellan spänningen under signalomkopplaren är mindre och kan påverka designen.

En annan viktig förändring av DDR5 skiljer sig från hur krafthanteringschipet (PMIC) för DDR4 är integrerad på moderkortet. DDR5 överförde Power Management IC (PMIC) från moderkortet till dubbel -kolumnens direktminnesmodul (DIMM).Detta möjliggör krafthantering, spänningsreglering och kraft -vid -sekvens till fysisk närmare lagringsenheten på modulen, vilket också hjälper till att säkerställa strömförsörjningsintegritet (PI) och förbättra kontrollen av PMIC -driftsmetoden.

Dessutom, när det totala antalet databitar förblir oförändrade, är antalet DIMM -kanaler från 1 kanal till 2 kanaler också en viktig framsteg. Genom att överföra data till två smala kanalöverföring kan det mer effektivt genereras och genereras mer effektivt tilldela tilldela tilldela mer effektivt tilldela Klocksignaler för att förbättra signalintegriteten.

Uppenbarligen har utvecklingen av DDR5 -standarden också tagit hänsyn till signalintegritetsproblemet, och överföring av PMIC till modulen kommer också att utöva motsvarande fördelar.Emellertid måste designers fortfarande överväga den totala effekten av signalintegriteten för kraftförsörjningen.Som nämnts ovan har DDR5 en datahastighet på upp till 6,4 Gbps och 3,2 GHz -systemklockfrekvensen. Strömbrus kan orsaka mer uppenbara problem i denna höga hastighetsoperation, vilket kommer att påverka systemets prestanda och stabilitet.Om kraftintegriteten och signalintegriteten analyseras separat kan problemet med bruset från strömförsörjningen missas.

Därför måste alla viktiga punkter i systemet för att ge full spel till DDR5 -prestanda inkludera chips, förpackning och PCB för signalintegritetsanalys av påverkan av strömförsörjning.Analysen av denna nivå är emellertid en komplex uppgift. Den har höga krav för hårdvaru- och mjukvaruverktyg som används för simuleringsanalys för den underliggande datorplattformen. Svårigheten och komplexiteten i designen.

Släpp helt potentialen för DDR5, Cadence

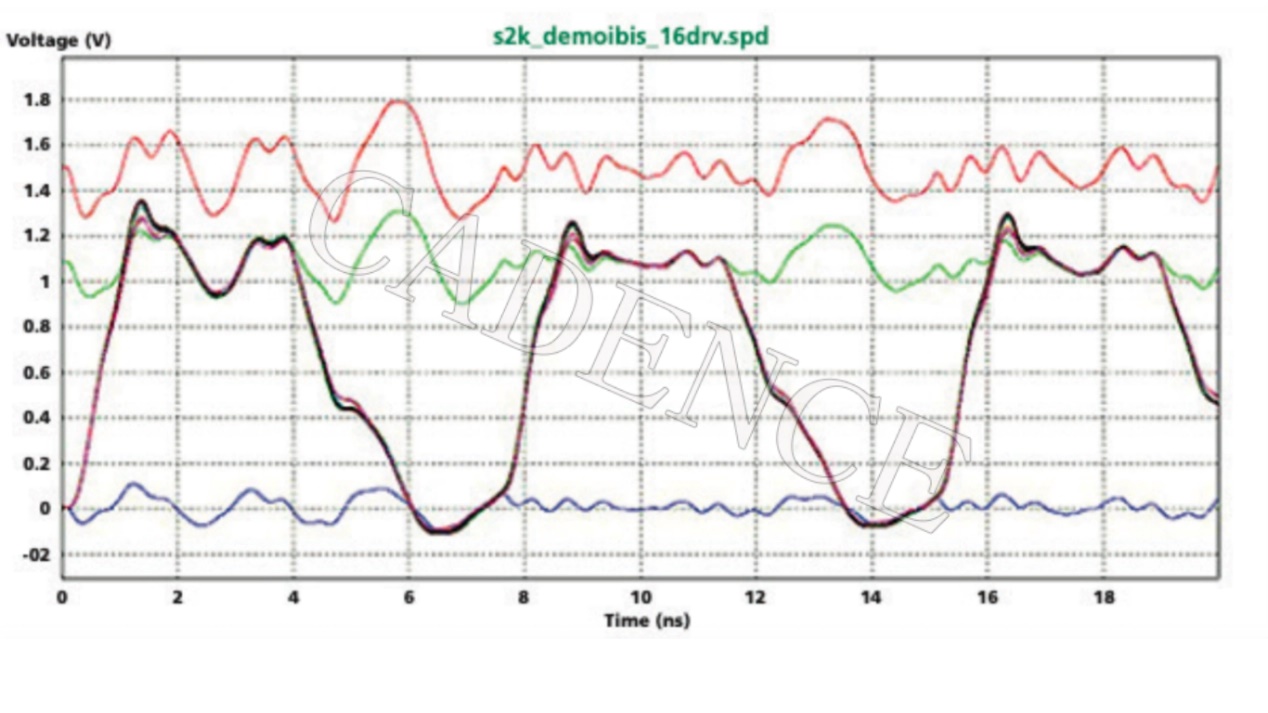

Redan 2005 debuterade konceptet att "ta hänsyn till påverkan av strömförsörjning" för första gången. Det är en avancerad signalintegritetssimuleringsmetod som kan analysera signaler och kraftbrus samtidigt (figur 1).Signalintegritetslösningen som tar hänsyn till påverkan av strömförsörjningen måste överväga reflektion, strängning, sekventiell och andra effekter och utrustade med motsvarande simulerings- och reglerinspektionstekniker.Det är värt att notera att för att effektivt implementera signalintegritetssimuleringen som tar hänsyn till effekten av strömförsörjning är det nödvändigt att utföra i analysfasen efter regelbunden inspektion och ledningar, eftersom interaktionen/kopplingen av planet och signalen inträffar Efter att ledningarna är klar.

Därför måste en komplett lösning som tar hänsyn till påverkan av strömförsörjning ofta:

l En uppsättning snabbinspektionslösningar för signaldämpning och strömförsörjning på signaler

l kan simulera tidsdomänets simulator för stora kretsar (resultaten från flera signalnätverk och kraftnätverk)

L Power Network och Signal Network Modelling

l Hög nivå Input/Output (I/O) Buffertmodellering

Bild 1: Resultatet av signalintegriteten för både påverkan av kraftförsörjningen

Även om många verktyg på marknaden stöder de grundläggande I/O -modelleringsstandarderna som tar hänsyn till påverkan av kraftförsörjning, med kontinuerlig utveckling av minnesgränssnittstekniken, ökar marknadens krav för signalintegritetsverktyg också. Det exakta extraktionsverktyget för Kopplingssignal, strömförsörjning och marksignal på PCB är sällsynt.

I detta avseende, som ett ledande företag inom EDA -simulering, ger Sigrity X -tekniken som lanseras av Cadence en signalintegritetsanalys av påverkan av strömförsörjning för DDR4 och DDR5.

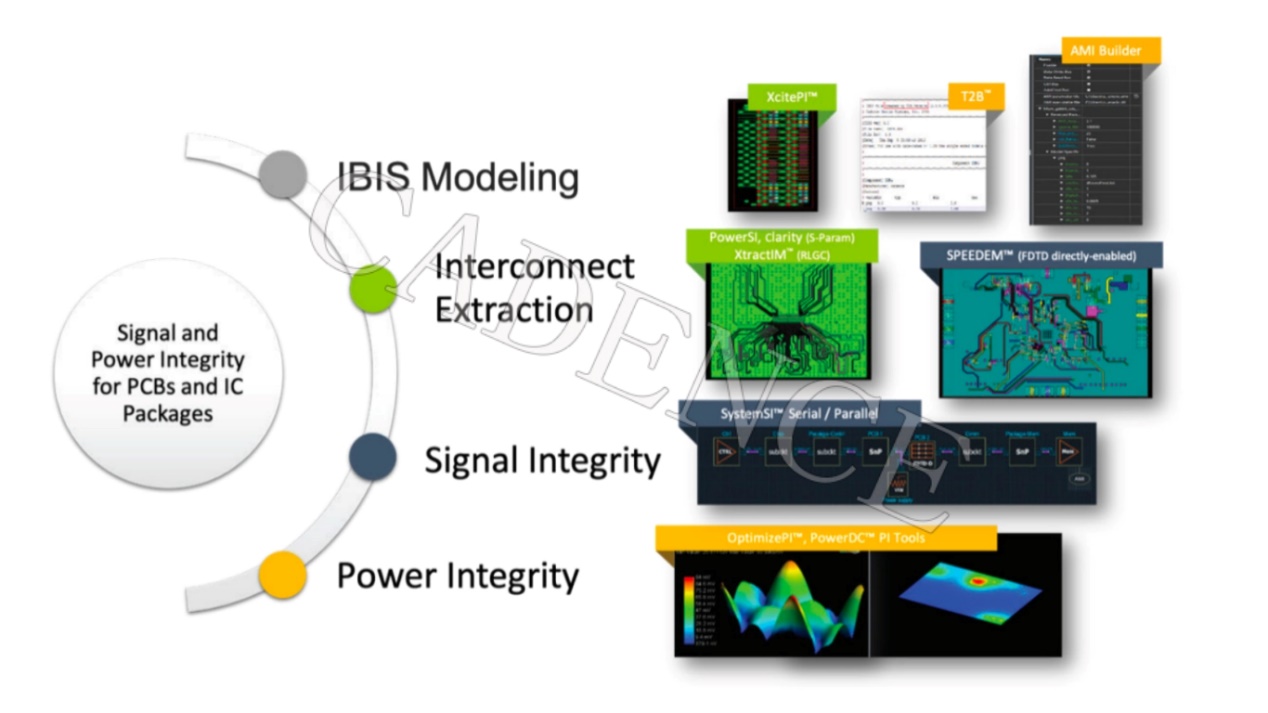

Sigrity X -teknik inser inte bara den exakta extraktionen av kopplade signaler, strömförsörjning och marksignaler på chips, förpackning och PCB, utan kan också göra effektiv simulering av reflektion, förlust, bandidal och synkron switch -effekt (SSO) vid samma tid.Formgivare som använder Sigrity -teknik kan snabbt konvertera transistor -nivå -modellen till en beteendemässig IBIS -modell som beaktar påverkan av kraft, så att den inom några timmar kan ge exakt, effektiv och omfattande med tanke på simulering av kraftförsörjning, som i hög grad Förkortar det ursprungliga antalet ursprungligen måste numreras. Sky Design Cycle.(figur 2)

Bild 2: Cadence Signal Integrity and Power Integrity Tool för PCB och IC -förpackning

Sigrity X -tekniken förenklar arbetsflödet, ger design synkron simulering och noggrannheten för signeringsnivån för slutlig verifiering.Signaler, kraft- och värmeproblem kan lösas i varje designsteg och därmed minska antalet iterationer mellan design- och analysteamen.Formgivare kan köra kärnkraftsmotorn i utformningen av ritduken för simulering med hög precision och därmed tillhandahålla högkvalitetsdesign för analysteam för att verifiera.Senare använde analysteamet den storskaliga parallella simuleringsmotorn för SIGRITY för att göra full systemsimulering för att säkerställa att hela "chip-packning-PCB-Shell" uppfyller designspecifikationerna och förbereder sig för signeringen.

Dessa fördelar gör Sigrity X till den bästa lösningen för DDR5 -minne och 112G -gränssnitt.Dess Golden Standard Interconnect -modellering kombinerar tidsdomänsimulering (Circuit and Channel Simulation) för serie/lösning (SERDES) -analys och stöd för IBIS -algoritmmodelleringsgränssnittet (AMI), som ger kadens unika fördelar, därigenom kan extrahera och gränssnittsöverensstämmelse Signing tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller tillhandahåller för tillhandahåller tillhandahåller för tillhandahåller. Kompletta lösningar.

Sigrity Xtractim och Clarity 3D Solver Technology kan dessutom användas i samband, vilket gör det möjligt för ingenjörer att skapa kompletta förpackningsmodeller som innehåller kopplingssignaler, strömförsörjning och jordning av sammankopplingar för olika typer av förpackningar, som effektivt kompenserar för förpackningsdesign och paketegenskaper Klyftan mellan.

Dessutom stöder Sigrity Systemsi -tekniken IBIS -modellen som snabbt kan ansluta till påverkan av kraftförsörjning och sammankopplingsmodellen som tar hänsyn till påverkan av strömförsörjning. Designern kan snabbt bestämma den värsta situationen genom denna teknik och jämföra den med JEDEC -standard för att säkerställa att DDR4/DDR5 gränssnittet (inklusive Bitless Code Rate -kraven) uppfyller alla relevanta specifikationer.

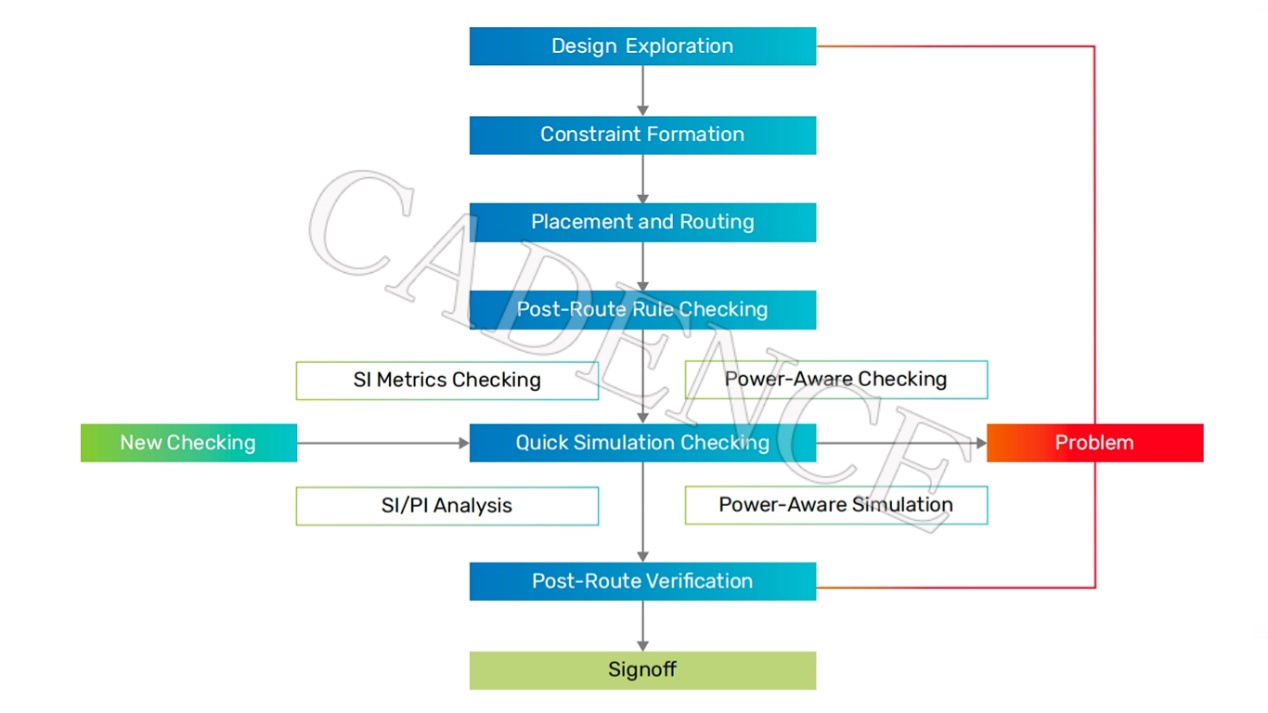

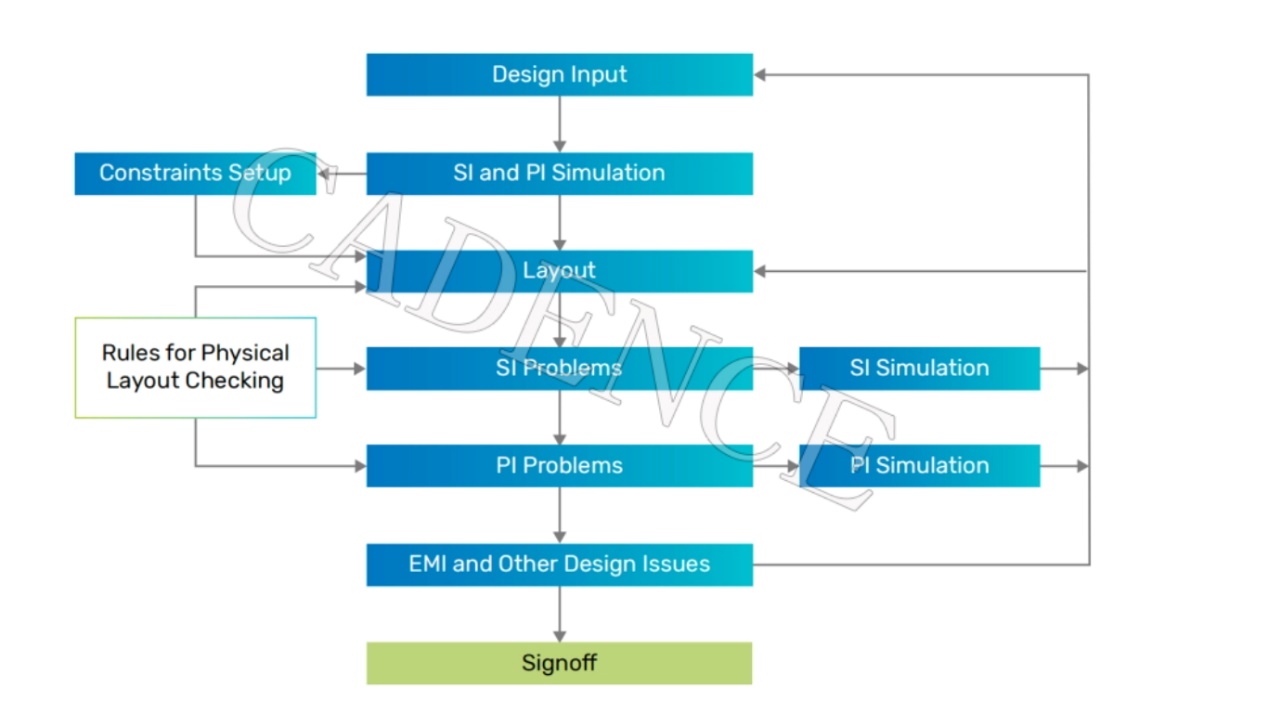

Figur 3 är inspektions- och simuleringsprocessen som tar hänsyn till påverkan av strömförsörjningen, som står i skarp kontrast till den traditionella begränsningstyrda designprocessen (figur 4).Konstruktionsprocessen för traditionella begränsningsförare inkluderar huvudsakligen fyra delar: ledning av layout, begränsningsbildning, reglerinspektion och verifiering efter ledning.

Bild 3: Cadence tar hänsyn till processen för begränsningsföraren för påverkan av strömförsörjning

MOT

Bild 4: Exempel på traditionell begränsningsprocess

Bland de många aktuella simuleringsteknologierna finns det ofta kopplingar mellan signalanalys och kraftdistributionsnätverk (PDN), och det finns några andra brister.Under normala omständigheter använder du ibland en idealisk markplan enligt normala omständigheter för att generera exakt motstånd/induktans/kondensatorer (RLC) -modeller, och ibland antar det ett idealiskt markplan.Tidsdomänmodellen erhållen från detta är baserad på det enkla frekvensresponsen för simuleringsekstraktion. Även om den är mer bekväm är den något otillräcklig när det gäller noggrannhet. För högre frekvenser kommer ingenjörer att använda S -parametrarna som skapas av en blandad lösningsanordning.

I själva verket finns det också en effektiv metod för att kombinera metoden med begränsad skillnadstid (FDTD) med den blandade lösningsanordningen för att utöka täckningen till signal, strömförsörjning och jordningslinje.

Det framgångsrika praktikfallet med denna metod är Cadence's Sigrity Speed2000 motorverktyg. Det integrerar och integrerar utgången från flera lösningar för att lösa krets ledningar, transmissionslinjer och elektromagnetiska fältproblem och kan bättre visa data och effekt/markplaninteraktion på olika tider.Och använd FDTD -metoden för att analysera layouten för IC -förpackningar och PCB.Det ger en viktig referensbasis för ytterligare optimering av kretsdesign.

När man går in i det slutliga signeringssteget tenderar ingenjörer vanligtvis att använda 3D -vågmodelleringsmetoder för att få högre noggrannhet.Men detta kommer att konsumera fler datorresurser och öka simuleringstiden.För att lindra detta problem kan divisions- och parallelliseringsteknologi antas.I detta avseende, genom att använda Clarity 3D -lösaren för en finit Element Analys (FEM) -analys och sedan kombinera SIGRITY XTRACTIM -teknik, är resultaten av varje analys återkommande för att bilda en S -parametermodell baserad på frekvensrespons och därmed uppnå den Hela systemet till hela systemet eller i djup och exakt analys av design.

Sammanfatta

Samtidigt som det tekniska språnget har tekniken förbättrats och det är oundvikligt att lägga nya utmaningar för designers.På vägen mot DDR5 -minne och nya utmaningar, med det skarpa "skarpa bladet" av Cadence Sigrity X, kan ingenjörer lugnt hantera de komplexa frågorna om signalintegritet, vilket säkerställer att produkten inte bara överensstämmer med specifikationerna. Den lyser också in i prestanda, lägga till en annan tegel till vägen för framtida innovation.