Message

L'ère DDR5 approche et de nouveaux défis ne peuvent pas être ignorés

- Auteur:ROGER

- Libération sur:2023-12-04

Dans la frénésie de l'intelligence artificielle (IA), de l'apprentissage automatique (ML) et de l'exploration de données, notre désir de traitement des données montre une croissance sans précédent de l'indice.Face à cette perspective, la largeur de la bande passante de la mémoire est devenue une «artères» clés à l'ère numérique.Parmi eux, la technologie DDR (double débat de données), connu pour les taux de transmission de données doubles et la bande passante plus élevée en tant que mémoire dynamique d'accès aléatoire (DRAM), a considérablement favorisé l'amélioration des performances de l'ordinateur.De la naissance de la première génération de la technologie DDR en 2000, à DDR5 en 2020, chaque génération de technologie DDR a réalisé des améliorations significatives dans divers aspects tels que la bande passante, la performance et la consommation d'énergie.

Aujourd'hui, que ce soit PC, ordinateur portable ou intelligence artificielle, diverses industries accélèrent pour se déplacer vers la nouvelle ère de DDR5.Cette année, le marché de l'IA de génération est en plein essor et les serveurs d'IA utilisés dans les grandes applications de modèle ont vigoureusement favorisé la demande de DDR5.Avec la récupération de la demande de marché de la mémoire, les fournisseurs de puces de mémoire ont montré la capacité de production de DDR5 au quatrième trimestre de cette année pour remplacer progressivement le DDR4 actuel.

La nouvelle ère de DDR5 est arrivée, cependant, certains défis ont également entravé le développement ultérieur de l'industrie.

ERA DDR5: Concevoir des défis derrière des performances de vitesse ultra-high

En juillet 2020, la norme de technologie de la mémoire DDR5 a été officiellement publiée, marquant que la technologie de la mémoire a ouvert un nouveau chapitre.DDR5 a attiré une large attention avec une bande passante et des performances plus élevées.Par rapport au DDR4 précédent, le plus grand avantage du DDR5 est qu'il a considérablement réduit la consommation d'énergie et doublé la bande passante.Plus précisément, le taux le plus élevé du protocole de libération actuel de DDR5 a atteint 6,4 Gbit / sLa fréquence d'horloge est également passée de 1,6 GHz à 3,2 GHz.

Lorsque nous explorons plus de détails sur DDR5, nous constatons également que cette nouvelle technologie a apporté des défis techniques supplémentaires.Par exemple, la tension d'alimentation de DDR5 diminue de 0,1 V par 1,2 V par rapport à DDR4, atteignant 1,1 V. Bien que la tension d'alimentation plus faible réduit la consommation d'énergie et prolonge la durée de vie de la batterie, elle apporte également des défis techniques, tels que tels que techniques Des défis, tels que tels que des défis techniques, tels que, tels que certains défis techniques, tels que certains défis techniques, tels que certains défis techniques, tels que certains défis techniques, tels que, tels que Certains défis techniques, tels que, tels que des défis techniques, tels que certains défis techniques. Par exemple, il est plus susceptible d'être dérangé par le bruit, ce qui rend l'intégrité du signal plus difficile, car la quantité de bruit entre la tension entre la tension pendant l'interrupteur de signal est moindre et peut affecter la conception.

Un autre changement majeur de DDR5 est différent de la façon dont la puce de gestion de l'alimentation (PMIC) de DDR4 est intégrée à la carte mère. DDR5 a transféré le Power Management IC (PMIC) de la carte mère au module de mémoire directe à double colonne (DIMM).Cela permet la gestion de la puissance, la régulation de la tension et la séquence de puissance -Un à la plus proche du périphérique de stockage du module, ce qui permet également d'assurer l'intégrité de l'alimentation (PI) et d'améliorer le contrôle de la méthode de fonctionnement PMIC.

De plus, lorsque le nombre total de bits de données reste inchangé, le nombre de canaux DIMM de 1 canal à 2 canaux est également un progrès important. signaux d'horloge pour améliorer l'intégrité du signal.

De toute évidence, le développement de la norme DDR5 a également pris en compte le problème d'intégrité du signal, et le transfert de PMIC au module exercera également les avantages correspondants.Cependant, les concepteurs doivent encore considérer l'effet global de l'intégrité du signal de l'alimentation.Comme mentionné ci-dessus, DDR5 a un débit de données allant jusqu'à 6,4 Gbit / s et la fréquence d'horloge du système 3,2 GHz.Si l'intégrité de la puissance et l'intégrité du signal sont analysées séparément, le problème du bruit de l'alimentation peut être manqué.

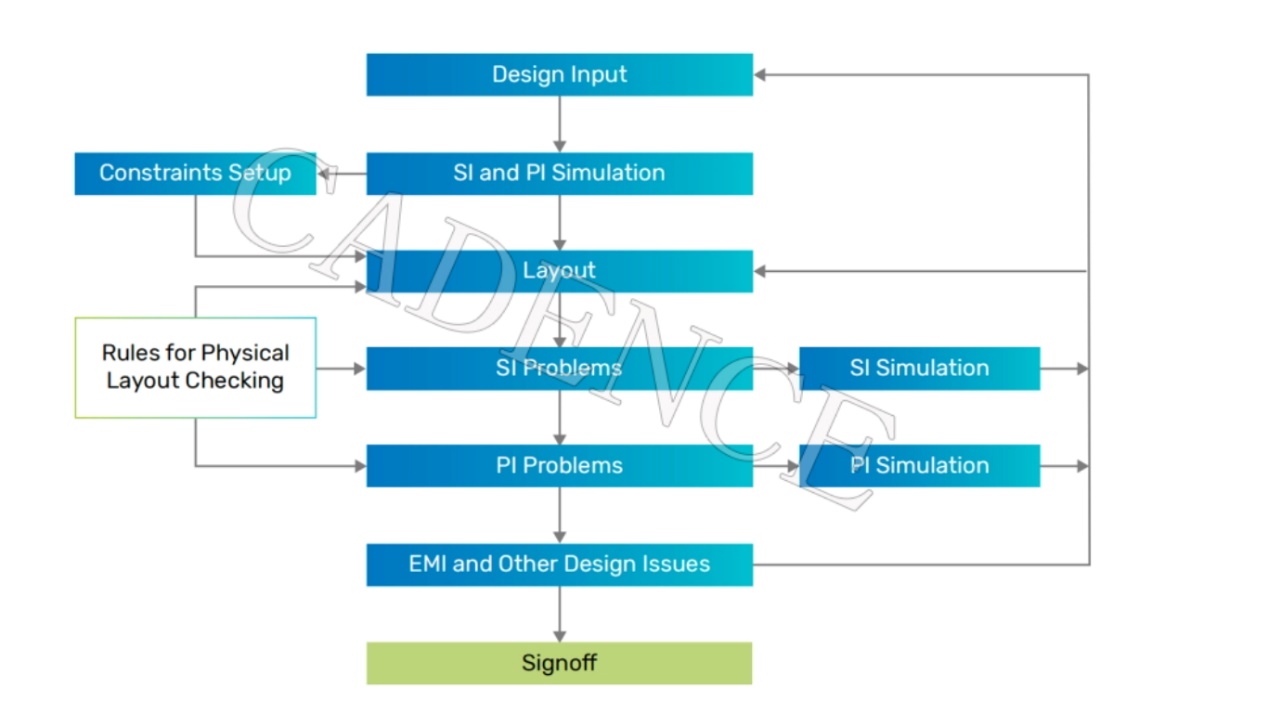

Par conséquent, afin de donner un jeu complet aux performances de DDR5, tous les points clés du système doivent inclure les puces, l'emballage et le PCB pour l'analyse de l'intégrité du signal de l'influence de l'alimentation électrique.Cependant, l'analyse de ce niveau est une tâche complexe. Il a des exigences élevées pour les outils matériels et logiciels utilisés pour l'analyse de simulation pour la plate-forme informatique sous-jacente. La difficulté et la complexité de la conception.

Libérez pleinement le potentiel de DDR5, Cadence

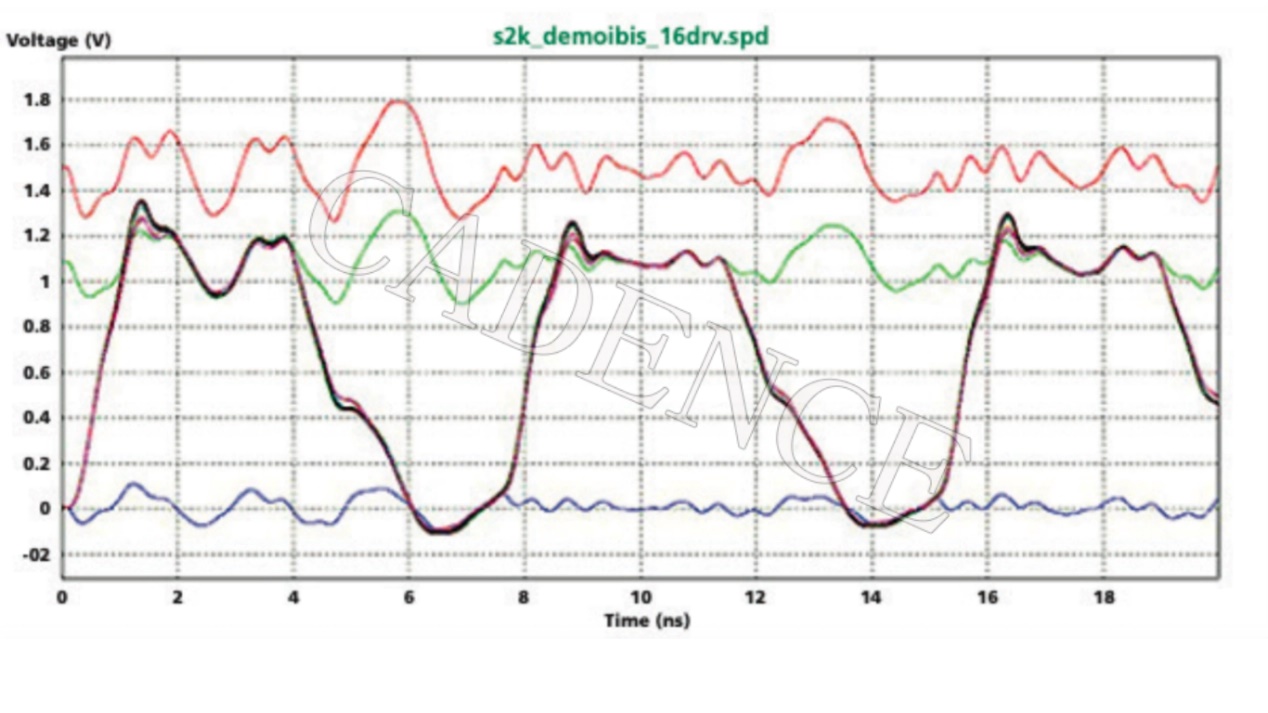

Dès 2005, le concept de «prendre en compte l'influence de l'alimentation électrique» a fait ses débuts pour la première fois. Il s'agit d'une méthode avancée de simulation d'intégrité du signal qui peut analyser les signaux et le bruit de puissance en même temps (figure 1).La solution d'intégrité du signal qui prend en compte l'influence de l'alimentation doit tenir compte de la réflexion, du corde, des effets séquentiels et d'autres, et équipés de techniques de simulation et d'inspection des règles correspondantes.Il convient de noter que pour mettre en œuvre efficacement la simulation d'intégrité du signal qui prend en compte l'impact de l'alimentation, il est nécessaire de fonctionner dans la phase d'analyse après une inspection et un câblage réguliers, car l'interaction / couplage du plan et du signal se produit Une fois le câblage terminé.

Par conséquent, une solution complète qui prend en compte l'influence de l'alimentation électrique doit souvent être fournie:

l Un ensemble de solutions d'inspection rapide pour l'atténuation du signal et l'alimentation électrique sur les signaux

l peut simuler le simulateur de domaine temporel de grands circuits (les résultats de plusieurs réseaux de signaux et réseaux électriques)

L Réseau d'alimentation et modélisation du réseau de signaux

L Modélisation de tampon entrée / sortie (E / S) de niveau élevé

Figure 1: Le résultat de l'intégrité du signal de l'influence de l'alimentation

Bien que de nombreux outils sur le marché prennent en charge les normes de modélisation d'E / S de base qui prennent en compte l'influence de l'alimentation électrique, avec le développement continu de la technologie d'interface mémoire, les exigences du marché pour les outils d'intégrité du signal augmentent également. L'outil d'extraction précis pour le Le signal de couplage, l'alimentation et le signal de terre sur PCB sont rares.

À cet égard, en tant qu'entreprise de premier plan dans le domaine de la simulation EDA, la technologie Sigrity X lancée par Cadence fournit une analyse d'intégrité du signal de l'influence de l'alimentation électrique pour DDR4 et DDR5.

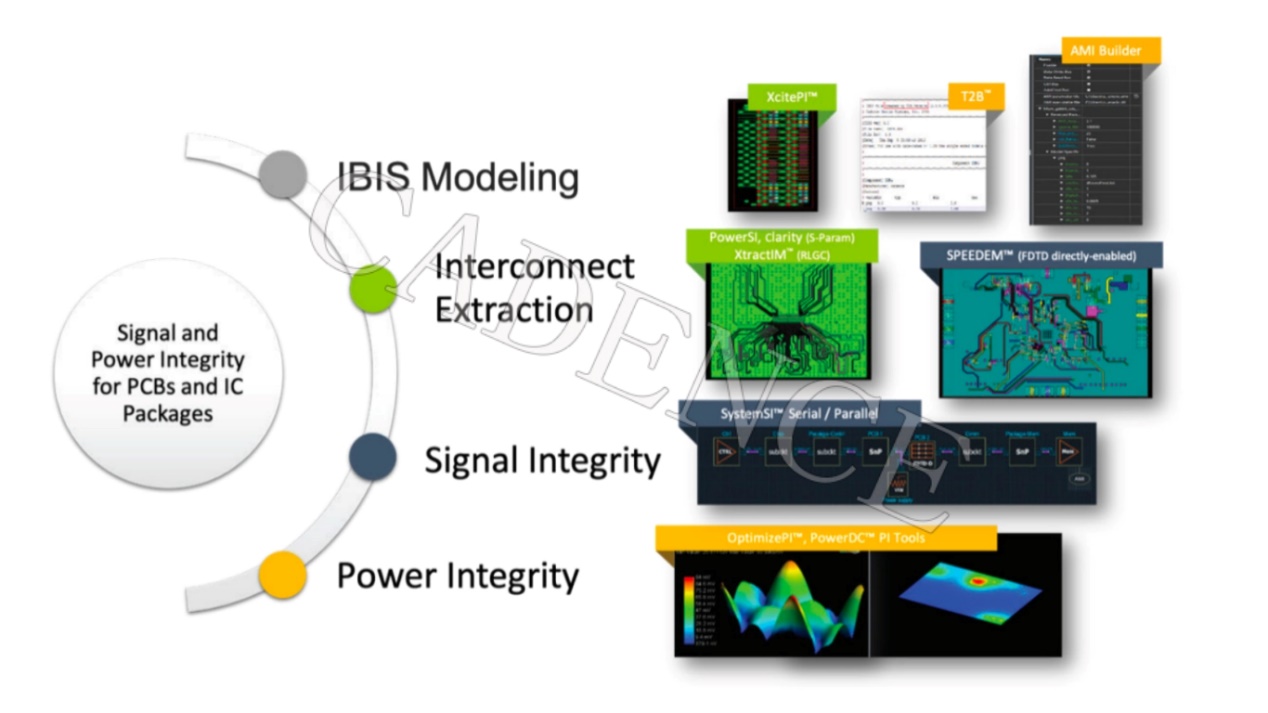

La technologie Sigrity X réalise non seulement l'extraction précise des signaux couplés, de l'alimentation et des signaux de sol sur les puces, l'emballage et la PCB, mais peut également faire une simulation efficace sur la réflexion, la perte, le bandes et la sortie de commutation synchrone (SSO) à la même temps.Les concepteurs utilisant la technologie de sigrity peuvent rapidement convertir le modèle de niveau transistor en un modèle IBIS de niveau comportemental qui considère l'influence de la puissance, de sorte qu'en quelques heures, elle peut fournir une grandeur précise, efficace et complète en considérant la simulation des effets de l'alimentation électrique, qui grandement raccourcit le nombre d'origine d'origine doit être numéroté. Cycle de conception du ciel.(Figure 2)

Figure 2: Intégrité du signal de cadence et outil d'intégrité de la puissance pour PCB et emballage IC

La technologie Sigrity X simplifie le flux de travail, fournit une simulation synchrone de conception et la précision du niveau de signature pour la vérification finale.Les signaux, les problèmes de puissance et de chaleur peuvent être résolus à chaque étape de conception, réduisant ainsi le nombre d'itérations entre les équipes de conception et d'analyse.Les concepteurs peuvent gérer le moteur de niveau nucléaire dans la conception du tissu de dessin pour une simulation à haute provision, fournissant ainsi une conception de haute qualité pour les équipes d'analyse à vérifier.Plus tard, l'équipe d'analyse a utilisé le moteur de simulation parallèle à grande échelle de la smigrité pour faire une simulation complète du système pour garantir que l'ensemble de la "Shell de PCB-PCB de puce" répond aux spécifications de conception et se prépare à la signature.

Ces avantages font de Sigrity X la meilleure solution pour la mémoire DDR5 et l'interface 112G.Sa modélisation d'interconnexion standard en or combine la simulation du domaine temporel (circuit et simulation de canaux) de l'analyse en série / solution (Serdes) et en soutenant l'interface de modélisation de l'algorithme IBIS (AMI), qui offre des avantages uniques de cadence, peut ainsi extraire et interface la signature de la conformité à la conformité fourni Compléter les solutions.

En outre, la technologie Sigrity Xtracttim et Clarity 3D Solver peut être utilisée en conjonction, qui permet aux ingénieurs de créer des modèles d'emballage complets contenant des signaux de couplage, de l'alimentation et des modèles d'interconnexion de mise à la terre pour divers types d'emballage, qui compensent efficacement la conception de l'emballage et les caractéristiques des emballages L'écart entre.

De plus, la technologie Sigrity SystemsI prend en charge le modèle IBIS qui peut rapidement se connecter à l'influence de l'alimentation électrique et du modèle d'interconnexion qui prend en compte l'influence de l'alimentation électrique. Le concepteur peut rapidement déterminer la pire situation grâce à cette technologie et la comparer avec le Norme JEDEC pour garantir que DDR4 / DDR5 l'interface (y compris les exigences de taux de code sans bit) répond à toutes les spécifications pertinentes.

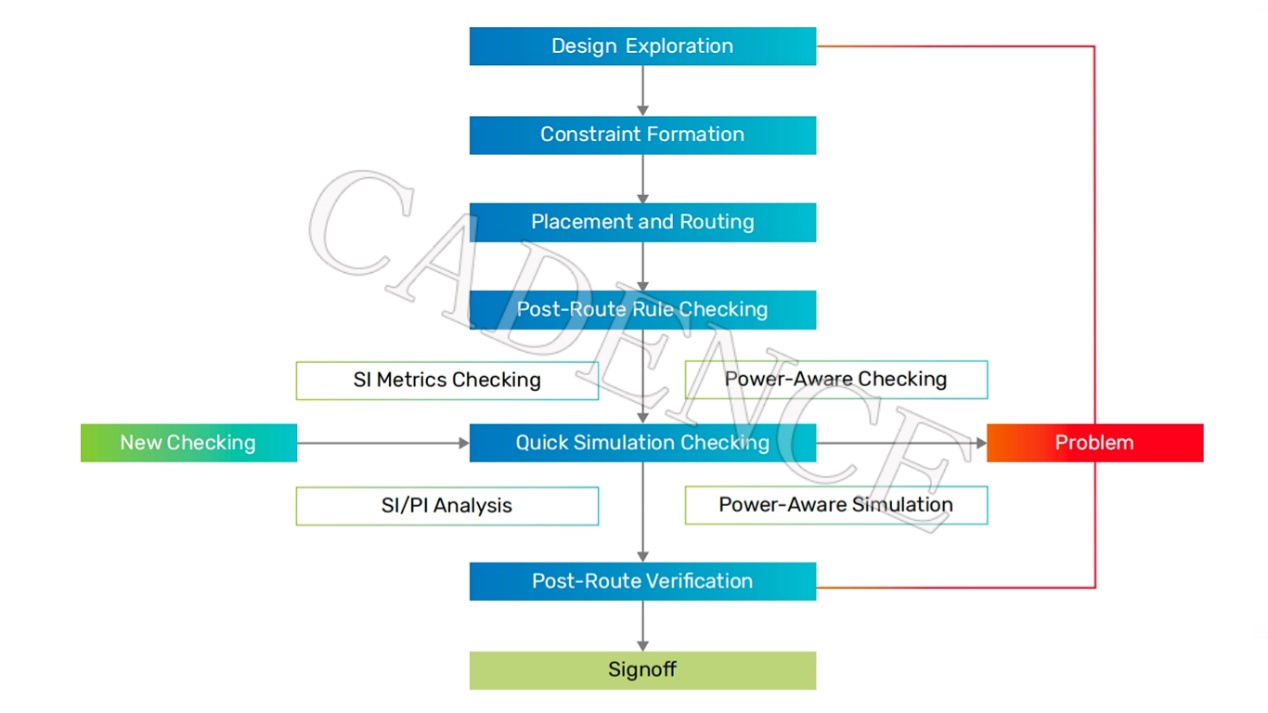

La figure 3 est le processus d'inspection et de simulation qui prend en compte l'influence de l'alimentation, qui contraste fortement avec le processus de conception traditionnel axé sur les contraintes (figure 4).Le processus de conception des conducteurs de contraintes traditionnels comprend principalement quatre parties: le câblage avant la mise en place, la formation de contraintes, l'inspection des règles et la vérification du poste de portail.

Figure 3: Cadence prend en compte le processus du conducteur de contrainte de l'influence de l'alimentation

CONTRE

Figure 4: Exemple du processus de conception du pilote de contrainte traditionnel

Parmi les nombreuses technologies de simulation actuelles, il existe souvent des déconnexions entre l'analyse du signal et le réseau de distribution de puissance (PDN), et il existe d'autres lacunes.Dans des circonstances normales, selon la complexité du modèle d'épices, utilisez parfois la simulation du domaine temporel pour générer des modèles précis de résistance / inductance / condensateurs (RLC), et parfois il assume un plan de sol idéal.Le modèle de domaine temporel obtenu à partir de ceci est basé sur la réponse de fréquence simple d'extraction de simulation. Bien qu'elle soit plus pratique, elle est légèrement insuffisante en termes de précision. Pour les fréquences plus élevées, les ingénieurs utiliseront les paramètres S créés par un dispositif de résolution mixte.

En fait, il existe également une méthode efficace pour combiner la méthode du domaine temporel de différence limité (FDTD) avec le dispositif de résolution mixte pour étendre la couverture au signal, à l'alimentation et à la ligne de mise à la terre.

Le cas de pratique réussi de cette méthode est l'outil de moteur Sigrity Speed2000 de Cadence. Il intègre et intègre la sortie de plusieurs solutions pour résoudre le câblage du circuit, les lignes de transmission et les problèmes de champ électromagnétique, et peut mieux afficher les données et l'interaction du plan d'alimentation / sol à différents fois.Et utilisez la méthode FDTD pour analyser la disposition de l'emballage IC et du PCB.Il fournit une base de référence importante pour l'optimisation supplémentaire de la conception du circuit.

Lors de l'entrée de la phase de signature finale, les ingénieurs ont généralement tendance à utiliser des méthodes de modélisation des ondes complètes 3D pour obtenir une précision plus élevée.Mais cela consommera plus de ressources informatiques et augmentera le temps de simulation.Pour atténuer ce problème, la technologie de division et de parallélisation peut être adoptée.À cet égard, en utilisant le solveur Clarity 3D pour une analyse d'analyse des éléments finis (FEM), puis en combinant la technologie Sigrity Xtracttim, les résultats de chaque analyse sont ré-combinés pour former un modèle de paramètre S basé sur une réponse en fréquence, réalisant ainsi le Système entier à l'ensemble du système ou en profondeur et une analyse précise de la conception.

Résumer

En même temps que le saut technologique, la technologie a été améliorée et il est inévitable de poser de nouveaux défis pour les concepteurs.Sur le chemin de la mémoire DDR5 et de nouveaux défis, avec la "lame tranchante" nette de Cadence Sigrity X, les ingénieurs peuvent calmement faire face aux problèmes complexes de l'intégrité du signal, en veillant à ce que le produit ne soit pas seulement cohérent avec les spécifications. Performance, ajoutant une autre brique à la route de l'innovation future.