Informações

A era DDR5 está se aproximando e novos desafios não podem ser ignorados

- Autor:ROGER

- Lançamento em:2023-12-04

No frenesi da inteligência artificial (IA), do aprendizado de máquina (ML) e da mineração de dados, nosso desejo de processamento de dados mostra um crescimento sem precedentes do índice.Enfrentando essa perspectiva, a largura da largura de banda da memória se tornou uma "artérias" importantes na era digital.Entre eles, a tecnologia DDR (Taxa de Dados Duplo), conhecida por taxas de transmissão de dados duplas e maior largura de banda como uma memória dinâmica de acesso aleatório (DRAM), promoveu bastante a melhoria do desempenho do computador.Desde o nascimento da primeira geração de tecnologia DDR em 2000, até o DDR5 em 2020, cada geração de tecnologia DDR alcançou melhorias significativas em vários aspectos, como largura de banda, desempenho e consumo de energia.

Hoje, seja PC, laptop ou inteligência artificial, várias indústrias estão se acelerando para avançar em direção à nova era do DDR5.Este ano, o mercado de IA de geração está crescendo e os servidores de IA usados em aplicativos de modelo grandes promoveram vigorosamente a demanda por DDR5.Com a recuperação da demanda por mercado de memória, os fornecedores de chip de memória mostraram a capacidade de produção do DDR5 no quarto trimestre deste ano para substituir gradualmente o DDR4 atual.

A nova era do DDR5 chegou, no entanto, alguns desafios também impediram o desenvolvimento adicional da indústria.

ERA DDR5: Desafios de design por trás do desempenho Ultra -High -Speed

Em julho de 2020, o padrão de tecnologia de memória DDR5 foi lançado oficialmente, marcando que a tecnologia de memória abriu um novo capítulo.O DDR5 atraiu atenção generalizada com maior largura de banda e desempenho.Comparado com o DDR4 anterior, a maior vantagem do DDR5 é que ele reduziu significativamente o consumo de energia e dobrou a largura de banda.Especificamente, a maior taxa do protocolo de liberação atual do DDR5 atingiu 6.4 GbpsA frequência do relógio também aumentou de 1,6 GHz para 3,2 GHz.

Quando exploramos mais detalhes do DDR5, também descobrimos que essa nova tecnologia trouxe alguns desafios técnicos adicionais.Por exemplo, a tensão da fonte de alimentação do DDR5 diminui em 0,1V em 1,2V do DDR4, atingindo 1,1V. Embora a menor tensão da fonte de alimentação reduz o consumo de energia e estenda a duração da bateria, também traz alguns desafios técnicos, como tal, como técnico Desafios, como tal, desafios técnicos, como, como alguns desafios técnicos, como, como alguns desafios técnicos, como, como alguns desafios técnicos, como, como alguns desafios técnicos, como, como como Alguns desafios técnicos, como, como desafios técnicos, como alguns desafios técnicos. Por exemplo, é mais provável que seja perturbado pelo ruído, o que torna a integridade do sinal mais desafiadora, porque a quantidade de ruído entre a tensão Entre a tensão durante o interruptor do sinal é menor e pode afetar o projeto.

Outra grande mudança de DDR5 é diferente da maneira como o chip de gerenciamento de energia (PMIC) do DDR4 é integrado na placa -mãe. O DDR5 transferiu o IC de gerenciamento de energia (PMIC) da placa -mãe para o módulo de memória direta de coluna dupla (DIMM).Isso permite o gerenciamento de energia, a regulação de tensão e a sequência de potência -na sequência física mais próxima do dispositivo de armazenamento no módulo, o que também ajuda a garantir a integridade da fonte de alimentação (PI) e aprimorar o controle do método de operação PMIC.

Além disso, quando o número total de bits de dados permanece inalterado, o número de canais DIMM de 1 canal para 2 canais também é um progresso importante. Ao transmitir dados em duas transmissão estreita de canal, ele pode ser gerado com mais eficácia e gerado com mais eficiência Sinais de relógio para melhorar a integridade do sinal.

Obviamente, o desenvolvimento do padrão DDR5 também levou em consideração o problema de integridade do sinal, e a transferência de PMIC para o módulo também exercerá as vantagens correspondentes.No entanto, os designers ainda precisam considerar o efeito geral da integridade do sinal da fonte de alimentação.Como mencionado acima, o DDR5 possui uma taxa de dados de até 6,4 Gbps e a frequência do relógio do sistema de 3,2 GHz. O ruído de energia pode causar problemas mais óbvios nesta operação de alta velocidade, o que afetará o desempenho e a estabilidade do sistema.Se a integridade de energia e a integridade do sinal forem analisadas separadamente, o problema do ruído da fonte de alimentação poderá ser perdido.

Portanto, para dar jogo completo ao desempenho do DDR5, todos os pontos -chave do sistema devem incluir chips, embalagens e PCB para análise de integridade do sinal da influência da fonte de alimentação.No entanto, a análise desse nível é uma tarefa complexa. Possui altos requisitos para as ferramentas de hardware e software usadas para análise de simulação para a plataforma de computação subjacente. A dificuldade e a complexidade do design.

Libere totalmente o potencial do DDR5, Cadence

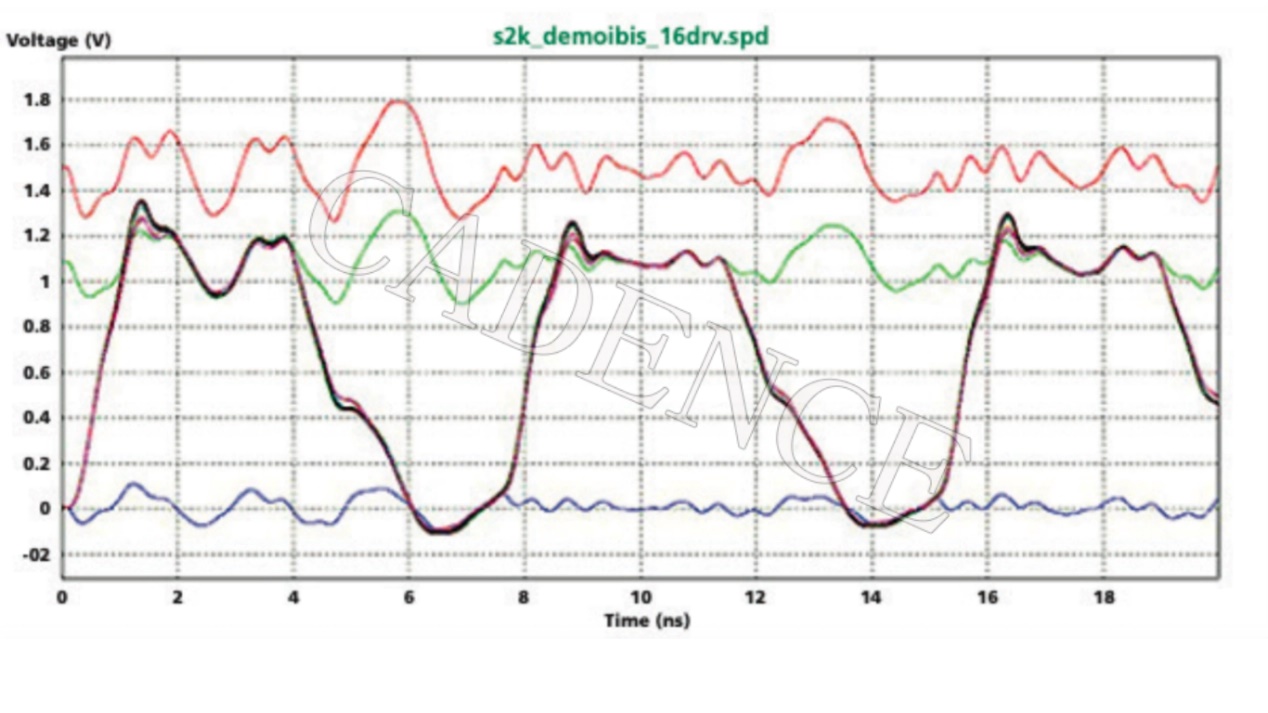

Já em 2005, o conceito de "levar em consideração a influência da fonte de alimentação" estreou pela primeira vez. É um método avançado de simulação de integridade de sinal que pode analisar sinais e ruído de energia ao mesmo tempo (Figura 1).A solução de integridade do sinal que leva em consideração a influência da fonte de alimentação deve considerar a reflexão, a cordas, os efeitos sequenciais e outros e equipados com as técnicas correspondentes de simulação e inspeção de regras.Vale a pena notar que, para implementar efetivamente a simulação de integridade do sinal que leva em consideração o impacto da fonte de alimentação, é necessário executar na fase de análise após inspeção e fiação regulares, porque a interação/acoplamento do plano e o sinal ocorre Após a conclusão da fiação.

Portanto, uma solução completa que leva em consideração a influência da fonte de alimentação geralmente precisa ser fornecida:

l Um conjunto de soluções de inspeção rápida para atenuação de sinal e fonte de alimentação em sinais

l pode simular o simulador de domínio de tempo de grandes circuitos (os resultados de múltiplas redes de sinais e redes de energia)

L Rede de energia e modelagem de rede de sinais

l Modelagem de buffer de entrada/saída de alto nível (E/S)

Figura 1: o resultado da integridade do sinal da influência da fonte de alimentação

Embora muitas ferramentas no mercado apóiam os padrões básicos de modelagem de E/S que levam em consideração a influência da fonte de alimentação, com o desenvolvimento contínuo da tecnologia da interface de memória, os requisitos do mercado para ferramentas de integridade de sinal também estão aumentando. A ferramenta de extração precisa para o O sinal de acoplamento, a fonte de alimentação e o sinal do solo no PCB são raros.

Nesse sentido, como uma empresa líder no campo da simulação da EDA, a tecnologia Sigrity X lançada pela Cadence fornece uma análise de integridade do sinal da influência da fonte de alimentação para DDR4 e DDR5.

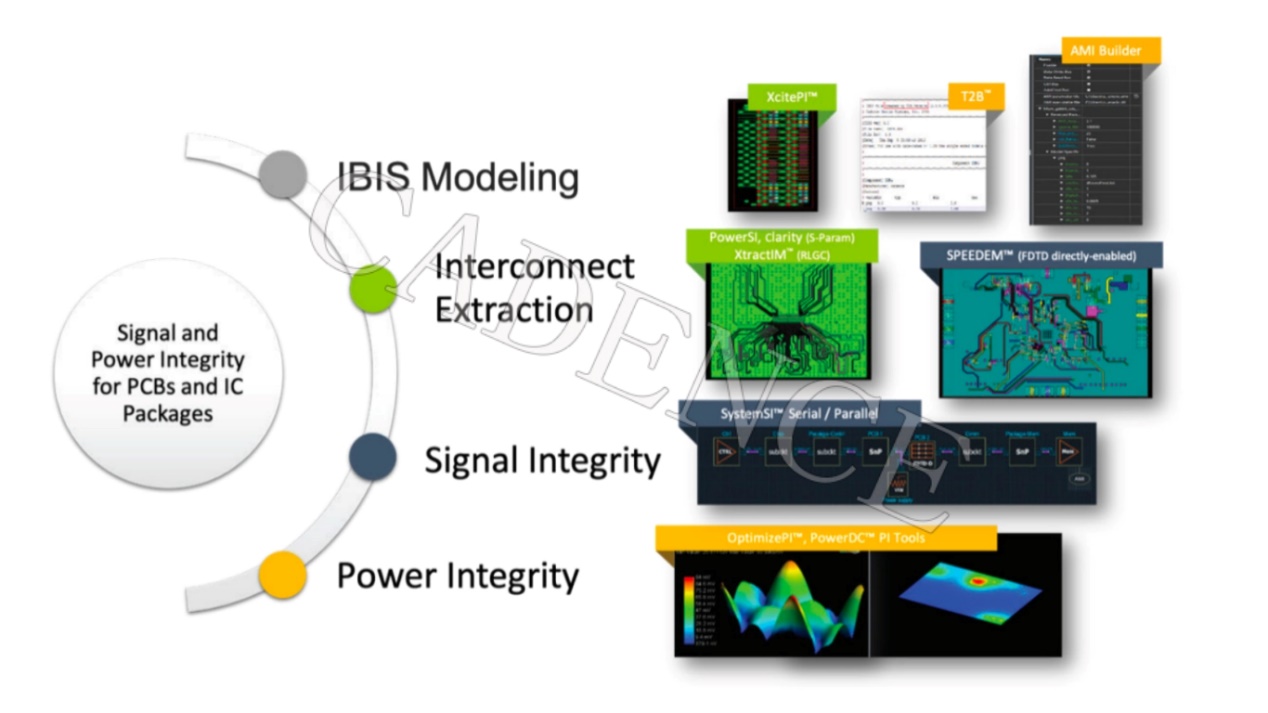

A tecnologia Sigrity X não apenas percebe a extração precisa de sinais acoplados, fonte de alimentação e sinais de solo em batatas fritas, embalagens e PCB, mas também pode fazer simulação eficiente sobre efeitos de reflexão, perda, bandidal e síncrona (SSO) no mesmo tempo.Os designers que usam a tecnologia de sigridade podem converter rapidamente o modelo de nível de transistor em um modelo de Ibis de nível comportamental que considera a influência do poder, de modo que, em poucas horas, pode fornecer precisão, eficiente e abrangente, considerando a simulação de efeitos da fonte de alimentação, que muito Encurta o número original de originalmente precisa ser numerado. Ciclo de design do céu.(Figura 2)

Figura 2: Ferramenta de integridade e integridade de energia da cadência para embalagens de PCB e IC

A tecnologia Sigrity X simplifica o fluxo de trabalho, fornece simulação síncrona de design e a precisão do nível de assinatura para a verificação final.Sinais, poder e problemas de calor podem ser resolvidos em cada estágio de design, reduzindo assim o número de iterações entre as equipes de design e análise.Os designers podem executar o motor de nível nuclear no design do pano de desenho para simulação de alta precisão, fornecendo assim o design de alta qualidade para as equipes de análise verificar.Posteriormente, a equipe de análise usou o mecanismo de simulação paralelo em larga escala da Sigrity para fazer simulação completa do sistema para garantir que toda a "pica-papo-pcb-shell" atenda às especificações do projeto e se prepare para a assinatura.

Essas vantagens tornam o SIGRITY X a melhor solução para a memória DDR5 e a interface 112G.Sua modelagem de interconexão padrão de ouro combina a simulação de domínio do tempo (simulação de circuito e canal) da análise serial/solução (SERDES) e apoiando a interface de modelagem do algoritmo IBIS (AMI), que fornece vantagens únicas de cadência, assim pode extrair e a sinalização de conformidade com interface fornece fornece soluções completas.

Além disso, a tecnologia Sigrity Xtractim e Clarity 3D Solver pode ser usada em conjunto, o que permite que os engenheiros criem modelos completos de embalagens contendo sinais de acoplamento, fonte de alimentação e modelos de interconexão de aterramento para vários tipos de embalagens, que efetivamente compensam o design da embalagem e as características de design da embalagem e do pacote O espaço entre.

Além disso, a tecnologia SIGRITY Systemsi suporta o modelo IBIS que pode se conectar rapidamente à influência da fonte de alimentação e ao modelo de interconexão que leva em consideração a influência da fonte de alimentação. O designer pode determinar rapidamente a pior situação através dessa tecnologia e compará -la com o Jedec Standard para garantir que DDR4/DDR5 a interface (incluindo os requisitos de taxa de código sem bits) atenda a todas as especificações relevantes.

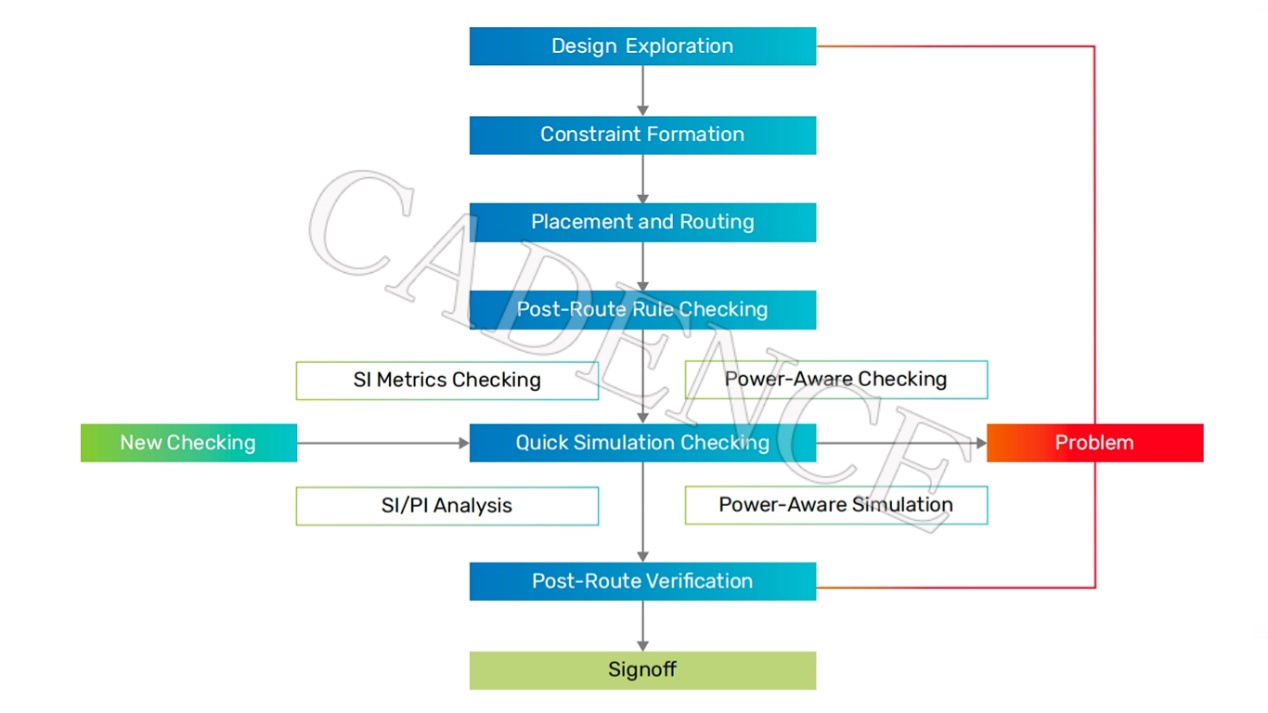

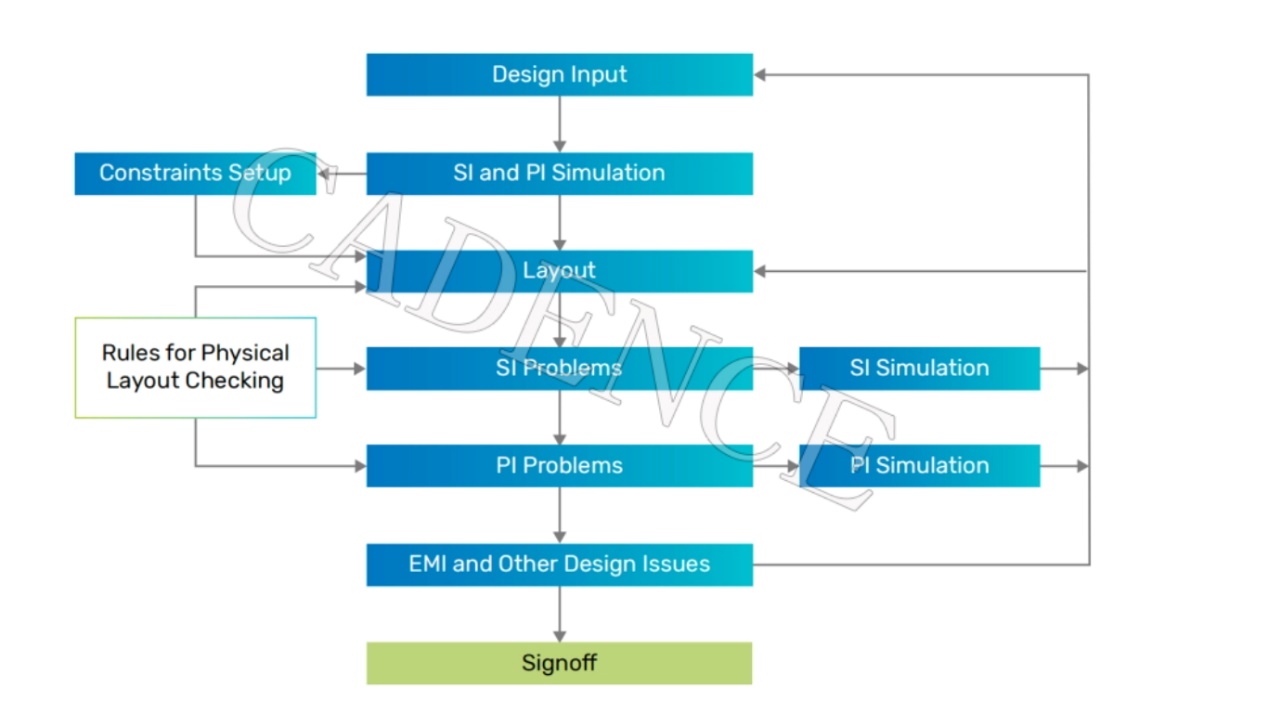

A Figura 3 é o processo de inspeção e simulação que leva em consideração a influência da fonte de alimentação, que contrasta nítido com o processo de projeto orientado a restrições tradicional (Figura 4).O processo de design dos drivers de restrição tradicional inclui principalmente quatro partes: fiação pré -layout, formação de restrições, inspeção de regras e verificação pós -relativa.

Figura 3: Cadência leva em consideração o processo de restrição de fator de influência da fonte de alimentação

Vs.

Figura 4: Exemplo do processo de design de driver de restrição tradicional

Entre as muitas tecnologias atuais de simulação, muitas vezes há desconexão entre a análise de sinal e a rede de distribuição de energia (PDN) e existem outras deficiências.Em circunstâncias normais, de acordo com a complexidade do modelo de especiarias, às vezes usa a simulação de domínio de tempo para gerar modelos precisos de resistência/indutância/capacitores (RLC) e, às vezes, assume um plano de aterramento ideal.O modelo de domínio de tempo obtido com isso é baseado na resposta simples de frequência da extração de simulação. Embora seja mais conveniente, é um pouco insuficiente em termos de precisão. Para frequências mais altas, os engenheiros usarão os parâmetros S criados por um dispositivo de solução mista.

De fato, também existe um método eficiente para combinar o método de domínio do tempo de diferença limitado (FDTD) com o dispositivo de solução mista para expandir a cobertura para sinalizar, fonte de alimentação e linha de aterramento.

O caso de prática bem -sucedida desse método é a ferramenta de motor Speed2000 da Cadence Speed2000. Ele integra e integra a saída de várias soluções para resolver a fiação do circuito, linhas de transmissão e problemas de campo eletromagnético, e pode exibir melhor a interação de dados e energia/plano de solo em diferentes diferentes vezes.E use o método FDTD para analisar o layout da embalagem do IC e da PCB.Ele fornece uma base de referência importante para a otimização adicional do projeto do circuito.

Ao entrar no estágio final de assinatura, os engenheiros geralmente tendem a usar métodos de modelagem de ondas completas 3D para obter maior precisão.Mas isso consumirá mais recursos de computação e aumentará o tempo de simulação.Para aliviar esse problema, a tecnologia de divisão e paralelização pode ser adotada.Nesse sentido, usando o solucionador Clarity 3D para uma análise de análise de elementos finitos (FEM) e, em seguida, combinando a tecnologia sigridade xtractim, os resultados de cada análise são recolocados para formar um modelo de parâmetro S baseado na resposta de frequência, alcançando assim o Sistema inteiro para todo o sistema ou em análise de aprovação e profundidade do projeto.

Resumir

Ao mesmo tempo que o salto tecnológico, a tecnologia foi aprimorada e é inevitável dar novos desafios para os designers.No caminho para a memória DDR5 e novos desafios, com a "lâmina afiada" da cadência sigridade X, os engenheiros podem lidar com os problemas complexos da integridade do sinal, garantindo que o produto não seja apenas consistente com as especificações. Ele também brilha em Desempenho, adicionando outro tijolo ao caminho da inovação futura.