hírek

A DDR5 korszak közeledik, és az új kihívásokat nem lehet figyelmen kívül hagyni

- Szerző:ROGER

- Engedje fel:2023-12-04

A mesterséges intelligencia (AI), a gépi tanulás (ML) és az adatbányászat őrületében az adatfeldolgozás iránti vágyunk példátlan index növekedést mutat.Ezzel a kilátással szembesülve a memória sávszélességének szélessége kulcsfontosságú "artériákká" vált a digitális korban.Közülük a DDR (kettős adatsebesség) technológia, amely a kettős adatátviteli sebességről és a nagyobb sávszélességről ismert, mint egy dinamikus véletlenszerű hozzáférésű memória (DRAM), jelentősen elősegítette a számítógépes teljesítmény javulását.A DDR technológia első generációjának 2000 -es születésétől kezdve a DDR5 -ig 2020 -ban a DDR technológia minden generációja jelentős javulást ért el különféle szempontokban, például a sávszélességben, a teljesítményben és az energiafogyasztásban.

Ma, akár PC, laptop, akár mesterséges intelligencia, a különféle iparágak felgyorsulnak, hogy a DDR5 új korszaka felé mozogjanak.Ebben az évben az AI generációs piac virágzik, és a nagy modell -alkalmazásokban használt AI szerverek erőteljesen előmozdították a DDR5 iránti keresletet.A memória -piac iránti kereslet visszanyerésével a memória chip -beszállítói megmutatták a DDR5 termelési kapacitását az év negyedik negyedévében, hogy fokozatosan helyettesítsék az aktuális DDR4 -et.

Megérkezett a DDR5 új korszaka, néhány kihívás azonban akadályozta az ipar további fejlődését is.

DDR5 ERA: A tervezési kihívások az ultra -magassebességű teljesítmény mögött

2020 júliusában a DDR5 memóriatechnológiai szabványt hivatalosan kiadták, jelezve, hogy a memória technológiája új fejezetet nyitott.A DDR5 széles körű figyelmet fordított a nagyobb sávszélességgel és a teljesítménygel.Az előző DDR4 -hez képest a DDR5 legnagyobb előnye, hogy jelentősen csökkentette az energiafogyasztást és megduplázta a sávszélességet.Pontosabban, elérte a DDR5 jelenlegi kiadási protokolljának legmagasabb arányát 6.4 GbpsAz órafrekvencia szintén 1,6 GHz -ről 3,2 GHz -re nőtt.

Amikor a DDR5 további részleteit vizsgáljuk, azt is megállapítjuk, hogy ez az új technológia további technikai kihívásokat hozott.Például a DDR5 tápegység feszültsége 0,1 V -rel 1,2 V -rel csökken a DDR4 -től, elérve az 1,1 V -ot olyan kihívások, mint például a műszaki kihívások, például néhány műszaki kihívás, például néhány technikai kihívás, például néhány technikai kihívás, például néhány műszaki kihívás, például például Néhány technikai kihívás, például a műszaki kihívások, például, például néhány technikai kihívás A feszültség között a jelkapcsoló kevesebb, és befolyásolhatja a kialakítást.

A DDR5 másik jelentős változása különbözik attól, ahogyan a DDR4 energiagazdálkodási chip (PMIC) integrálódik az alaplapra. A DDR5 átadta az energiagazdálkodási IC -t (PMIC) az alaplapról a Dual -Column Direct Memory modulba (DIMM).Ez lehetővé teszi az energiagazdálkodást, a feszültségszabályozást és az energia -szekvenciát a modul tárolóeszközéhez való fizikai közelebbről, amely szintén elősegíti a tápegység integritását (PI) és javítja a PMIC működési módszer vezérlését.

Ezenkívül, ha az adatbitek teljes száma változatlan marad, akkor az 1 -csatorna és 2 csatorna közötti DIMM -csatornák száma szintén fontos előrelépés. Az adatok két keskeny csatorna -átvitelre történő továbbításával hatékonyabban előállíthatók és hatékonyabban hozzárendelhetők. Órajelek a jel integritásának javítása érdekében.

Nyilvánvaló, hogy a DDR5 szabvány fejlődése szintén figyelembe vette a jel integritási problémáját, és a PMIC átadása a modulhoz a megfelelő előnyöket is gyakorolja.A tervezőknek azonban továbbra is figyelembe kell venniük az áramellátás jel integritásának általános hatását.Mint fentebb említettük, a DDR5 adatsebessége akár 6,4 Gbps -ig terjedhet, és a 3,2 GHz -es rendszer óra frekvenciája. Az energiazaj nyilvánvalóbb problémákat okozhat ebben a nagysebességű műveletben, ami befolyásolja a rendszer teljesítményét és stabilitását.Ha a teljesítmény integritását és a jel integritását külön -külön elemezzük, akkor az áramellátás zajának problémája elmaradható.

Ezért annak érdekében, hogy teljes mértékben lejátsszák a DDR5 teljesítményét, a rendszer minden kulcsfontosságú pontjának tartalmaznia kell a chipeket, a csomagolást és a PCB -t a jel integritásának elemzéséhez az energiaellátás befolyásáról.Ennek a szintnek az elemzése azonban összetett feladat. Magas követelményei vannak a hardver- és szoftver eszközökre, amelyeket a mögöttes számítási platform szimulációs elemzéséhez használtak. A tervezés nehézsége és összetettsége.

Teljesen engedje el a DDR5, Cadence potenciálját

Már 2005 -ben először debütált az a fogalom, hogy "figyelembe vesszük az áramellátás befolyását".A jelző integritási megoldásnak, amely figyelembe veszi az áramellátás befolyását, figyelembe kell vennie a reflexiót, a húrokat, a szekvenciális és egyéb hatásokat, valamint a megfelelő szimulációs és szabályok ellenőrzési technikáival felszerelve.Érdemes megjegyezni, hogy annak érdekében, hogy hatékonyan megvalósítsuk a jel integritási szimulációját, amely figyelembe veszi a tápegység hatását, a rendszeres ellenőrzés és a vezetékek utáni elemzési szakaszban kell végrehajtani, mivel a sík és a jel interakciója/összekapcsolása megtörténik A vezeték befejezése után.

Ezért gyakran kell biztosítani egy teljes megoldást, amely figyelembe veszi az áramellátás hatását:

l Gyors ellenőrzési megoldások halmaza a jelcsillapításhoz és a jelek tápegységéhez

l szimulálhatja a nagy áramkörök időtartomány -szimulátorát (több jelzőhálózat és energiatartalmú hálózatok eredményei)

L Power Network és Signal Network modellezés

L magas szintű bemeneti/kimenet (I/O) puffermodellezés

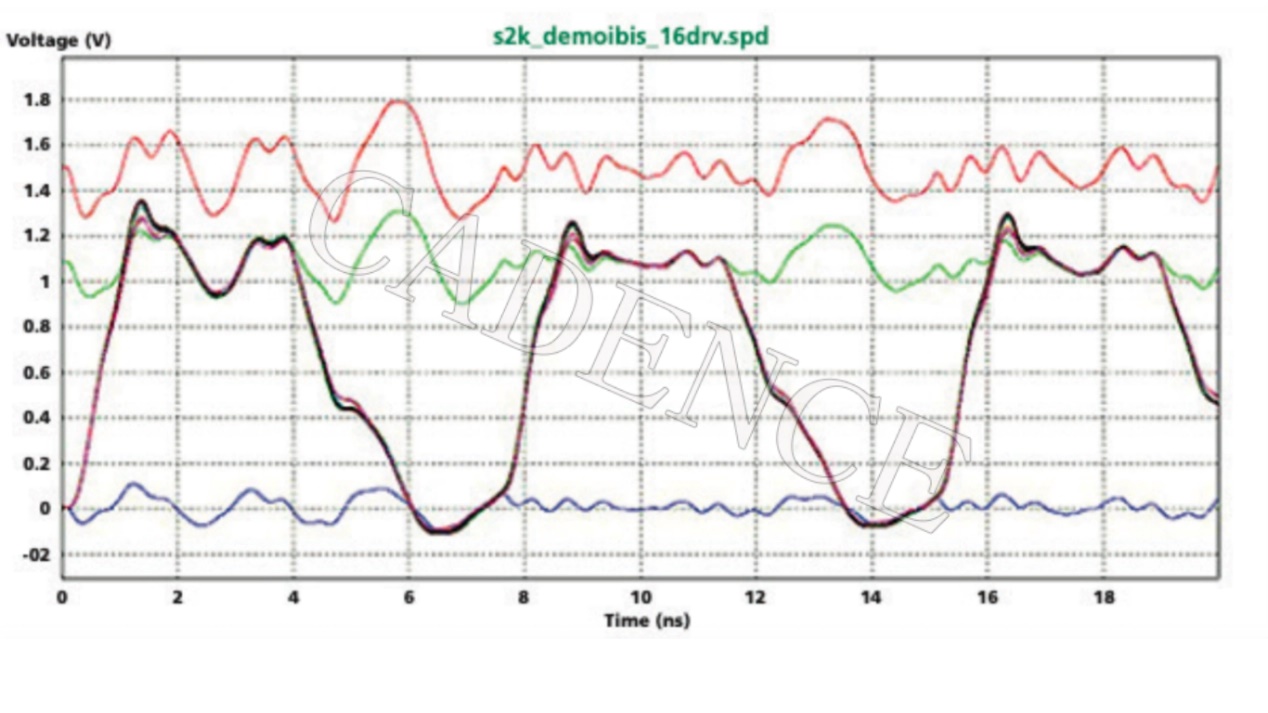

1. ábra: A tápegység mindkét hatása jel integritásának eredménye

Bár a piacon számos eszköz támogatja az alapvető I/O modellezési szabványokat, amelyek figyelembe veszik az áramellátás hatását, a memória interfész technológiájának folyamatos fejlesztésével, a piac jelzési eszközökre vonatkozó követelményei is növekszenek. A kapcsolójel, a tápegység és a PCB földi jele ritka.

Ebben a tekintetben, mint az EDA szimuláció területén vezető vállalkozás, a Cadence által indított Sigrity X technológia jel integritási elemzést nyújt a DDR4 és a DDR5 tápegységének befolyásáról.

A Sigrity X technológia nem csak a kapcsolt jelek, az energiaellátás és a talajjelek pontos kinyerését veszi észre a chipsen, a csomagoláson és a PCB -n, hanem hatékony szimulációt is végezhet a reflexió, a veszteség, a bandidal és idő.A Sigrity technológiát használó tervezők gyorsan átalakíthatják a tranzisztorszintű modellt viselkedési szintű IBIS modellré, amely figyelembe veszi a hatalom befolyását, így néhány órán belül pontos, hatékony, és átfogó, figyelembe véve az energiaellátási effektusok szimulációját, amelyek nagymértékben nagyban lerövidíti az eredetileg számozású eredeti számot. Sky Design Cycle.(2. ábra)

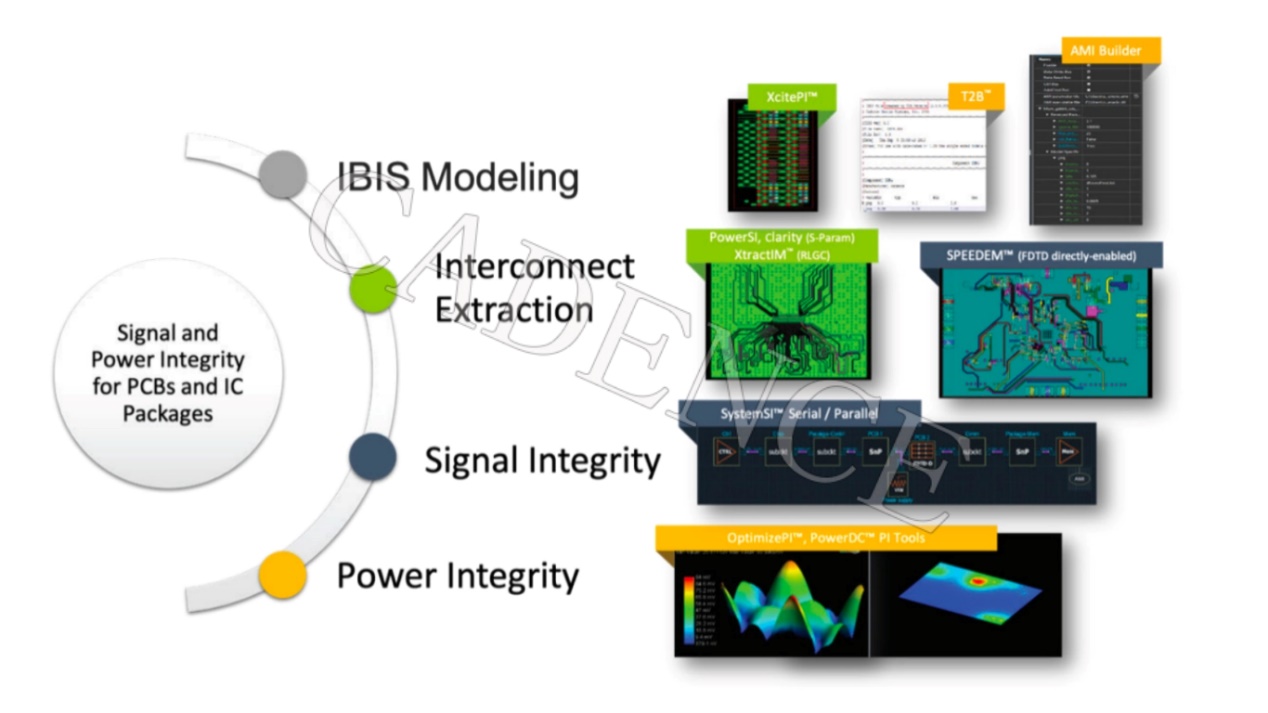

2. ábra: A Cadence Signal integritása és az energia integritási eszköze a PCB és az IC csomagoláshoz

A Sigrity X technológia leegyszerűsíti a munkafolyamatot, biztosítja a tervezési szinkron szimulációt és az aláírási szint pontosságát a végső ellenőrzéshez.A jelek, az erő és a hőproblémák minden tervezési szakaszban megoldhatók, ezáltal csökkentve a tervező és elemző csoportok közötti iterációk számát.A tervezők a nukleáris szintű motort futtathatják a rajzszövet kialakításában a nagy pontosságú szimulációhoz, ezáltal nagy minőségű kialakítást biztosítva az elemző csapatok számára.Később az elemzőcsoport a Sigrity nagyszabású párhuzamos szimulációs motorját a teljes rendszer szimulációjának elkészítéséhez használta annak biztosítása érdekében, hogy a teljes "chip-csomagolás-PCB-héj" megfeleljen a tervezési előírásoknak, és felkészüljön az aláírásra.

Ezek az előnyök miatt a Sigrity X a legjobb megoldás a DDR5 memória és a 112G interfész számára.Arany standard összekapcsolási modellezése ötvözi a soros/megoldás (SERDES) elemzési tartomány szimulációját (áramköri és csatorna -szimulációját), és támogatja az IBIS algoritmus modellezési felületét (AMI), amely egyedi előnyöket ad a Cadence -nak, ezáltal kivonhatja és az interfész -megfelelés aláírása biztosítja az aláírást. Teljes megoldások.

Ezenkívül a Sigrity Xractim és a Clarity 3D Solver technológia együttesen használható, amely lehetővé teszi a mérnökök számára, hogy teljes csomagolási modelleket készítsenek, amelyek összekapcsolási jeleket, tápegységeket és földelő összekapcsolási modelleket tartalmaznak a különféle csomagoláshoz, amelyek hatékonyan pótolják a csomagolási tervezést és a csomagok jellemzőit. A rés között.

Ezenkívül a Sigrity Systemsi Technology támogatja az IBIS modellt, amely gyorsan kapcsolódhat az áramellátás és az összekapcsolási modell befolyásához, amely figyelembe veszi a tápegység befolyását. A tervező gyorsan meghatározhatja a legrosszabb helyzetet ezen a technológián keresztül A JEDEC szabvány annak biztosítása érdekében, hogy a DDR4/DDR5 az interfész (beleértve a Bitless kódkövetelményeket is) megfelel az összes releváns előírásoknak.

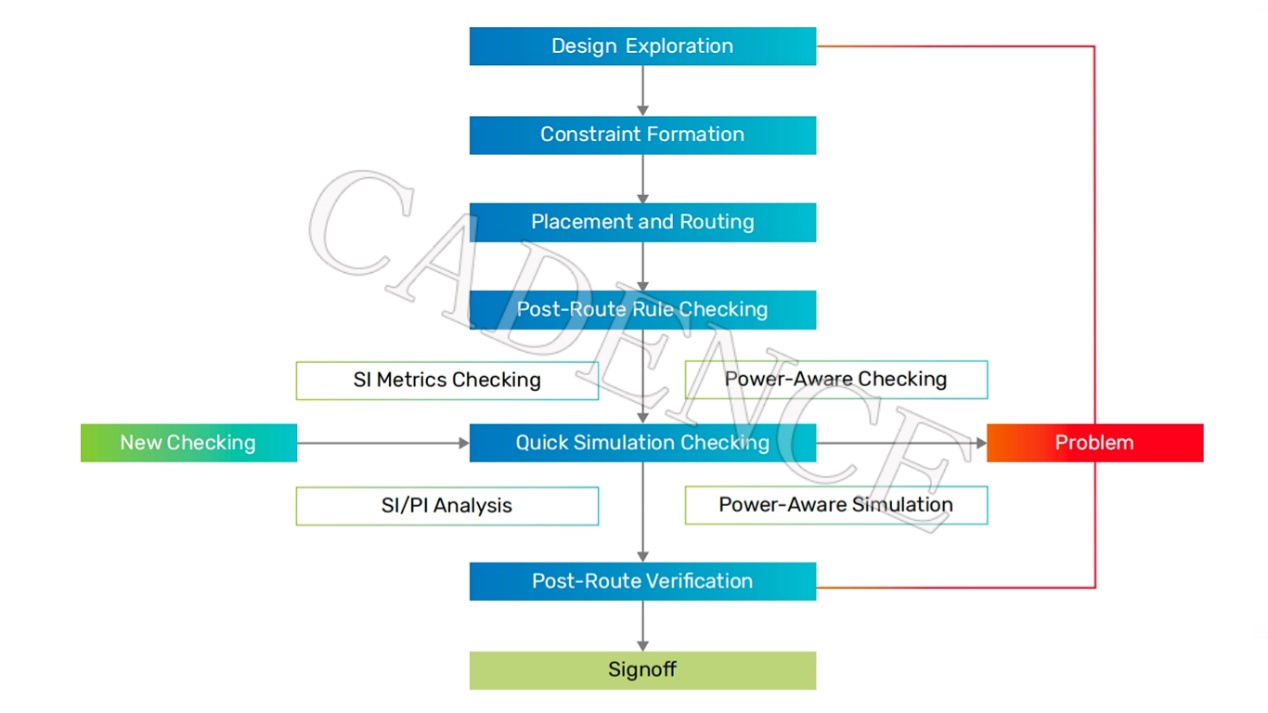

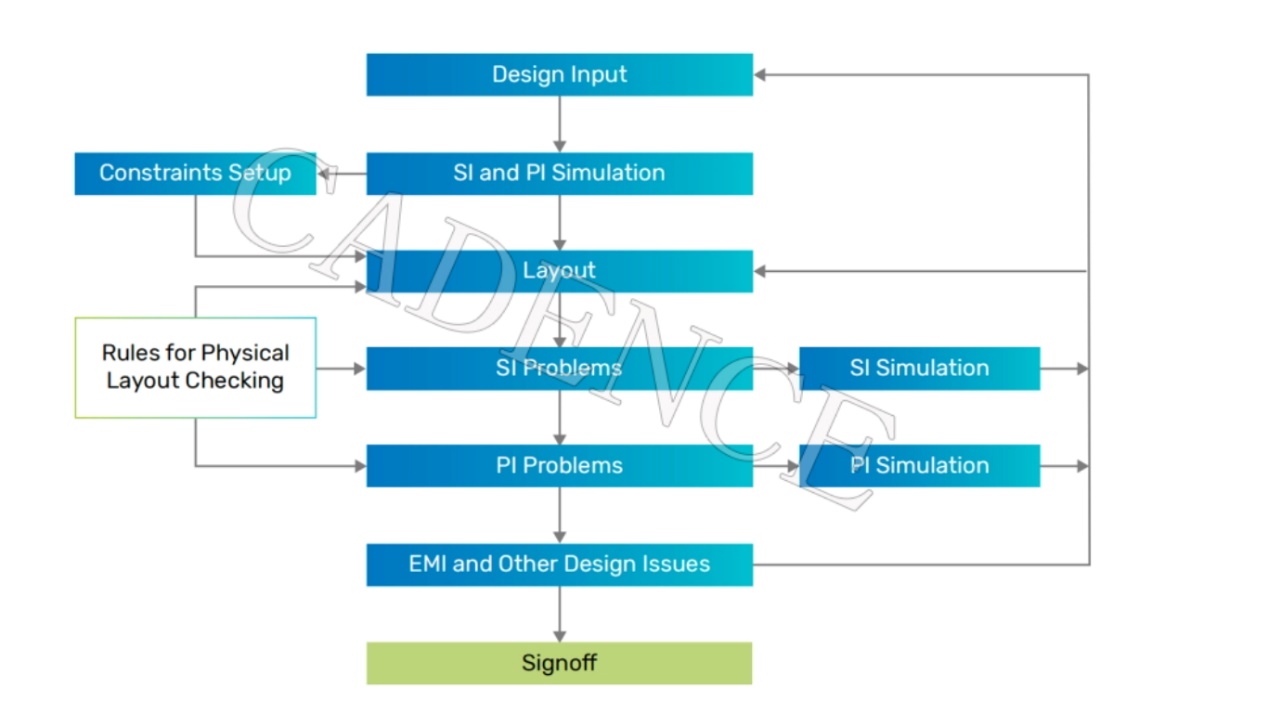

A 3. ábra az ellenőrzési és szimulációs folyamat, amely figyelembe veszi az áramellátás befolyását, amely éles ellentétben áll a hagyományos kényszer -vezérelt tervezési eljárással (4. ábra).A hagyományos kényszermeghajtók tervezési folyamata elsősorban négy részből áll: az előzetes huzalozás, a korlátozás kialakulása, a szabályok ellenőrzése és a vezeték utáni ellenőrzés.

3. ábra: A Cadence figyelembe veszi az áramellátás befolyásának korlátozásának folyamatát

VS

4. ábra: Példa a hagyományos kényszer illesztőprogram -tervezési folyamatra

A jelenlegi szimulációs technológiák közül gyakran vannak leválasztva a jelelemzés és az energiaelosztó hálózat (PDN) között, és vannak más hiányosságok is.Normál körülmények között, a fűszermodell bonyolultsága szerint, néha használja az időtartomány szimulációját a pontos ellenállás/induktivitás/kondenzátorok (RLC) modellek előállításához, és néha ideális alapvető síkot feltételez.Az ebből kapott időtartomány -modell a szimulációs extrakció egyszerű frekvenciaválaszán alapul. Noha ez kényelmesebb, a pontosság szempontjából kissé nem elegendő. A magasabb frekvenciákhoz a mérnökök a vegyes megoldó eszköz által létrehozott S paramétereket fogják használni.

Valójában létezik egy hatékony módszer a korlátozott különbség -időtartomány (FDTD) módszerrel a vegyes megoldó eszközzel, hogy a lefedettséget a jel, az áramellátás és a földelő vonal kibővítéséhez bővítse.

Ennek a módszernek a sikeres gyakorlati esete a Cadence's Sigrity Speed2000 motor eszköze. Ez integrálja és integrálja több megoldás kimenetét az áramköri vezetékek, az átviteli vezetékek és az elektromágneses mező problémáinak megoldására, és jobban megjelenítheti az adatokat és az energia/alapsík interakciót a különböző állapotban. alkalommal.És használja az FDTD módszert az IC csomagolás és a PCB elrendezésének elemzéséhez.Fontos referencia alapot nyújt az áramkör tervezésének további optimalizálásához.

A végső aláírási szakaszba való belépéskor a mérnökök általában 3D teljes hullámmodellezési módszereket használnak a nagyobb pontosság elérésére.De ez több számítástechnikai forrást fogyaszt és növeli a szimulációs időt.A probléma enyhítése érdekében a megosztás és a párhuzamosítási technológia elfogadható.Ebben a tekintetben a Clarity 3D megoldó felhasználásával a véges elem -elemzés (FEM) elemzéséhez, majd a Sigrity Xractim technológiának kombinálásával az egyes elemzések eredményei újra összeomlanak, hogy a frekvenciaválasz alapján egy S paramétermodellt képezzenek, ezáltal elérve a A teljes rendszer a teljes rendszerhez vagy a tervezés mélyreható és pontos elemzéséhez.

Összesít

A technológiai ugráshoz egyidejűleg javult a technológia, és elkerülhetetlen új kihívások megfogalmazása a tervezők számára.A DDR5 memória és az új kihívások felé vezető úton, a Sigrity X Cadence éles "éles pengéjével", a mérnökök nyugodtan megbirkózhatnak a jel integritásának összetett kérdéseivel, biztosítva, hogy a termék nem csak a specifikációkkal összhangban. Teljesítmény, újabb tégla hozzáadásával a jövőbeli innováció útjához.