Noticias

Se acerca la efectividad de DDR5 y no se pueden ignorar los nuevos desafíos

- Autor:ROGER

- Liberar:2023-12-04

En el frenesí de la inteligencia artificial (IA), el aprendizaje automático (ML) y la minería de datos, nuestro deseo de procesamiento de datos muestra un crecimiento de índice sin precedentes.Enfrentando esta perspectiva, el ancho del ancho de banda de la memoria se ha convertido en una "arterias" clave en la era digital.Entre ellos, la tecnología DDR (tasa de datos doble), conocida por las tasas de transmisión de datos dobles y el mayor ancho de banda como memoria de acceso aleatorio (DRAM) dinámico, ha promovido en gran medida la mejora del rendimiento de la computadora.Desde el nacimiento de la primera generación de tecnología DDR en 2000, hasta DDR5 en 2020, cada generación de tecnología DDR ha logrado mejoras significativas en diversos aspectos, como el ancho de banda, el rendimiento y el consumo de energía.

Hoy, ya sea PC, computadora portátil o inteligencia artificial, varias industrias están acelerando para avanzar hacia la nueva era de DDR5.Este año, el mercado de IA de generación está en auge, y los servidores de IA utilizados en aplicaciones modelo grandes han promovido vigorosamente la demanda de DDR5.Con la recuperación de la demanda del mercado de memoria, los proveedores de chips de memoria han demostrado la capacidad de producción de DDR5 en el cuarto trimestre de este año para reemplazar gradualmente el DDR4 actual.

La nueva era de DDR5 ha llegado, sin embargo, algunos desafíos también han obstaculizado el desarrollo adicional de la industria.

ERA DDR5: Desafíos de diseño detrás del rendimiento de la velocidad ultra alta

En julio de 2020, el estándar de tecnología de memoria DDR5 se lanzó oficialmente, marcando que la tecnología de memoria abrió un nuevo capítulo.DDR5 ha atraído una atención generalizada con un mayor ancho de banda y rendimiento.En comparación con el DDR4 anterior, la mayor ventaja de DDR5 es que ha reducido significativamente el consumo de energía y duplicó el ancho de banda.Específicamente, la tasa más alta del protocolo de liberación actual de DDR5 ha alcanzado 6.4GbpsLa frecuencia del reloj también aumentó de 1.6GHz a 3.2GHz.

Cuando exploramos más detalles de DDR5, también encontramos que esta nueva tecnología ha traído algunos desafíos técnicos adicionales.Por ejemplo, el voltaje de la fuente de alimentación de DDR5 disminuye en 0.1V en 1.2V desde DDR4, alcanzando 1.1V. Aunque el voltaje de la fuente de alimentación más bajo reduce desafíos, como tales como desafíos técnicos, como, como algunos desafíos técnicos, como algunos desafíos técnicos, como algunos desafíos técnicos, como algunos desafíos técnicos, como, como, como, como Algunos desafíos técnicos, como, como los desafíos técnicos, como, como algunos desafíos técnicos. Por ejemplo, es más probable que se vea perturbado por el ruido, lo que hace que la integridad de la señal sea más desafiante, porque la cantidad de ruido entre el voltaje Entre el voltaje durante el interruptor de señal es menor y puede afectar el diseño.

Otro cambio importante de DDR5 es diferente de la forma en que el chip de gestión de energía (PMIC) de DDR4 está integrado en la placa base. DDR5 transfirió el IC de administración de energía (PMIC) desde la placa base al módulo de memoria directa de doble columna (DIMM).Esto permite la administración de energía, la regulación de voltaje y la secuencia de potencia -en el físico más cercano al dispositivo de almacenamiento en el módulo, lo que también ayuda a garantizar la integridad de la fuente de alimentación (PI) y mejorar el control del método de operación PMIC.

Además, cuando el número total de bits de datos permanece sin cambios, el número de canales DIMM de 1 canal a 2 canales también es un progreso importante. Al transmitir datos a dos transmisión de canal estrecho, se puede generar y generar más efectivamente de manera más efectiva Señales de reloj para mejorar la integridad de la señal.

Obviamente, el desarrollo del estándar DDR5 también ha tenido en cuenta el problema de integridad de la señal, y la transferencia de PMIC al módulo también ejercerá las ventajas correspondientes.Sin embargo, los diseñadores aún deben considerar el efecto general de la integridad de la señal de la fuente de alimentación.Como se mencionó anteriormente, DDR5 tiene una velocidad de datos de hasta 6.4 Gbps y la frecuencia del reloj del sistema de 3.2GHz. El ruido de alimentación puede causar problemas más obvios en esta operación de alta velocidad, lo que afectará el rendimiento y la estabilidad del sistema.Si la integridad de la potencia y la integridad de la señal se analizan por separado, se puede perder el problema del ruido de la fuente de alimentación.

Por lo tanto, para dar un juego completo al rendimiento de DDR5, todos los puntos clave del sistema deben incluir chips, empaques y PCB para el análisis de integridad de la señal de la influencia de la fuente de alimentación.Sin embargo, el análisis de este nivel es una tarea compleja. Tiene altos requisitos para las herramientas de hardware y software utilizadas para el análisis de simulación para la plataforma informática subyacente. La dificultad y la complejidad del diseño.

Libere completamente el potencial de DDR5, cadencia

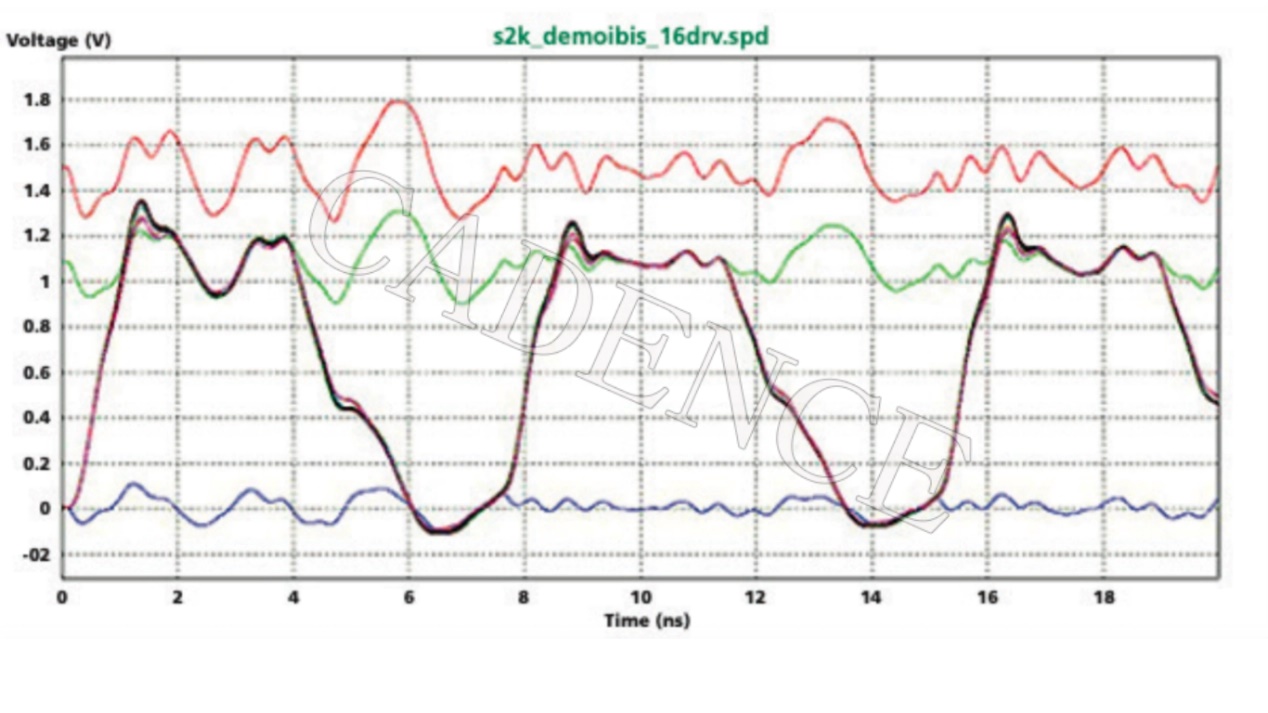

Ya en 2005, el concepto de "tener en cuenta la influencia de la fuente de alimentación" debutó por primera vez. Es un método avanzado de simulación de integridad de señal que puede analizar las señales y el ruido de potencia al mismo tiempo (Figura 1).La solución de integridad de la señal que tiene en cuenta la influencia de la fuente de alimentación debe considerar la reflexión, la cadena, los efectos secuenciales y de otro tipo, y equipado con las técnicas de inspección de simulación y reglas correspondientes.Vale la pena señalar que para implementar efectivamente la simulación de integridad de la señal que tiene en cuenta el impacto de la fuente de alimentación, es necesario realizar en la fase de análisis después de la inspección y el cableado regular, porque la interacción/acoplamiento del plano y la señal ocurre Después de completar el cableado.

Por lo tanto, se debe proporcionar una solución completa que tenga en cuenta la influencia de la fuente de alimentación:

l Un conjunto de soluciones de inspección rápida para la atenuación de la señal y la fuente de alimentación en las señales

L puede simular el simulador de dominio de tiempo de grandes circuitos (los resultados de múltiples redes de señal y redes de energía)

L Network de Power y modelado de red de señales

l modelado de búfer de entrada/salida de alto nivel (E/S)

Figura 1: El resultado de la integridad de la señal de la influencia de la fuente de alimentación

Aunque muchas herramientas en el mercado respaldan los estándares básicos de modelado de E/S que tienen en cuenta la influencia de la fuente de alimentación, con el desarrollo continuo de la tecnología de interfaz de memoria, los requisitos del mercado para las herramientas de integridad de la señal también están aumentando. La herramienta de extracción precisa para el La señal de acoplamiento, la fuente de alimentación y la señal de tierra en la PCB es rara.

En este sentido, como una empresa líder en el campo de la simulación EDA, la tecnología Sigrity X lanzada por Cadence proporciona un análisis de integridad de señal de la influencia de la fuente de alimentación para DDR4 y DDR5.

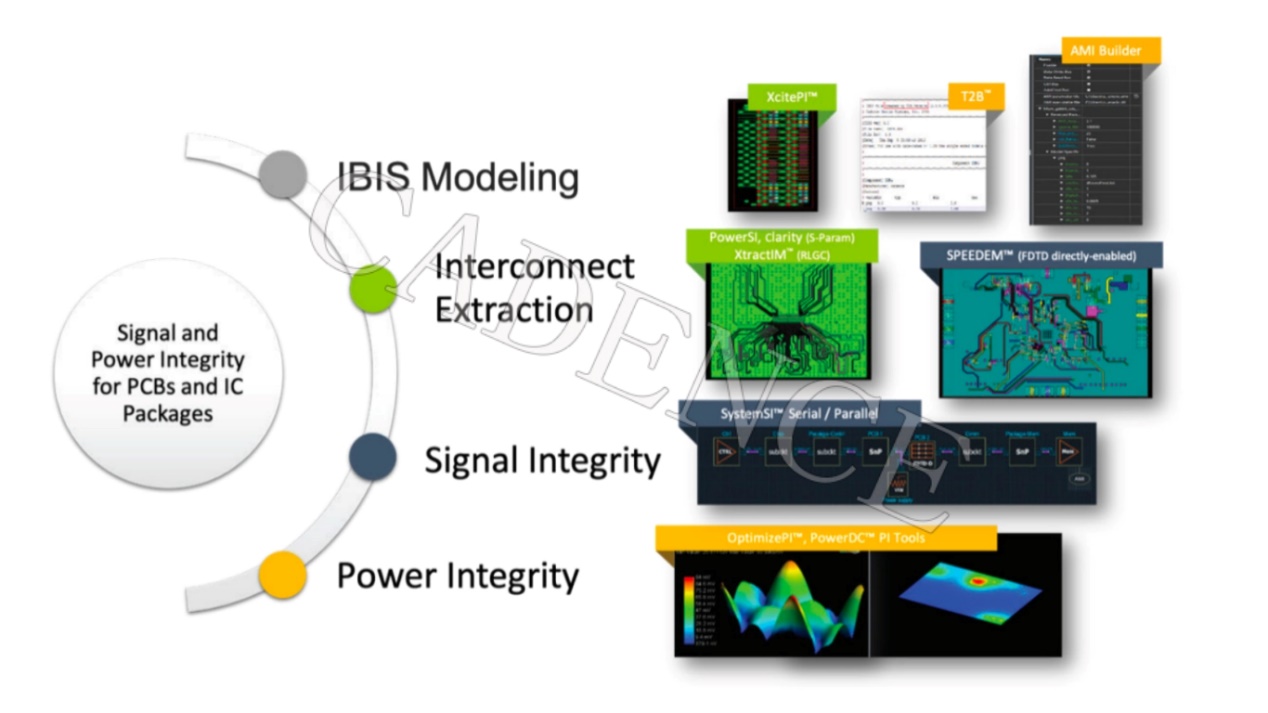

La tecnología Sigrity X no solo se da cuenta de la extracción precisa de señales acopladas, fuente de alimentación y señales de tierra en chips, empaques y PCB, sino que también puede hacer una simulación eficiente sobre la reflexión, la pérdida, la salida del interruptor (SSO) (SSO) con la misma tiempo.Los diseñadores que utilizan la tecnología Sigrity pueden convertir rápidamente el modelo de nivel de transistor en un modelo IBIS de nivel de comportamiento que considera la influencia de la potencia, de modo que en unas pocas horas, puede proporcionar preciso, eficiente e integral considerando la simulación de los efectos del suministro de energía, que en gran medida Acorta el número original de que originalmente necesita estar numerado. Ciclo de diseño del cielo.(Figura 2)

Figura 2: Herramienta de integridad de señal de cadencia e integridad de potencia para envases de PCB e IC

La tecnología Sigrity X simplifica el flujo de trabajo, proporciona simulación sincrónica de diseño y la precisión del nivel de firma para la verificación final.Las señales, la potencia y los problemas de calor se pueden resolver en cada etapa de diseño, reduciendo así el número de iteraciones entre los equipos de diseño y análisis.Los diseñadores pueden ejecutar el motor de nivel nuclear en el diseño de la tela de dibujo para una simulación de alta precisión, proporcionando así un diseño de alta calidad para que los equipos de análisis verifiquen.Más tarde, el equipo de análisis utilizó el motor de simulación paralelo a gran escala de Sigrity para hacer una simulación completa del sistema para garantizar que todo el "chip-empackaging-PCB-shell" cumpla con las especificaciones de diseño y prepararse para la firma.

Estas ventajas hacen de Sigry X la mejor solución para la memoria DDR5 y la interfaz 112G.Su modelado de interconexión estándar dorado combina la simulación de dominio de tiempo (simulación de circuito y canal) del análisis serial/solución (SERDES) y el soporte de la interfaz de modelado de algoritmo IBIS (AMI), que brinda ventajas únicas de cadencia, por lo tanto, puede extraer e interfaz de firma de cumplimiento Soluciones completas.

Además, la tecnología de solucionador 3D Sigrity Xtractim y Clarity 3D se puede utilizar en conjunción, lo que permite a los ingenieros crear modelos completos de envasado que contienen señales de acoplamiento, fuente de alimentación y modelos de interconexión de conexión a tierra para varios tipos de envases, que compensan efectivamente el diseño de envasado y las características del paquete. El espacio entre.

Además, la tecnología Sigrity Systemsi admite el modelo IBIS que puede conectarse rápidamente a la influencia de la fuente de alimentación y al modelo de interconexión que tiene en cuenta la influencia de la fuente de alimentación. El diseñador puede determinar rápidamente la peor situación a través de esta tecnología y compararla con el Estándar JEDEC para garantizar que DDR4/DDR5 la interfaz (incluidos los requisitos de tasa de código sin bits) cumpla con todas las especificaciones relevantes.

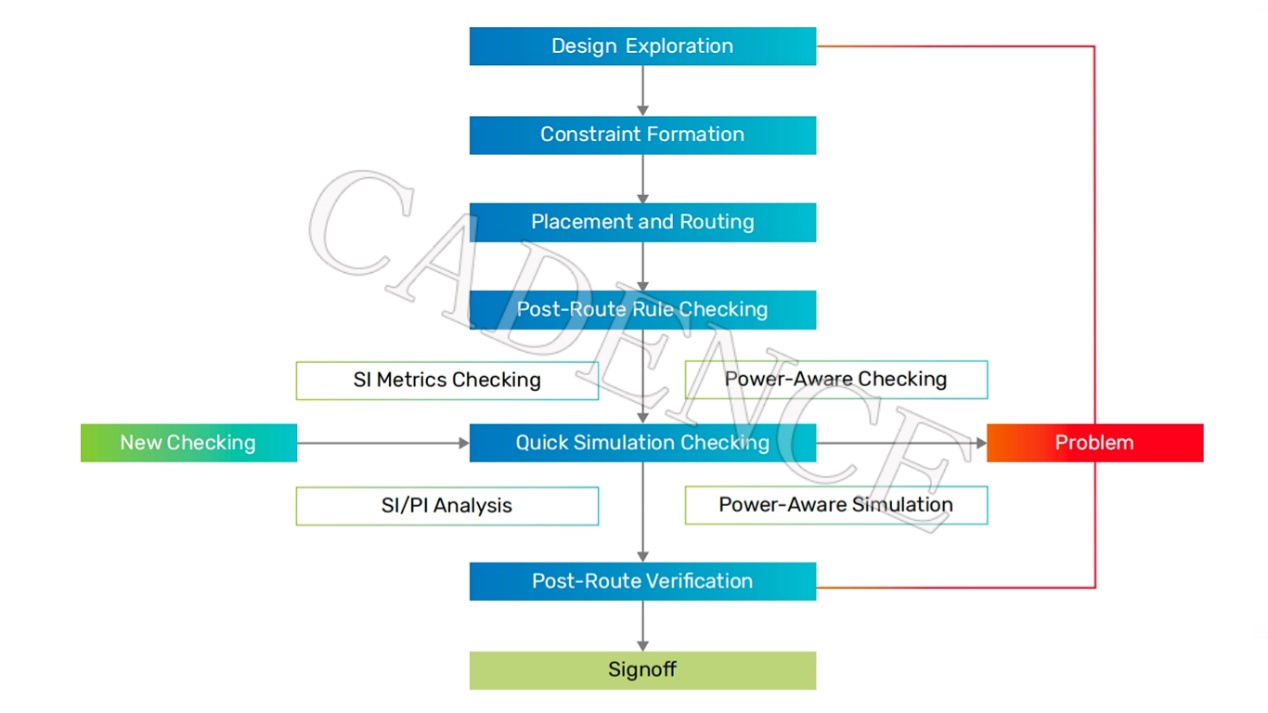

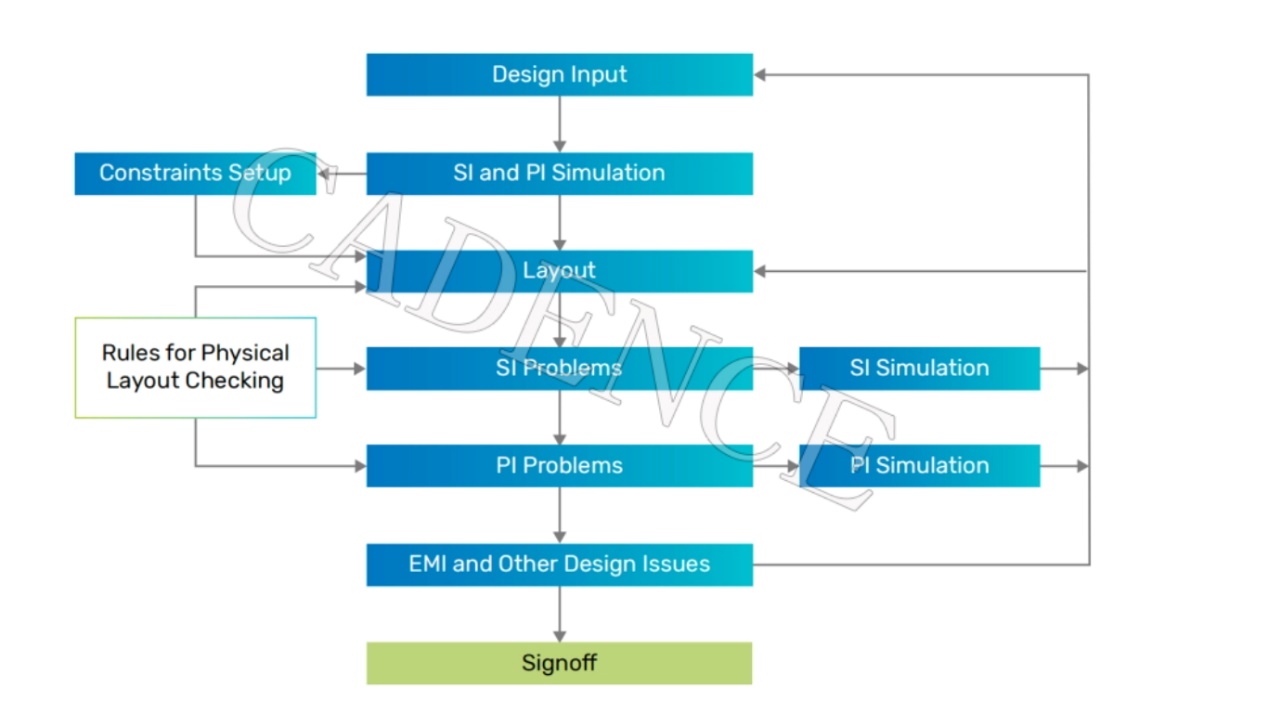

La Figura 3 es el proceso de inspección y simulación que tiene en cuenta la influencia de la fuente de alimentación, que contrasta con el proceso de diseño impulsado por la restricción tradicional (Figura 4).El proceso de diseño de los controladores de restricciones tradicionales incluye principalmente cuatro partes: cableado previo a la capa, formación de restricciones, inspección de reglas y verificación posterior al cableado.

Figura 3: La cadencia tiene en cuenta el proceso de impulsor de restricción de la influencia de la fuente de alimentación

VS

Figura 4: Ejemplo del proceso de diseño de controlador de restricciones tradicionales

Entre las muchas tecnologías de simulación de corriente, a menudo hay desconexiones entre el análisis de señal y la red de distribución de energía (PDN), y hay otras deficiencias.En circunstancias normales, de acuerdo con la complejidad del modelo de especias, a veces usa simulación de dominio de tiempo para generar modelos precisos de resistencia/inductancia/condensadores (RLC), y a veces asume un plano de tierra ideal.El modelo de dominio de tiempo obtenido de esto se basa en la simple respuesta de frecuencia de la extracción de simulación. Aunque es más conveniente, es ligeramente insuficiente en términos de precisión. Para frecuencias más altas, los ingenieros utilizarán los parámetros S creados por un dispositivo de resolución mixto.

De hecho, también existe un método eficiente para combinar el método de dominio de tiempo de diferencia de diferencia limitada (FDTD) con el dispositivo de resolución mixto para expandir la cobertura a señal, fuente de alimentación y línea de conexión a tierra.

El caso de práctica exitoso de este método es la herramienta de motor Sigrity Speed2000 de Cadence. Integra e integra la salida de varias soluciones para resolver el cableado del circuito, las líneas de transmisión y los problemas de campo electromagnético, y puede mostrar mejor los datos y la interacción de plano de potencia/tierra en diferentes veces.Y use el método FDTD para analizar el diseño del embalaje IC y PCB.Proporciona una base de referencia importante para la optimización adicional del diseño del circuito.

Al ingresar a la etapa de firma final, los ingenieros generalmente tienden a usar métodos de modelado de onda completa 3D para obtener una mayor precisión.Pero esto consumirá más recursos informáticos y aumentará el tiempo de simulación.Para aliviar este problema, se puede adoptar la tecnología de división y paralelización.En este sentido, al utilizar el Clarity 3D Solver para un análisis de análisis de elementos finitos (FEM), y luego combinar la tecnología Sigrity Xtractim, los resultados de cada análisis se vuelven a formar un modelo de parámetro S basado en la respuesta de frecuencia, logrando así el logro de la respuesta de frecuencia, logrando así Sistema completo a todo el sistema o en el análisis de diseño y preciso de diseño.

Resumir

Al mismo tiempo que el salto tecnológico, la tecnología se ha mejorado, y es inevitable presentar nuevos desafíos para los diseñadores.En el camino hacia la memoria DDR5 y los nuevos desafíos, con la aguda "cuchilla afilada" de Cadence Sigrity X, los ingenieros pueden hacer frente a los problemas complejos de integridad de la señal, asegurando que el producto no solo sea consistente con las especificaciones. También brilla. rendimiento, agregando otro ladrillo al camino de la innovación futura.