Berita

Era DDR5 semakin dekat, dan tantangan baru tidak dapat diabaikan

- Penulis:ROGER

- Lepaskan di:2023-12-04

Dalam kegilaan kecerdasan buatan (AI), pembelajaran mesin (ML), dan penambangan data, keinginan kami untuk pemrosesan data menunjukkan pertumbuhan indeks yang belum pernah terjadi sebelumnya.Menghadapi prospek ini, lebar bandwidth memori telah menjadi "arteri" kunci di era digital.Di antara mereka, teknologi DDR (Double Data Rate), yang dikenal dengan laju transmisi data ganda dan bandwidth yang lebih tinggi sebagai memori akses acak dinamis (DRAM), telah sangat mempromosikan peningkatan kinerja komputer.Dari kelahiran generasi pertama teknologi DDR pada tahun 2000, hingga DDR5 pada tahun 2020, setiap generasi teknologi DDR telah mencapai peningkatan yang signifikan dalam berbagai aspek seperti bandwidth, kinerja dan konsumsi daya.

Saat ini, apakah itu PC, laptop atau kecerdasan buatan, berbagai industri semakin cepat bergerak menuju era baru DDR5.Tahun ini, pasar AI generasi sedang booming, dan server AI yang digunakan dalam aplikasi model besar telah dengan kuat mempromosikan permintaan untuk DDR5.Dengan pemulihan permintaan pasar memori, pemasok chip memori telah menunjukkan kapasitas produksi DDR5 pada kuartal keempat tahun ini untuk secara bertahap menggantikan DDR4 saat ini.

Era baru DDR5 telah tiba, namun, beberapa tantangan juga telah menghambat pengembangan industri lebih lanjut.

DDR5 ERA: Tantangan Desain Di Balik Kinerja Ultra -Tinggi -Kecepatan

Pada Juli 2020, standar teknologi memori DDR5 secara resmi dirilis, menandai bahwa teknologi memori membuka bab baru.DDR5 telah menarik perhatian luas dengan bandwidth dan kinerja yang lebih tinggi.Dibandingkan dengan DDR4 sebelumnya, keuntungan terbesar dari DDR5 adalah telah secara signifikan mengurangi konsumsi daya dan menggandakan bandwidth.Secara khusus, tingkat tertinggi protokol rilis DDR5 saat ini telah tercapai 6.4GbpsFrekuensi jam juga meningkat dari 1,6GHz menjadi 3.2GHz.

Ketika kami mengeksplorasi lebih banyak detail DDR5, kami juga menemukan bahwa teknologi baru ini telah membawa beberapa tantangan teknis tambahan.Sebagai contoh, tegangan catu daya DDR5 berkurang 0,1V sebesar 1,2V dari DDR4, mencapai 1,1V. Meskipun tegangan catu daya yang lebih rendah mengurangi konsumsi daya dan memperpanjang masa pakai baterai, itu juga membawa beberapa tantangan teknis, seperti seperti teknis Tantangan, seperti seperti tantangan teknis, seperti, seperti beberapa tantangan teknis, seperti, seperti beberapa tantangan teknis, seperti, seperti beberapa tantangan teknis, seperti, seperti beberapa tantangan teknis, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, seperti, Beberapa tantangan teknis, seperti, seperti tantangan teknis, seperti, seperti beberapa tantangan teknis. Misalnya, lebih mungkin terganggu oleh kebisingan, yang membuat integritas sinyal lebih menantang, karena jumlah kebisingan antara tegangan Antara tegangan selama sakelar sinyal lebih sedikit dan dapat mempengaruhi desain.

Perubahan utama DDR5 lainnya berbeda dari cara chip manajemen daya (PMIC) DDR4 diintegrasikan pada motherboard. DDR5 mentransfer IC manajemen daya (PMIC) dari motherboard ke Dual -Column Direct Memory Module (DIMM).Hal ini memungkinkan manajemen daya, regulasi tegangan, dan urutan daya ke fisik lebih dekat ke perangkat penyimpanan pada modul, yang juga membantu memastikan integritas catu daya (PI) dan meningkatkan kontrol metode operasi PMIC.

Selain itu, ketika jumlah total bit data tetap tidak berubah, jumlah saluran DIMM dari 1 saluran ke 2 saluran juga merupakan kemajuan penting. Dengan mengirimkan data ke dalam dua transmisi saluran sempit, itu dapat lebih efektif dihasilkan dan dihasilkan secara lebih efektif. sinyal jam untuk meningkatkan integritas sinyal.

Jelas, pengembangan standar DDR5 juga telah memperhitungkan masalah integritas sinyal, dan transfer PMIC ke modul juga akan memberikan keuntungan yang sesuai.Namun, desainer masih perlu mempertimbangkan efek keseluruhan integritas sinyal catu daya.Seperti disebutkan di atas, DDR5 memiliki laju data hingga 6.4Gbps dan frekuensi clock sistem 3.2GHz. Kebisingan daya dapat menyebabkan masalah yang lebih jelas dalam operasi kecepatan tinggi ini, yang akan mempengaruhi kinerja dan stabilitas sistem.Jika integritas daya dan integritas sinyal dianalisis secara terpisah, masalah kebisingan catu daya mungkin terlewatkan.

Oleh karena itu, untuk memberikan permainan penuh pada kinerja DDR5, semua titik utama sistem harus mencakup chip, pengemasan, dan PCB untuk analisis integritas sinyal dari pengaruh catu daya.Namun, analisis level ini adalah tugas yang kompleks. Ini memiliki persyaratan tinggi untuk perangkat keras dan perangkat lunak yang digunakan untuk analisis simulasi untuk platform komputasi yang mendasarinya. Kesulitan dan kompleksitas desain.

Lepaskan potensi DDR5, irama

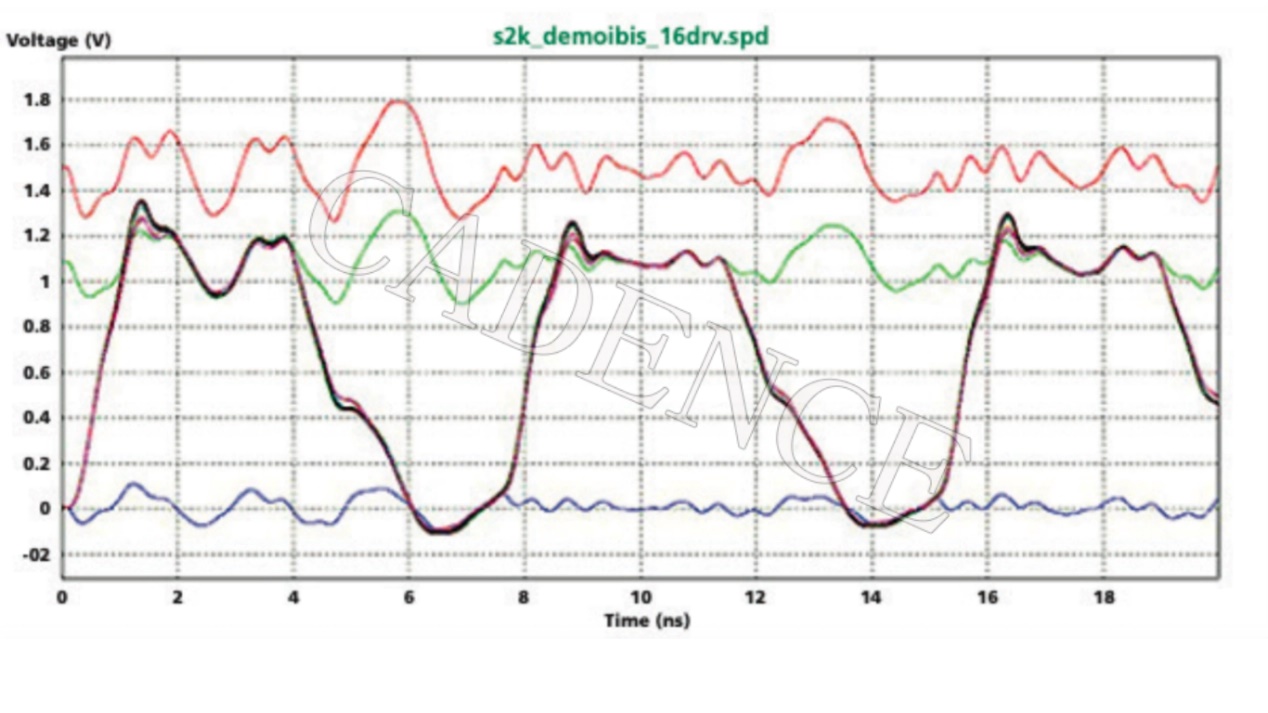

Pada awal 2005, konsep "dengan mempertimbangkan pengaruh catu daya" yang debutnya untuk pertama kalinya. Ini adalah metode simulasi integritas sinyal canggih yang dapat menganalisis sinyal dan kebisingan daya pada saat yang sama (Gambar 1).Solusi integritas sinyal yang memperhitungkan pengaruh catu daya harus mempertimbangkan refleksi, rangkaian, efek berurutan dan lainnya, dan dilengkapi dengan simulasi dan teknik inspeksi aturan yang sesuai.Perlu dicatat bahwa untuk secara efektif mengimplementasikan simulasi integritas sinyal yang memperhitungkan dampak catu daya, perlu dilakukan dalam fase analisis setelah inspeksi dan kabel secara teratur, karena interaksi/penggabungan bidang dan sinyal terjadi terjadi Setelah kabel selesai.

Oleh karena itu, solusi lengkap yang memperhitungkan pengaruh catu daya sering kali perlu disediakan:

l Satu set solusi inspeksi cepat untuk atenuasi sinyal dan catu daya pada sinyal

L dapat mensimulasikan simulator domain waktu sirkuit besar (hasil beberapa jaringan sinyal dan jaringan daya)

L jaringan daya dan pemodelan jaringan sinyal

L TINGKAT High -Input/Output (I/O) Buffer Modeling

Gambar 1: Hasil integritas sinyal dari kedua pengaruh catu daya

Meskipun banyak alat di pasaran mendukung standar pemodelan I/O dasar yang memperhitungkan pengaruh catu daya, dengan pengembangan berkelanjutan teknologi antarmuka memori, persyaratan pasar untuk alat integritas sinyal juga meningkat. Alat ekstraksi yang akurat untuk tersebut Sinyal kopling, catu daya dan sinyal ground pada PCB jarang terjadi.

Dalam hal ini, sebagai perusahaan terkemuka di bidang simulasi EDA, teknologi Sigrity X yang diluncurkan oleh Cadence memberikan analisis integritas sinyal tentang pengaruh catu daya untuk DDR4 dan DDR5.

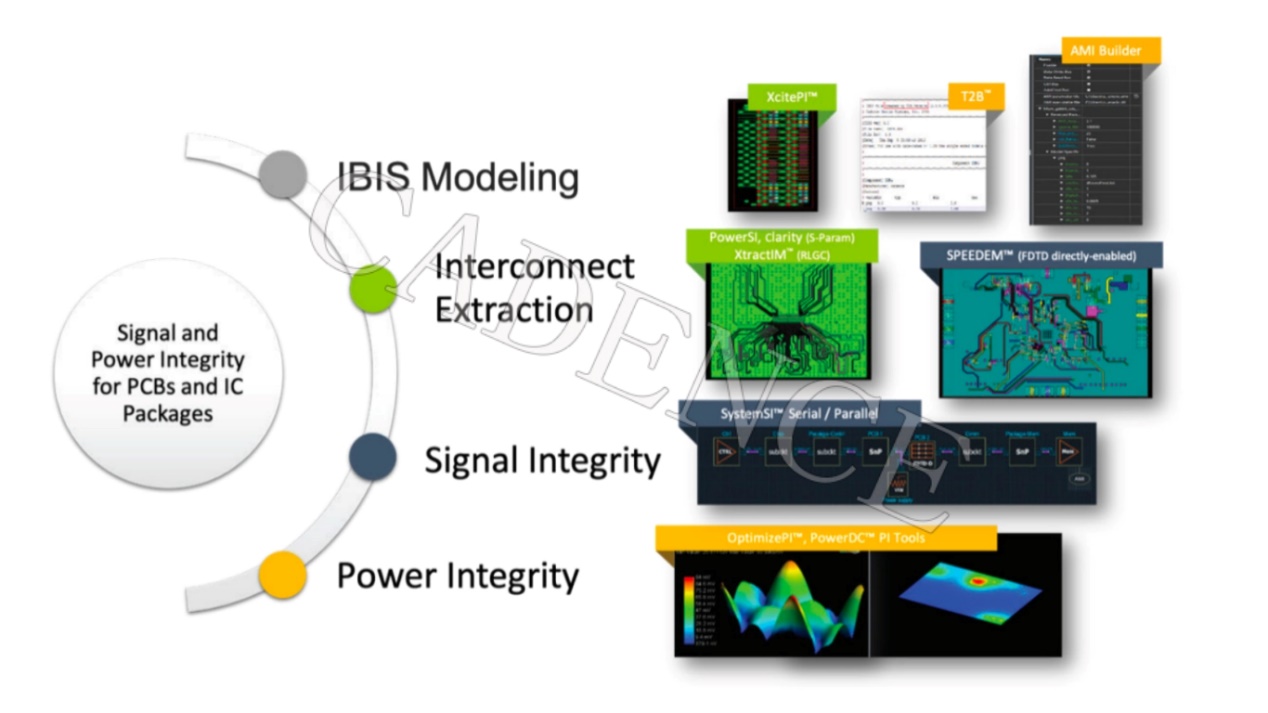

Sigrity X Teknologi tidak hanya menyadari ekstraksi yang tepat dari sinyal yang digabungkan, catu daya dan sinyal tanah pada chip, pengemasan dan PCB, tetapi juga dapat membuat simulasi yang efisien pada refleksi, kehilangan, bandidal, dan efek output sakelar (SSO) yang sama pada hal waktu.Desainer yang menggunakan teknologi Sigrity dapat dengan cepat mengubah model tingkat transistor menjadi model IBIS tingkat perilaku yang mempertimbangkan pengaruh daya, sehingga dalam beberapa jam, dapat memberikan simulasi efek catu daya yang tepat, efisien dan komprehensif, yang sangat besar, yang sangat besar, yang sangat. Memperpendek jumlah asli yang awalnya perlu diberi nomor. Siklus Desain Langit.(Gambar 2)

Gambar 2: Integritas Sinyal Cadence dan Alat Integritas Daya untuk PCB dan IC Packaging

Sigrity X Technology menyederhanakan alur kerja, memberikan simulasi sinkron desain dan keakuratan tingkat penandatanganan untuk verifikasi akhir.Sinyal, daya, dan masalah panas dapat diselesaikan pada setiap tahap desain, sehingga mengurangi jumlah iterasi antara tim desain dan analisis.Desainer dapat menjalankan mesin tingkat nuklir dalam desain kain gambar untuk simulasi presisi tinggi, sehingga memberikan desain berkualitas tinggi untuk diverifikasi tim analisis.Kemudian, tim analisis menggunakan mesin simulasi paralel skala besar Sigrity untuk membuat simulasi sistem penuh untuk memastikan bahwa seluruh "chip-packaging-pcb-shell" memenuhi spesifikasi desain dan bersiap untuk penandatanganan.

Keuntungan ini menjadikan Sigrity X solusi terbaik untuk memori DDR5 dan antarmuka 112G.Pemodelan interkoneksi standar emasnya menggabungkan simulasi domain waktu (sirkuit dan simulasi saluran) dari analisis serial/solusi (serdes) dan mendukung antarmuka pemodelan algoritma IBIS (AMI), yang memberikan keuntungan unik, karenanya penandatanganan kepatuhan dan penandatanganan kepatuhan antarmuka menyediakan penandatanganan kepatuhan. solusi lengkap.

Selanjutnya, Sigrity XtracTim dan Clarity 3D Solver Technology dapat digunakan bersama, yang memungkinkan para insinyur untuk membuat model kemasan lengkap yang berisi sinyal kopling, catu daya dan model interkoneksi landasan untuk berbagai jenis kemasan, yang secara efektif menebus desain kemasan dan karakteristik paket paket Kesenjangan antara.

Selain itu, teknologi Sigrity Systemsi mendukung model IBIS yang dapat dengan cepat terhubung dengan pengaruh catu daya dan model interkoneksi yang memperhitungkan pengaruh catu daya. Perancang dapat dengan cepat menentukan situasi terburuk melalui teknologi ini dan membandingkannya dengan Jedec Standard Untuk memastikan bahwa DDR4/DDR5 antarmuka (termasuk persyaratan tarif kode bitless) memenuhi semua spesifikasi yang relevan.

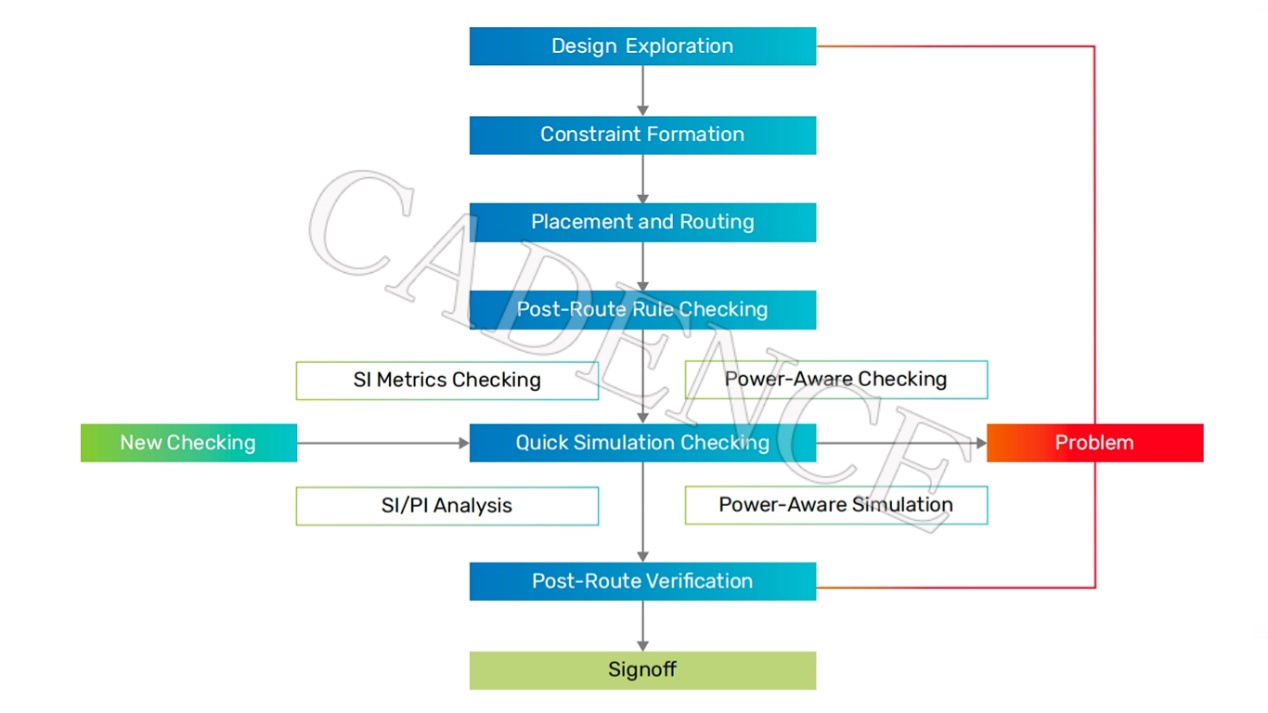

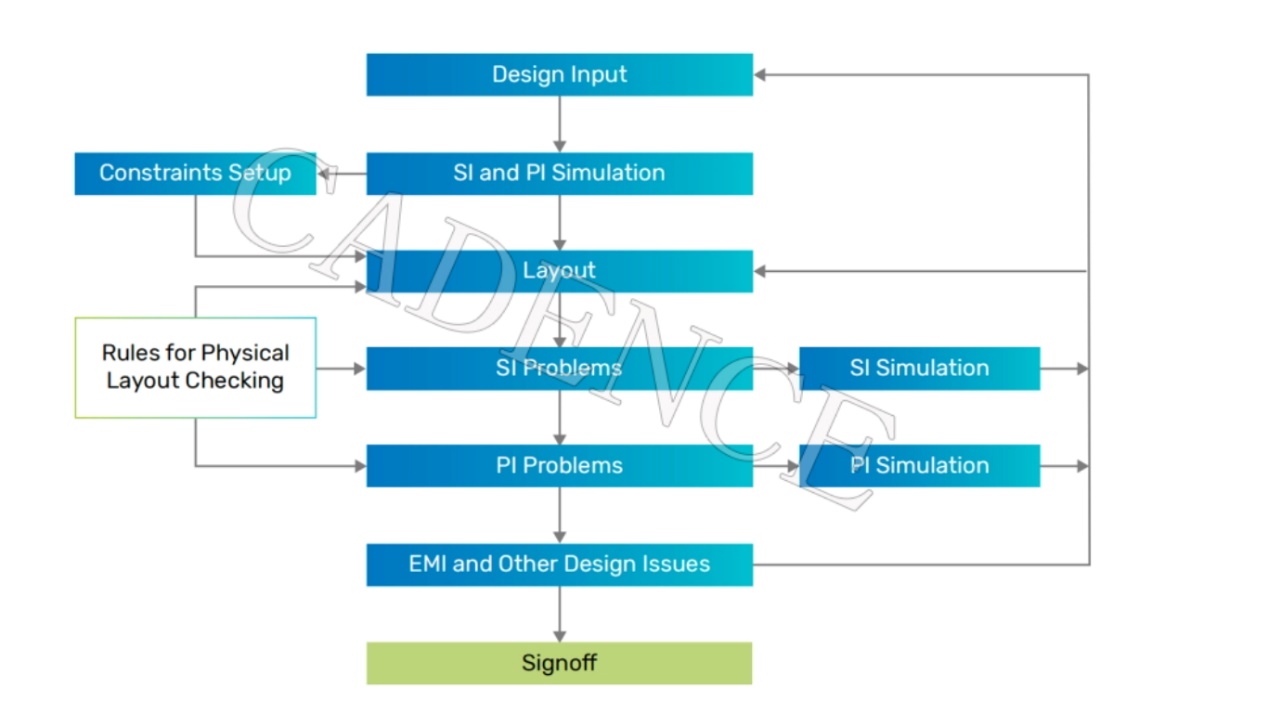

Gambar 3 adalah proses inspeksi dan simulasi yang memperhitungkan pengaruh catu daya, yang sangat kontras dengan proses desain yang didorong oleh kendala tradisional (Gambar 4).Proses desain driver kendala tradisional terutama mencakup empat bagian: Kabel pra -layout, pembentukan kendala, inspeksi aturan, dan verifikasi pasca -pemandangan.

Gambar 3: Ikat memperhitungkan proses pengemudi kendala pengaruh catu daya

Vs.

Gambar 4: Contoh proses desain driver kendala tradisional

Di antara banyak teknologi simulasi saat ini, sering ada pemutusan antara analisis sinyal dan jaringan distribusi daya (PDN), dan ada beberapa kekurangan lainnya.Dalam keadaan normal, sesuai dengan kompleksitas model rempah -rempah, kadang -kadang menggunakan simulasi domain waktu untuk menghasilkan model resistansi/induktansi/kapasitor (RLC) yang akurat, dan kadang -kadang mengasumsikan bidang tanah yang ideal.Model domain waktu yang diperoleh dari ini didasarkan pada respons frekuensi sederhana dari ekstraksi simulasi. Meskipun lebih nyaman, itu sedikit tidak cukup dalam hal akurasi. Untuk frekuensi yang lebih tinggi, insinyur akan menggunakan parameter S yang dibuat oleh perangkat pemecahan campuran.

Faktanya, ada juga metode yang efisien untuk menggabungkan metode domain waktu perbedaan terbatas (FDTD) dengan perangkat pemecahan campuran untuk memperluas cakupan ke sinyal, catu daya dan saluran pembumian.

Kasus praktik yang berhasil dari metode ini adalah alat mesin Sigrity Speed2000 Cadence. Ini mengintegrasikan dan mengintegrasikan output dari beberapa solusi untuk menyelesaikan kabel sirkuit, saluran transmisi dan masalah medan elektromagnetik, dan dapat dengan lebih baik menampilkan data dan interaksi bidang daya/tanah di berbagai waktu.Dan gunakan metode FDTD untuk menganalisis tata letak kemasan IC dan PCB.Ini memberikan dasar referensi penting untuk optimalisasi lebih lanjut dari desain sirkuit.

Saat memasuki tahap penandatanganan akhir, insinyur biasanya cenderung menggunakan metode pemodelan gelombang penuh 3D untuk mendapatkan akurasi yang lebih tinggi.Tetapi ini akan mengkonsumsi lebih banyak sumber daya komputasi dan meningkatkan waktu simulasi.Untuk mengurangi masalah ini, teknologi divisi dan paralelisasi dapat diadopsi.Dalam hal ini, dengan menggunakan Solver 3D Clarity untuk analisis analisis elemen hingga (FEM), dan kemudian menggabungkan teknologi sigrity xtracTim, hasil dari setiap analisis dirancang ulang untuk membentuk model parameter S berdasarkan respons frekuensi, sehingga mencapai pada Seluruh sistem ke seluruh sistem atau analisis desain yang tepat dan tepat.

Meringkaskan

Pada saat yang sama dengan lompatan teknologi, teknologi ini telah ditingkatkan, dan tidak dapat dihindari untuk meletakkan tantangan baru bagi para desainer.Dalam perjalanan menuju memori DDR5 dan tantangan baru, dengan "bilah tajam" tajam dari Cadence Sigrity X, para insinyur dapat dengan tenang mengatasi masalah integritas sinyal yang kompleks, memastikan bahwa produk tidak hanya konsisten dengan spesifikasi. Ini juga bersinar di dalam kinerja, menambahkan batu bata lain ke jalan inovasi di masa depan.