Notizie

L'era DDR5 si sta avvicinando e le nuove sfide non possono essere ignorate

- Autore:ROGER

- Rilascio:2023-12-04

Nella frenesia dell'intelligenza artificiale (AI), dell'apprendimento automatico (ML) e del data mining, il nostro desiderio di elaborazione dei dati mostra una crescita dell'indice senza precedenti.Di fronte a questa prospettiva, la larghezza della larghezza di banda della memoria è diventata una chiave "arterie" nell'era digitale.Tra questi, la tecnologia DDR (doppia velocità dei dati), nota per le velocità di trasmissione dei dati doppie e una maggiore larghezza di banda come memoria dinamica di accesso casuale (DRAM), ha promosso notevolmente il miglioramento delle prestazioni del computer.Dalla nascita della prima generazione di tecnologia DDR nel 2000 a DDR5 nel 2020, ogni generazione di tecnologia DDR ha ottenuto miglioramenti significativi in vari aspetti come la larghezza di banda, le prestazioni e il consumo di energia.

Oggi, che si tratti di PC, laptop o intelligenza artificiale, varie industrie stanno accelerando per spostarsi verso la nuova era di DDR5.Quest'anno, il mercato dell'intelligenza artificiale di generazione è in forte espansione e i server di intelligenza artificiale utilizzati in grandi applicazioni modello hanno promosso vigorosamente la domanda di DDR5.Con il recupero della domanda di mercato della memoria, i fornitori di chip di memoria hanno mostrato la capacità di produzione di DDR5 nel quarto trimestre di quest'anno per sostituire gradualmente l'attuale DDR4.

La nuova era di DDR5 è arrivata, tuttavia, alcune sfide hanno anche ostacolato l'ulteriore sviluppo del settore.

DDR5 Era: Design Sfide dietro Ultra -High -Speed Performance

Nel luglio 2020, lo standard di tecnologia della memoria DDR5 è stato rilasciato ufficialmente, segnando quella tecnologia di memoria ha aperto un nuovo capitolo.DDR5 ha attirato un'attenzione diffusa con una larghezza di banda e prestazioni più elevate.Rispetto al precedente DDR4, il più grande vantaggio di DDR5 è che ha ridotto significativamente il consumo di energia e ha raddoppiato la larghezza di banda.In particolare, è stato raggiunto il più alto tasso di protocollo di rilascio corrente di DDR5 6,4 GbpsAnche la frequenza dell'orologio è aumentata da 1,6 GHz a 3,2 GHz.

Quando esploriamo maggiori dettagli di DDR5, scopriamo anche che questa nuova tecnologia ha portato alcune sfide tecniche aggiuntive.Ad esempio, la tensione di alimentazione di DDR5 diminuisce di 0,1 V di 1,2 V da DDR4, raggiungendo 1,1 V. Sebbene la tensione di alimentazione inferiore riduca il consumo di energia ed estenda la durata della batteria, porta anche alcune sfide tecniche, come come tali tecnici sfide, come come sfide tecniche, come ad esempio alcune sfide tecniche, come ad esempio alcune sfide tecniche, come alcune sfide tecniche, come alcune sfide tecniche, come ad esempio Alcune sfide tecniche, come, come sfide tecniche, come, come alcune sfide tecniche. Ad esempio, è più probabile che siano disturbati dal rumore, il che rende l'integrità del segnale più impegnativa, perché la quantità di rumore tra la tensione Tra la tensione durante l'interruttore del segnale è inferiore e può influire sul design.

Un altro importante cambiamento di DDR5 è diverso dal modo in cui il chip di gestione dell'alimentazione (PMIC) di DDR4 è integrato sulla scheda madre. DDR5 ha trasferito l'ICE di gestione dell'alimentazione (PMIC) dalla scheda madre al modulo di memoria diretta a doppia column (DIMM).Ciò consente la gestione dell'alimentazione, la regolamentazione della tensione e la sequenza di potenza per fisica più vicina al dispositivo di archiviazione sul modulo, il che aiuta anche a garantire l'integrità dell'alimentazione (PI) e migliorare il controllo del metodo di funzionamento PMIC.

Inoltre, quando il numero totale di bit di dati rimane invariato, anche il numero di canali DIMM da 1 canale a 2 canali è un progresso importante. Trasmissione dei dati in due trasmissioni di canale stretta, può essere generato in modo più efficace e generato in modo più efficace. Segnali di clock per migliorare l'integrità del segnale.

Ovviamente, lo sviluppo dello standard DDR5 ha anche preso in considerazione il problema dell'integrità del segnale e il trasferimento di PMIC al modulo eserciterà anche i vantaggi corrispondenti.Tuttavia, i progettisti devono ancora considerare l'effetto complessivo dell'integrità del segnale dell'alimentazione.Come accennato in precedenza, DDR5 ha una velocità dati fino a 6,4 Gbps e la frequenza di clock di sistema a 3,2 GHz. Il rumore di potenza può causare problemi più evidenti in questa operazione ad alta velocità, che influenzerà le prestazioni e la stabilità del sistema.Se l'integrità della potenza e l'integrità del segnale vengono analizzati separatamente, il problema del rumore dell'alimentazione può essere perso.

Pertanto, al fine di dare il gioco completo alle prestazioni di DDR5, tutti i punti chiave del sistema devono includere chip, imballaggi e PCB per l'analisi dell'integrità del segnale dell'influenza dell'alimentazione.Tuttavia, l'analisi di questo livello è un compito complesso. Ha requisiti elevati per gli strumenti hardware e software utilizzati per l'analisi della simulazione per la piattaforma di elaborazione sottostante. La difficoltà e la complessità del design.

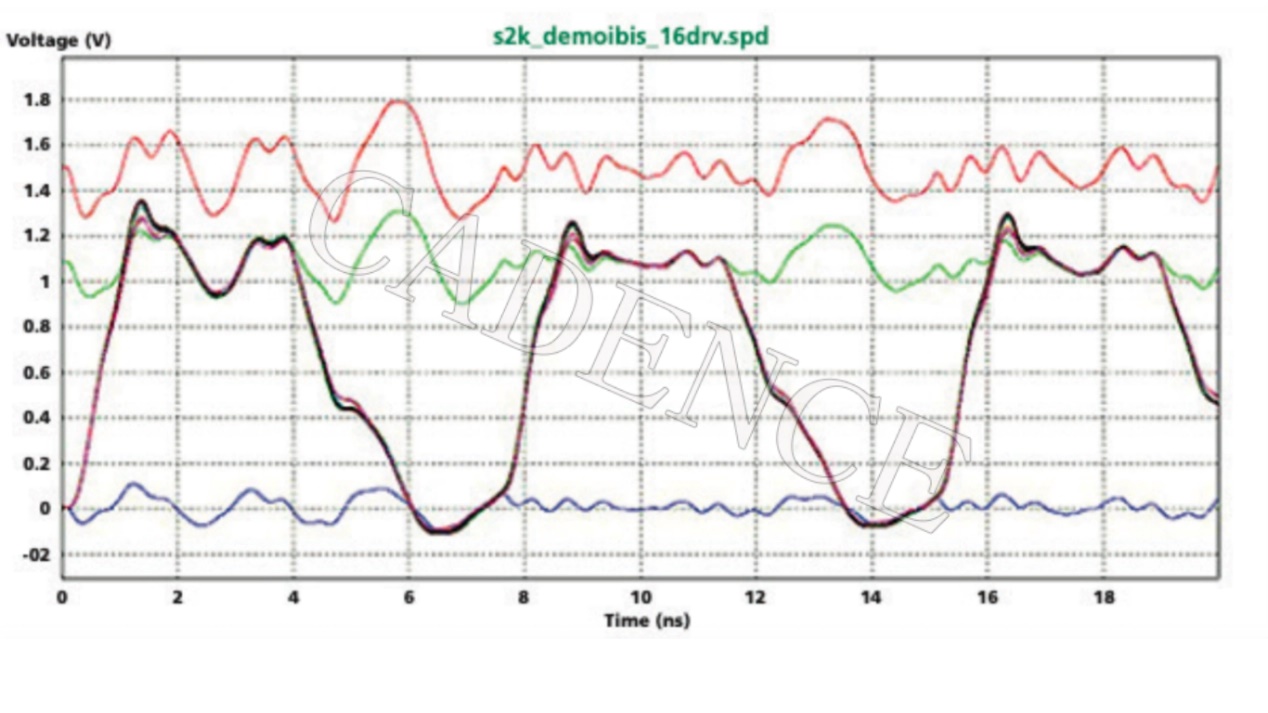

Rilasciare completamente il potenziale di DDR5, cadenza

Già nel 2005, il concetto di "tenendo conto dell'influenza dell'alimentazione" ha debuttato per la prima volta. È un metodo di simulazione di integrità del segnale avanzato che può analizzare i segnali e il rumore di potenza contemporaneamente (Figura 1).La soluzione di integrità del segnale che tiene conto dell'influenza dell'alimentazione deve considerare la riflessione, la corda, gli effetti sequenziali e di altro tipo e dotata di corrispondenti tecniche di ispezione della simulazione e delle regole.Vale la pena notare che per implementare efficacemente la simulazione di integrità del segnale che tiene conto dell'impatto dell'alimentazione, è necessario eseguire nella fase di analisi dopo un'ispezione e cablaggio regolari, poiché l'interazione/accoppiamento del piano e del segnale si verifica Dopo il completamento del cablaggio.

Pertanto, una soluzione completa che tiene conto dell'influenza dell'alimentazione spesso deve essere fornita:

l Un insieme di soluzioni di ispezione rapida per l'attenuazione del segnale e l'alimentazione sui segnali

l può simulare il simulatore del dominio temporale di circuiti di grandi dimensioni (i risultati di più reti di segnale e reti di alimentazione)

L Modellazione della rete di alimentazione e della rete di segnale

L MODELLAZIONE BUFFER INGRESSO/USTPUT (I/O) di alto livello

Figura 1: il risultato dell'integrità del segnale sia dell'influenza dell'alimentazione

Sebbene molti strumenti sul mercato supportino gli standard di modellazione I/O di base che tengono conto dell'influenza dell'alimentazione, con il continuo sviluppo della tecnologia dell'interfaccia di memoria, anche i requisiti del mercato per gli strumenti di integrità del segnale sono in aumento. L'accurato strumento di estrazione per il Il segnale di accoppiamento, l'alimentazione e il segnale di terra su PCB sono rari.

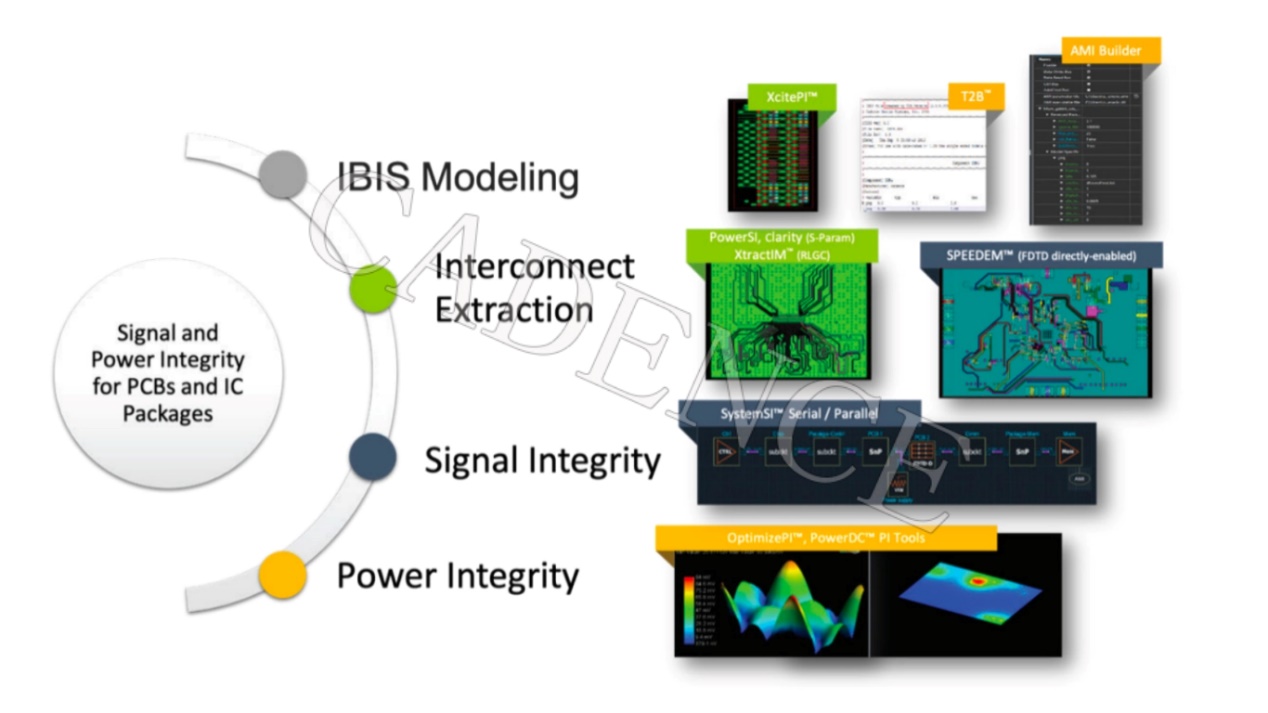

A questo proposito, come impresa leader nel campo della simulazione EDA, la tecnologia di Sigrity X lanciata da Cadence fornisce un'analisi di integrità del segnale dell'influenza dell'alimentazione per DDR4 e DDR5.

La tecnologia Sigrity X non solo realizza l'estrazione precisa di segnali accoppiati, alimentazione e segnali di terra su chip, imballaggi e PCB, ma può anche effettuare una simulazione efficiente su effetti di riflessione, perdita, bandidale e switch sincrono (SSO) agli stessi effetti tempo.I progettisti che utilizzano la tecnologia di sigrity possono convertire rapidamente il modello a livello di transistor in un modello IBIS a livello comportamentale che considera l'influenza del potere, in modo che in poche ore possano fornire precisione, efficiente ed efficiente e completa considerando la simulazione degli effetti dell'alimentazione, che notevolmente, che notevolmente Accorcia il numero originale di originariamente deve essere numerato. Ciclo di progettazione del cielo.(figura 2)

Figura 2: Strumento di integrità del segnale di cadenza e integrità della potenza per il packaging PCB e IC

La tecnologia Sigrity X semplifica il flusso di lavoro, fornisce una simulazione sincrona di progettazione e l'accuratezza del livello di firma per la verifica finale.I segnali, la potenza e i problemi di calore possono essere risolti in ogni fase di progettazione, riducendo così il numero di iterazioni tra i team di progettazione e analisi.I progettisti possono eseguire il motore a livello nucleare nella progettazione del tessuto da disegno per una simulazione ad alta preconcezione, fornendo così un design di alta qualità per i team di analisi da verificare.Successivamente, il team di analisi ha utilizzato il motore di simulazione parallela su larga scala di sigranza per realizzare una simulazione di sistema completo per garantire che l'intero "chip packaging-PCB-shell" soddisfi le specifiche di progettazione e si prepara per la firma.

Questi vantaggi rendono Sigrity X la migliore soluzione per la memoria DDR5 e l'interfaccia 112G.La sua modellazione di interconnessione standard d'oro combina la simulazione del dominio del tempo (simulazione del circuito e del canale) dell'analisi seriale/soluzione (SERDES) e supportando l'interfaccia di modellazione dell'algoritmo IBIS (AMI), che offre ai vantaggi unici, che può quindi estrarre e interfaccia soluzioni complete.

Inoltre, la tecnologia Sigrity Xtractim e Clarity 3D Solver può essere utilizzata insieme, il che consente agli ingegneri di creare modelli di imballaggio completi contenenti segnali di accoppiamento, alimentazione e modelli di interconnessione a terra per vari tipi di imballaggi, che compongono efficacemente la progettazione del packaging e le caratteristiche del pacchetto Il divario tra.

Inoltre, la tecnologia Sigrity Systemi supporta il modello IBIS che può rapidamente connettersi all'influenza dell'alimentazione e del modello di interconnessione che tiene conto dell'influenza dell'alimentazione. Il progettista può determinare rapidamente la situazione peggiore attraverso questa tecnologia e confrontarla con il Standard JEDEC per garantire che DDR4/DDR5 L'interfaccia (compresi i requisiti di velocità del codice Bit) soddisfi tutte le specifiche pertinenti.

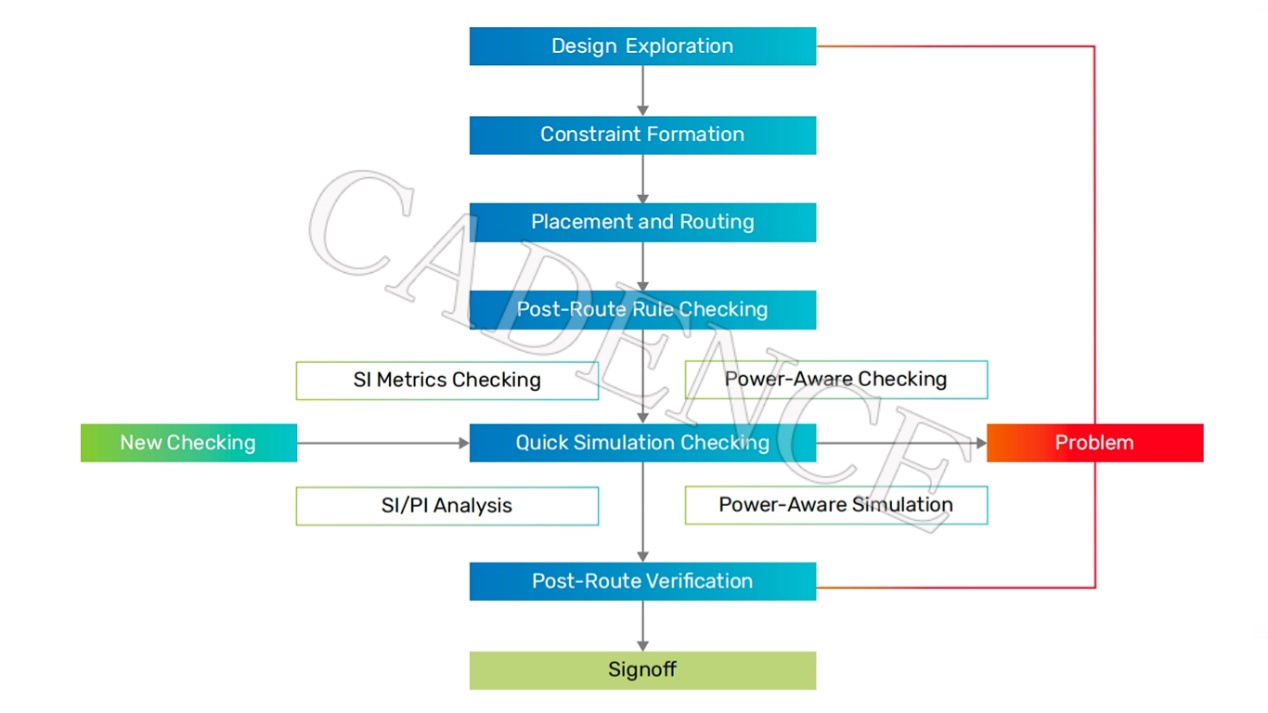

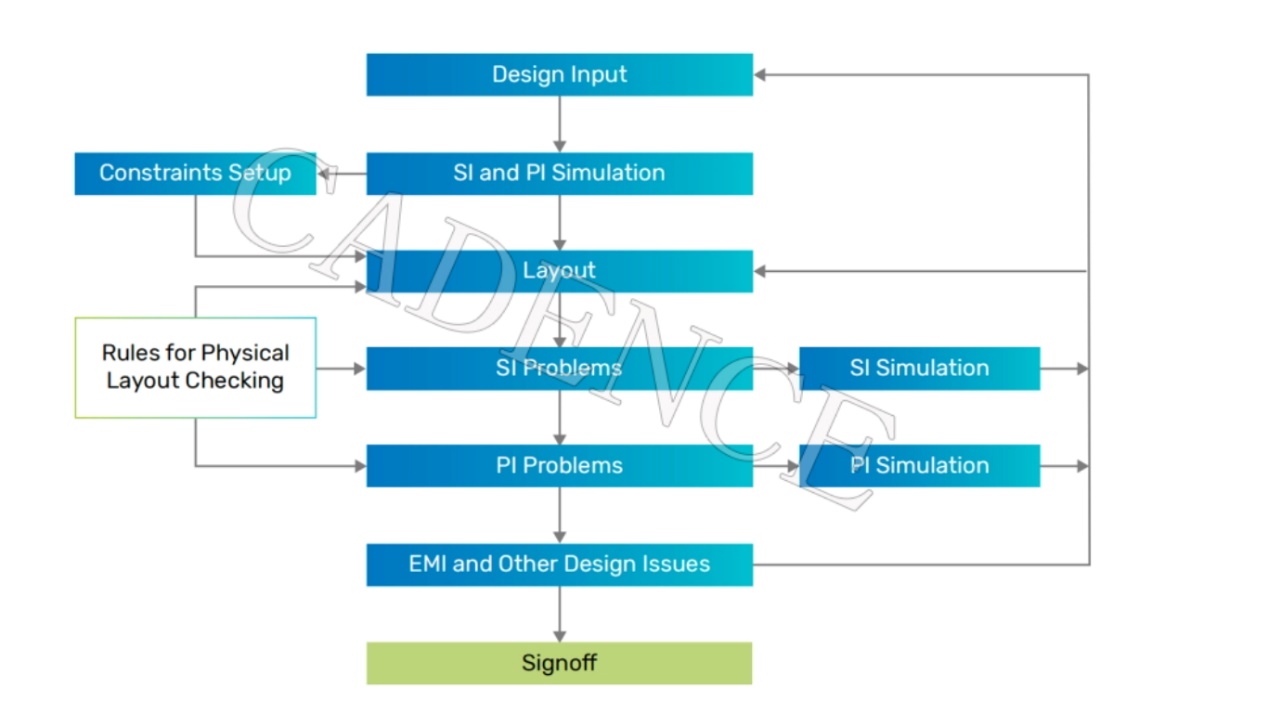

La Figura 3 è il processo di ispezione e simulazione che tiene conto dell'influenza dell'alimentazione, che è in netto contrasto con il tradizionale processo di progettazione basato sui vincoli (Figura 4).Il processo di progettazione dei tradizionali driver di vincolo include principalmente quattro parti: cablaggio pre -layout, formazione di vincoli, ispezione delle regole e verifica post -cablaggio.

Figura 3: Cadence tiene conto del processo di vincolo dell'influenza dell'alimentazione

Vs

Figura 4: Esempio del processo di progettazione del driver di vincoli tradizionale

Tra le molte attuali tecnologie di simulazione, ci sono spesso disconnessioni tra l'analisi del segnale e la rete di distribuzione di potenza (PDN) e ci sono alcune altre carenze.In circostanze normali, secondo la complessità del modello SPICE, a volte utilizzare la simulazione del dominio del tempo per generare modelli accurati di resistenza/induttanza/condensatori (RLC) e talvolta assume un piano di terra ideale.Il modello di dominio temporale ottenuto da questo si basa sulla semplice risposta in frequenza dell'estrazione di simulazione. Sebbene sia più conveniente, è leggermente insufficiente in termini di accuratezza. Per le frequenze più alte, gli ingegneri utilizzeranno i parametri S creati da un dispositivo di risoluzione mista.

In effetti, esiste anche un metodo efficiente per combinare il metodo del dominio del tempo di differenza limitato (FDTD) con il dispositivo di risoluzione mista per espandere la copertura su segnalazione, alimentazione e linea di messa a terra.

Il caso di pratica di questo metodo è lo strumento motore Sigrity Speed2000 di Cadence. Si integra e integra l'uscita di diverse soluzioni per risolvere il cablaggio del circuito, le linee di trasmissione e i problemi di campo elettromagnetico e può visualizzare meglio i dati e l'interazione del piano di potenza/terra a diverse volte.E utilizzare il metodo FDTD per analizzare il layout di IC Packaging e PCB.Fornisce un'importante base di riferimento per l'ulteriore ottimizzazione della progettazione del circuito.

Quando entrano nella fase di firma finale, gli ingegneri di solito tendono a utilizzare metodi di modellazione in onda completa 3D per ottenere una maggiore precisione.Ma questo consumerà più risorse di elaborazione e aumenterà il tempo di simulazione.Per alleviare questo problema, è possibile adottare la divisione e la tecnologia di parallelizzazione.A questo proposito, utilizzando il solutore 3D di chiarezza per un'analisi di analisi degli elementi finiti (FEM) e quindi combinando la tecnologia di sigrity xtractim, i risultati di ciascuna analisi vengono ricambiati per formare un modello di parametro S basato sulla risposta in frequenza, raggiungendo così il intero sistema all'intero sistema o in analisi del design.

Riassumere

Allo stesso tempo del salto tecnologico, la tecnologia è stata migliorata ed è inevitabile gettare nuove sfide per i designer.Sulla strada verso la memoria di DDR5 e le nuove sfide, con la "lama acuta" acuta di Cadence Sigrity X, gli ingegneri possono far fronte con calma ai complessi problemi di integrità del segnale, garantendo che il prodotto non sia solo coerente con le specifiche. Spensone anche Performance, aggiungendo un altro mattone alla strada dell'innovazione futura.