Tin tức

Thời đại DDR5 đang đến gần và những thách thức mới không thể bị bỏ qua

- Tác giả:ROGER

- Phát hành vào:2023-12-04

Trong sự điên cuồng của trí tuệ nhân tạo (AI), học máy (ML) và khai thác dữ liệu, mong muốn xử lý dữ liệu của chúng tôi cho thấy sự tăng trưởng chỉ số chưa từng có.Đối mặt với triển vọng này, chiều rộng của băng thông bộ nhớ đã trở thành một "động mạch" quan trọng trong thời đại kỹ thuật số.Trong số đó, công nghệ DDR (tốc độ dữ liệu kép), được biết đến với tốc độ truyền dữ liệu kép và băng thông cao hơn là bộ nhớ truy cập ngẫu nhiên động (DRAM), đã thúc đẩy đáng kể việc cải thiện hiệu suất máy tính.Từ sự ra đời của thế hệ công nghệ DDR đầu tiên vào năm 2000, đến DDR5 vào năm 2020, mỗi thế hệ công nghệ DDR đã đạt được những cải tiến đáng kể về các khía cạnh khác nhau như băng thông, hiệu suất và tiêu thụ năng lượng.

Ngày nay, cho dù đó là PC, máy tính xách tay hay trí tuệ nhân tạo, các ngành công nghiệp khác nhau đang tăng tốc để tiến tới kỷ nguyên mới của DDR5.Năm nay, thị trường AI thế hệ đang bùng nổ và các máy chủ AI được sử dụng trong các ứng dụng mô hình lớn đã thúc đẩy mạnh mẽ nhu cầu về DDR5.Với sự phục hồi của nhu cầu về thị trường bộ nhớ, các nhà cung cấp chip bộ nhớ đã cho thấy khả năng sản xuất của DDR5 trong quý IV năm nay để thay thế DDR4 hiện tại.

Thời đại mới của DDR5 đã đến, tuy nhiên, một số thách thức cũng đã cản trở sự phát triển hơn nữa của ngành công nghiệp.

Thời đại DDR5: Thách thức thiết kế đằng sau hiệu suất siêu tốc độ cao

Vào tháng 7 năm 2020, tiêu chuẩn công nghệ bộ nhớ DDR5 đã được phát hành chính thức, đánh dấu rằng công nghệ bộ nhớ đã mở một chương mới.DDR5 đã thu hút sự chú ý rộng rãi với băng thông và hiệu suất cao hơn.So với DDR4 trước đây, lợi thế lớn nhất của DDR5 là nó đã giảm đáng kể mức tiêu thụ điện năng và tăng gấp đôi băng thông.Cụ thể, tỷ lệ cao nhất của giao thức phát hành hiện tại của DDR5 đã đạt được 6,4GbpsTần số đồng hồ cũng tăng từ 1,6GHz lên 3,2GHz.

Khi chúng tôi khám phá thêm chi tiết về DDR5, chúng tôi cũng thấy rằng công nghệ mới này đã mang lại một số thách thức kỹ thuật bổ sung.Ví dụ, điện áp cung cấp năng lượng của DDR5 giảm 0,1V 1,2V từ DDR4, đạt 1,1v. Mặc dù điện áp cung cấp điện thấp hơn làm giảm mức tiêu thụ điện năng và kéo dài thời lượng pin, nhưng nó cũng mang lại một số thách thức kỹ thuật, chẳng hạn như kỹ thuật Những thách thức, chẳng hạn như các thách thức kỹ thuật, chẳng hạn như, như một số thách thức kỹ thuật, chẳng hạn như một số thách thức kỹ thuật, chẳng hạn như một số thách thức kỹ thuật, chẳng hạn như, như một số thách thức kỹ thuật, chẳng hạn như Một số thách thức kỹ thuật, chẳng hạn như, chẳng hạn như các thách thức kỹ thuật, chẳng hạn như, chẳng hạn như một số thách thức kỹ thuật. Ví dụ, nó có nhiều khả năng bị xáo trộn bởi tiếng ồn, khiến cho tính toàn vẹn tín hiệu trở nên khó khăn hơn, bởi vì lượng tiếng ồn giữa điện áp Giữa điện áp trong quá trình chuyển đổi tín hiệu ít hơn và có thể ảnh hưởng đến thiết kế.

Một thay đổi lớn khác của DDR5 khác với cách chip quản lý năng lượng (PMIC) của DDR4 được tích hợp trên bo mạch chủ. DDR5 đã chuyển IC quản lý năng lượng (PMIC) từ bo mạch chủ sang mô -đun bộ nhớ trực tiếp kép (DIMM).Điều này cho phép quản lý năng lượng, điều chỉnh điện áp và trình tự năng lượng đến vật lý gần hơn với thiết bị lưu trữ trên mô -đun, cũng giúp đảm bảo tính toàn vẹn của nguồn điện (PI) và tăng cường kiểm soát phương pháp vận hành PMIC.

Ngoài ra, khi tổng số bit dữ liệu không thay đổi, số lượng kênh DIMM từ 1 kênh đến 2 kênh cũng là một tiến bộ quan trọng. Bằng cách truyền dữ liệu vào hai kênh hẹp, nó có thể được tạo ra hiệu quả hơn và được tạo ra hiệu quả hơn Tín hiệu đồng hồ để cải thiện tính toàn vẹn tín hiệu.

Rõ ràng, sự phát triển của tiêu chuẩn DDR5 cũng đã tính đến vấn đề toàn vẹn tín hiệu và việc chuyển PMIC sang mô -đun cũng sẽ phát huy các lợi thế tương ứng.Tuy nhiên, các nhà thiết kế vẫn cần xem xét hiệu ứng tổng thể của tính toàn vẹn tín hiệu của nguồn điện.Như đã đề cập ở trên, DDR5 có tốc độ dữ liệu lên tới 6,4Gbps và tần số đồng hồ hệ thống 3,2GHz. Tiếng ồn công suất có thể gây ra các vấn đề rõ ràng hơn trong hoạt động tốc độ cao này, điều này sẽ ảnh hưởng đến hiệu suất và ổn định của hệ thống.Nếu tính toàn vẹn công suất và tính toàn vẹn tín hiệu được phân tích riêng biệt, vấn đề về tiếng ồn của nguồn cung cấp có thể bị bỏ qua.

Do đó, để chơi đầy đủ cho hiệu suất của DDR5, tất cả các điểm chính của hệ thống phải bao gồm chip, bao bì và PCB để phân tích tính toàn vẹn tín hiệu về ảnh hưởng của cung cấp điện.Tuy nhiên, phân tích cấp độ này là một nhiệm vụ phức tạp. Nó có yêu cầu cao đối với các công cụ phần cứng và phần mềm được sử dụng để phân tích mô phỏng cho nền tảng điện toán cơ bản. Khó khăn và độ phức tạp của thiết kế.

Phát hành đầy đủ tiềm năng của DDR5, Cadence

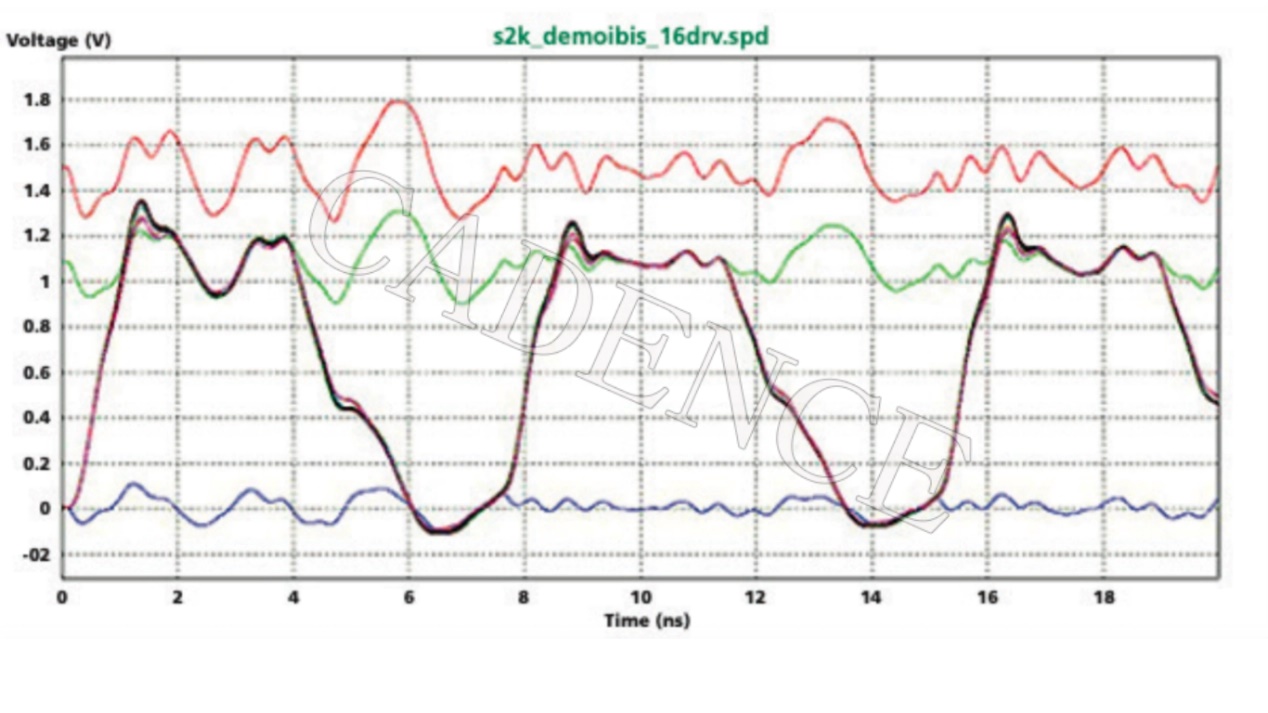

Ngay từ năm 2005, khái niệm "có tính đến ảnh hưởng của nguồn cung cấp điện" lần đầu tiên đã ra mắt. Đây là phương pháp mô phỏng tính toàn vẹn tín hiệu tiên tiến có thể phân tích tín hiệu và nhiễu công suất cùng một lúc (Hình 1).Giải pháp toàn vẹn tín hiệu có tính đến ảnh hưởng của nguồn cung cấp phải xem xét phản xạ, xâu chuỗi, tuần tự và các hiệu ứng khác, và được trang bị các kỹ thuật kiểm tra mô phỏng và quy tắc tương ứng.Điều đáng chú ý là để thực hiện hiệu quả mô phỏng tính toàn vẹn tín hiệu có tính đến tác động của cung cấp điện, cần phải thực hiện trong giai đoạn phân tích sau khi kiểm tra và nối dây thường xuyên, vì sự tương tác/khớp nối của mặt phẳng và tín hiệu xảy ra Sau khi hệ thống dây điện hoàn thành.

Do đó, một giải pháp hoàn chỉnh có tính đến ảnh hưởng của nguồn cung cấp điện thường cần được cung cấp:

l Một tập hợp các giải pháp kiểm tra nhanh để suy giảm tín hiệu và cung cấp điện cho các tín hiệu

l Có thể mô phỏng Trình mô phỏng miền thời gian của các mạch lớn (kết quả của nhiều mạng tín hiệu và mạng nguồn)

L Mạng điện và mô hình mạng tín hiệu

l Mô hình bộ đệm đầu vào/đầu ra (I/O) cao (I/O)

Hình 1: Kết quả của tính toàn vẹn tín hiệu của cả ảnh hưởng của nguồn cung cấp năng lượng

Mặc dù nhiều công cụ trên thị trường hỗ trợ các tiêu chuẩn mô hình I/O cơ bản có tính đến ảnh hưởng của cung cấp điện, với sự phát triển liên tục của công nghệ giao diện bộ nhớ, các yêu cầu của thị trường đối với các công cụ toàn vẹn tín hiệu cũng đang tăng lên. Tín hiệu khớp nối, nguồn điện và tín hiệu mặt đất trên PCB là rất hiếm.

Về vấn đề này, với tư cách là một doanh nghiệp hàng đầu trong lĩnh vực mô phỏng EDA, công nghệ Sigrity X được đưa ra bởi Cadence cung cấp phân tích tính toàn vẹn tín hiệu về ảnh hưởng của cung cấp năng lượng cho DDR4 và DDR5.

Công nghệ x không chỉ nhận ra việc trích xuất chính xác các tín hiệu kết hợp, nguồn điện và tín hiệu mặt đất trên chip, bao bì và PCB, mà còn có thể tạo ra mô phỏng hiệu quả về phản xạ, mất, băng thông và đầu ra công tắc đồng bộ (SSO) thời gian.Các nhà thiết kế sử dụng công nghệ sigrity có thể nhanh chóng chuyển đổi mô hình bóng bán dẫn thành mô hình IBIS hành vi hành vi xem xét ảnh hưởng của sức mạnh, để trong vài giờ, nó có thể cung cấp chính xác, hiệu quả và toàn diện khi xem xét mô phỏng các hiệu ứng cung cấp năng lượng, điều này rút ngắn số lượng ban đầu cần được đánh số. Chu kỳ thiết kế trên bầu trời.(Hình 2)

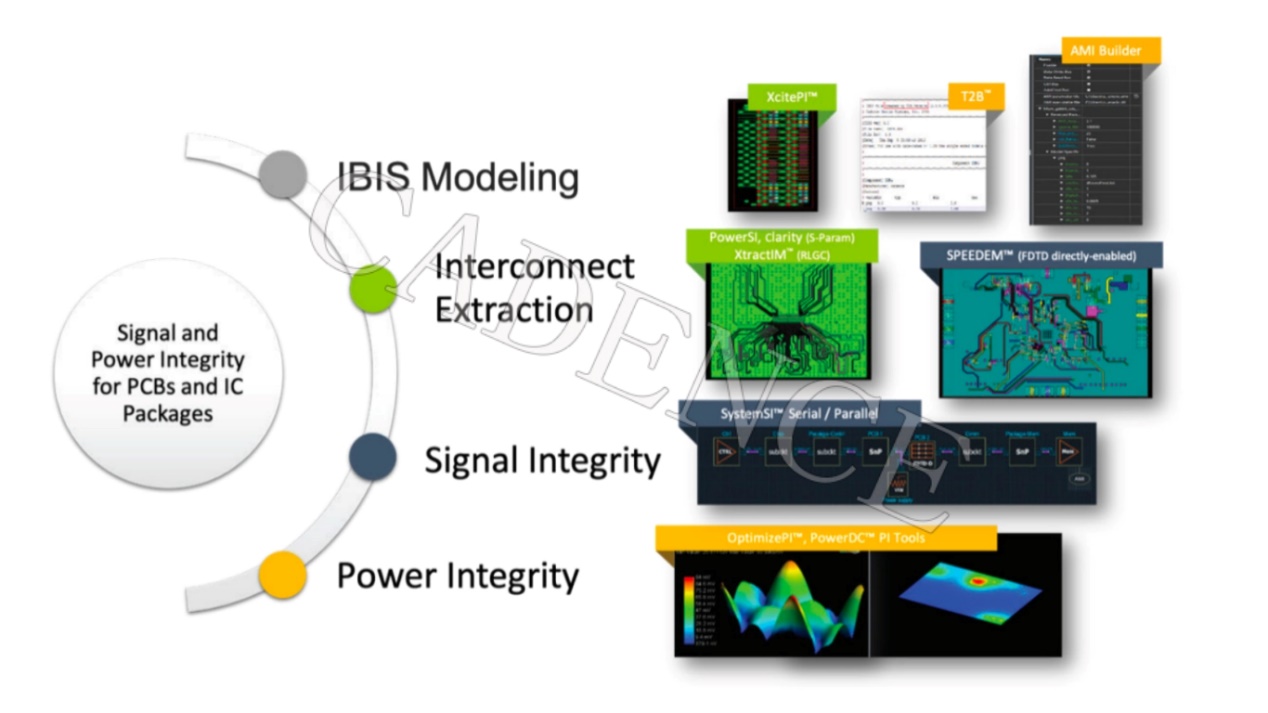

Hình 2: Tính toàn vẹn tín hiệu Cadence và công cụ toàn vẹn năng lượng cho bao bì PCB và IC

Công nghệ Sigrity X đơn giản hóa quy trình công việc, cung cấp mô phỏng đồng bộ thiết kế và độ chính xác của mức ký để xác minh cuối cùng.Tín hiệu, năng lượng và các vấn đề nhiệt có thể được giải quyết ở mỗi giai đoạn thiết kế, do đó giảm số lần lặp lại giữa các nhóm thiết kế và phân tích.Các nhà thiết kế có thể chạy động cơ hạt nhân trong thiết kế vải vẽ để mô phỏng cao, do đó cung cấp thiết kế chất lượng cao cho các nhóm phân tích để xác minh.Sau đó, nhóm phân tích đã sử dụng động cơ mô phỏng song song quy mô lớn của Sigrity để thực hiện mô phỏng hệ thống đầy đủ để đảm bảo rằng toàn bộ "vỏ PCB đóng gói chip" đáp ứng các thông số kỹ thuật thiết kế và chuẩn bị cho việc ký kết.

Những ưu điểm này làm cho sigrity x trở thành giải pháp tốt nhất cho bộ nhớ DDR5 và giao diện 112G.Mô hình kết nối tiêu chuẩn vàng của nó kết hợp mô phỏng miền thời gian (mô phỏng mạch và kênh) của phân tích nối tiếp/giải pháp (SERDES) và hỗ trợ giao diện mô hình thuật toán IBIS (AMI), mang lại lợi thế độc đáo của Cadence, do đó có thể trích xuất và ký kết giao diện. hoàn thành giải pháp.

Có thể sử dụng công nghệ Sigrity Xtractim và Clarity 3D giải quyết cùng nhau, cho phép các kỹ sư tạo ra các mô hình đóng gói hoàn chỉnh có chứa tín hiệu khớp nối, cung cấp năng lượng và các mô hình kết nối nối đất cho các loại bao bì khác nhau, tạo nên hiệu quả cho các đặc tính thiết kế và gói bao bì Khoảng cách giữa.

Ngoài ra, công nghệ Sigrity Systemsi hỗ trợ mô hình IBIS có thể nhanh chóng kết nối với ảnh hưởng của cung cấp năng lượng và mô hình kết nối có tính đến ảnh hưởng của nguồn điện. Nhà thiết kế có thể nhanh chóng xác định tình huống xấu nhất thông qua công nghệ này và so sánh nó với Tiêu chuẩn JEDEC để đảm bảo rằng DDR4/DDR5 giao diện (bao gồm các yêu cầu về tỷ lệ mã không bit) đáp ứng tất cả các thông số kỹ thuật có liên quan.

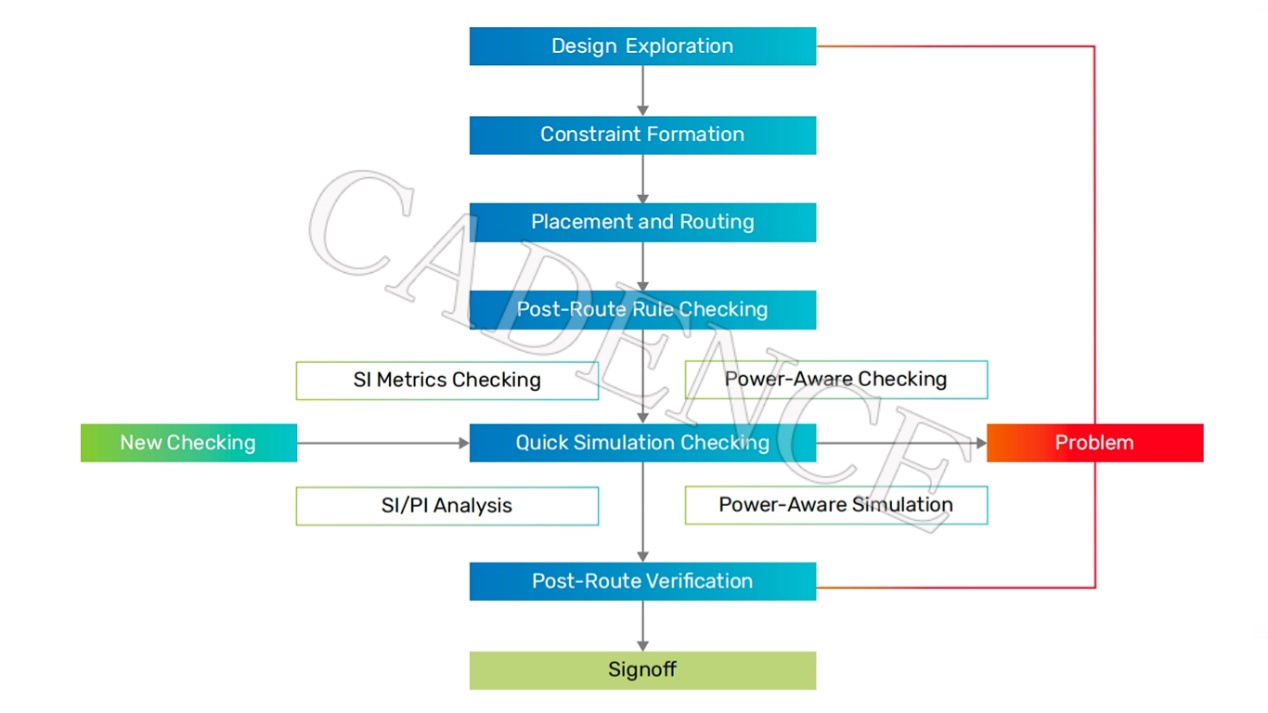

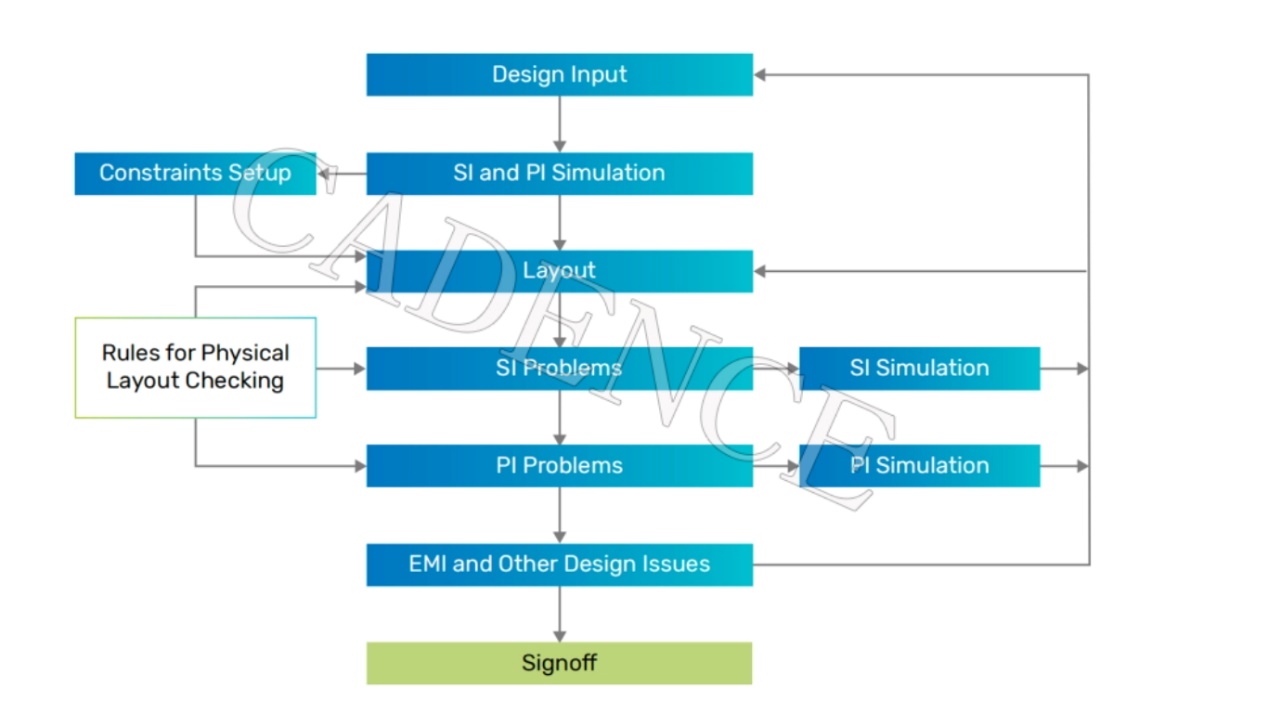

Hình 3 là quá trình kiểm tra và mô phỏng có tính đến ảnh hưởng của nguồn cung cấp năng lượng, trái ngược hoàn toàn với quy trình thiết kế được giới hạn truyền thống (Hình 4).Quá trình thiết kế của các trình điều khiển ràng buộc truyền thống chủ yếu bao gồm bốn phần: hệ thống dây điện trước, hình thành ràng buộc, kiểm tra quy tắc và xác minh sau.

Hình 3: Cadence tính đến quá trình điều khiển ràng buộc về ảnh hưởng của nguồn cung cấp điện

Vs

Hình 4: Ví dụ về quy trình thiết kế trình điều khiển ràng buộc truyền thống

Trong số nhiều công nghệ mô phỏng hiện tại, thường có sự ngắt kết nối giữa phân tích tín hiệu và mạng phân phối năng lượng (PDN) và có một số thiếu sót khác.Trong các trường hợp bình thường, theo độ phức tạp của mô hình Spice, đôi khi sử dụng mô phỏng miền thời gian để tạo ra các mô hình điện trở/điện trở/điện thoại chính xác (RLC), và đôi khi nó giả định một mặt phẳng mặt đất lý tưởng.Mô hình miền thời gian thu được từ điều này dựa trên phản ứng tần số đơn giản của trích xuất mô phỏng. Mặc dù thuận tiện hơn, nhưng nó không đủ về độ chính xác. Đối với tần số cao hơn, các kỹ sư sẽ sử dụng các tham số S được tạo bởi một thiết bị giải quyết hỗn hợp.

Trên thực tế, cũng có một phương pháp hiệu quả để kết hợp phương pháp Miền thời gian chênh lệch hạn chế (FDTD) với thiết bị giải quyết hỗn hợp để mở rộng phạm vi bảo hiểm cho tín hiệu, nguồn điện và đường nối đất.

Trường hợp thực hành thành công của phương pháp này là công cụ động cơ Sigrity Speed2000 của Cadence. Nó tích hợp và tích hợp đầu ra của một số giải pháp để giải quyết hệ thống dây điện, đường truyền và các vấn đề trường điện từ và có thể hiển thị tốt hơn dữ liệu và tương tác mặt phẳng điện/mặt đất ở các khác nhau thời gian.Và sử dụng phương pháp FDTD để phân tích bố cục bao bì IC và PCB.Nó cung cấp một cơ sở tham khảo quan trọng cho việc tối ưu hóa hơn nữa của thiết kế mạch.

Khi bước vào giai đoạn ký cuối cùng, các kỹ sư thường có xu hướng sử dụng các phương pháp mô hình 3D toàn bộ để đạt được độ chính xác cao hơn.Nhưng điều này sẽ tiêu thụ nhiều tài nguyên điện toán hơn và tăng thời gian mô phỏng.Để giảm bớt vấn đề này, công nghệ phân chia và song song có thể được thông qua.Về vấn đề này, bằng cách sử dụng bộ giải 3D Clarity để phân tích phân tích phần tử hữu hạn (FEM), sau đó kết hợp công nghệ Sigrity Xtractim, kết quả của mỗi phân tích được xác định lại để tạo thành một mô hình tham số S dựa trên phản ứng tần số, do đó đạt được Toàn bộ hệ thống cho toàn bộ hệ thống hoặc phân tích chính xác và phân tích thiết kế.

Tóm tắt

Đồng thời với bước nhảy vọt công nghệ, công nghệ đã được cải thiện và không thể tránh khỏi những thách thức mới cho các nhà thiết kế.Trên đường tới bộ nhớ DDR5 và những thách thức mới, với "lưỡi kiếm sắc bén" của Cadence Sigrity X, các kỹ sư có thể bình tĩnh đối phó với các vấn đề phức tạp về tính toàn vẹn tín hiệu, đảm bảo rằng sản phẩm không chỉ phù hợp với các thông số kỹ thuật. Nó cũng tỏa sáng trong Hiệu suất, thêm một viên gạch khác vào con đường đổi mới trong tương lai.