Aktualności

Zbliża się era DDR5, a nowych wyzwań nie można zignorować

- Autor:ROGER

- Zwolnij na:2023-12-04

W szaleństwie sztucznej inteligencji (AI), uczenia maszynowego (ML) i eksploracji danych nasze pragnienie przetwarzania danych wykazuje niespotykany wzrost indeksu.W obliczu tej perspektywy szerokość przepustowości pamięci stała się kluczowym „tętnicami” w erze cyfrowej.Wśród nich technologia DDR (podwójna szybkość danych), znana z podwójnej szybkości transmisji danych i wyższej przepustowości jako dynamiczna pamięć o dostępie losowym (DRAM), znacznie promowała poprawę wydajności komputera.Od narodzin pierwszej generacji technologii DDR w 2000 r., Do DDR5 w 2020 r., Każda generacja technologii DDR osiągnęła znaczną poprawę w różnych aspektach, takich jak przepustowość, wydajność i zużycie energii.

Dzisiaj, niezależnie od tego, czy jest to PC, laptop, czy sztuczna inteligencja, różne branże przyspieszają, aby przejść do nowej ery DDR5.W tym roku rynek generacji sztucznej inteligencji rozwija się, a serwery AI stosowane w dużych modelach energicznie promowały popyt na DDR5.Wraz z odzyskaniem zapotrzebowania na rynek pamięci dostawcy układów pamięci wykazali zdolność produkcyjną DDR5 w czwartym kwartale tego roku, aby stopniowo zastąpić obecny DDR4.

Nadeszła nowa era DDR5, jednak niektóre wyzwania utrudniały również dalszy rozwój branży.

ERA DDR5: Wyzwania projektowe stojące za ultra -high -prędkości

W lipcu 2020 r. Standard technologii pamięci DDR5 został oficjalnie wydany, oznaczając, że technologia pamięci otworzyła nowy rozdział.DDR5 przyciągnął szeroką uwagę przy wyższej przepustowości i wydajności.W porównaniu z poprzednim DDR4, największą zaletą DDR5 jest to, że znacznie zmniejszył zużycie energii i podwoił przepustowość.W szczególności najwyższa szybkość obecnego protokołu uwalniania DDR5 6,4 Gb / sCzęstotliwość zegara wzrosła również z 1,6 GHz do 3,2 GHz.

Kiedy badamy więcej szczegółów na temat DDR5, stwierdzamy również, że ta nowa technologia przyniosła dodatkowe wyzwania techniczne.Na przykład napięcie zasilania DDR5 zmniejsza się o 0,1 V o 1,2 V od DDR4, osiągając 1,1 V. Chociaż niższe napięcie zasilania zmniejsza zużycie energii i wydłuża żywotność baterii, również stanowi pewne wyzwania techniczne, takie jak techniczne Wyzwania, takie jak wyzwania techniczne, takie jak niektóre wyzwania techniczne, takie jak niektóre wyzwania techniczne, takie jak niektóre wyzwania techniczne, takie jak niektóre wyzwania techniczne, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak, takie jak Niektóre wyzwania techniczne, takie jak wyzwania techniczne, takie jak niektóre wyzwania techniczne. Na przykład jest to bardziej prawdopodobne przez szum, co sprawia, że integralność sygnału jest trudniejsza, ponieważ ilość szumu między napięciem napięcia Pomiędzy napięciem podczas przełącznika sygnału jest mniejsze i może wpływać na konstrukcję.

Kolejna poważna zmiana DDR5 różni się od sposobu, w jaki układ zarządzania energią (PMIC) DDR4 jest zintegrowany na płycie głównej. DDR5 przeniósł IC zarządzanie energią (PMIC) z płyty głównej do modułu pamięci bezpośredniej (DIMM).Umożliwia to zarządzanie energią, regulację napięcia i sekwencję mocy -N bliżej urządzenia magazynowego w module, co również pomaga zapewnić integralność zasilacza (PI) i zwiększyć kontrolę metody operacji PMIC.

Ponadto, gdy całkowita liczba bitów danych pozostaje niezmieniona, liczba kanałów DIMM od 1 kanału do 2 kanałów jest również ważnym postępem. Przekazując dane do dwóch wąskich transmisji kanałów, można je bardziej skutecznie wygenerować i wygenerować bardziej skutecznie przypisanie Sygnały zegara w celu poprawy integralności sygnału.

Oczywiście opracowanie standardu DDR5 uwzględniło również problem integralności sygnału, a przeniesienie PMIC do modułu również wywiera odpowiednie zalety.Jednak projektanci nadal muszą wziąć pod uwagę ogólny wpływ integralności sygnału zasilania.Jak wspomniano powyżej, DDR5 ma szybkość danych do 6,4 Gb / s i częstotliwość zegara systemowego 3,2 GHz. Szum mocy może powodować bardziej oczywiste problemy w tej wysokiej obsłudze, co wpłynie na wydajność i stabilność systemu.Jeśli integralność energii i integralność sygnału zostaną analizowane osobno, problem szumu zasilacza można pominąć.

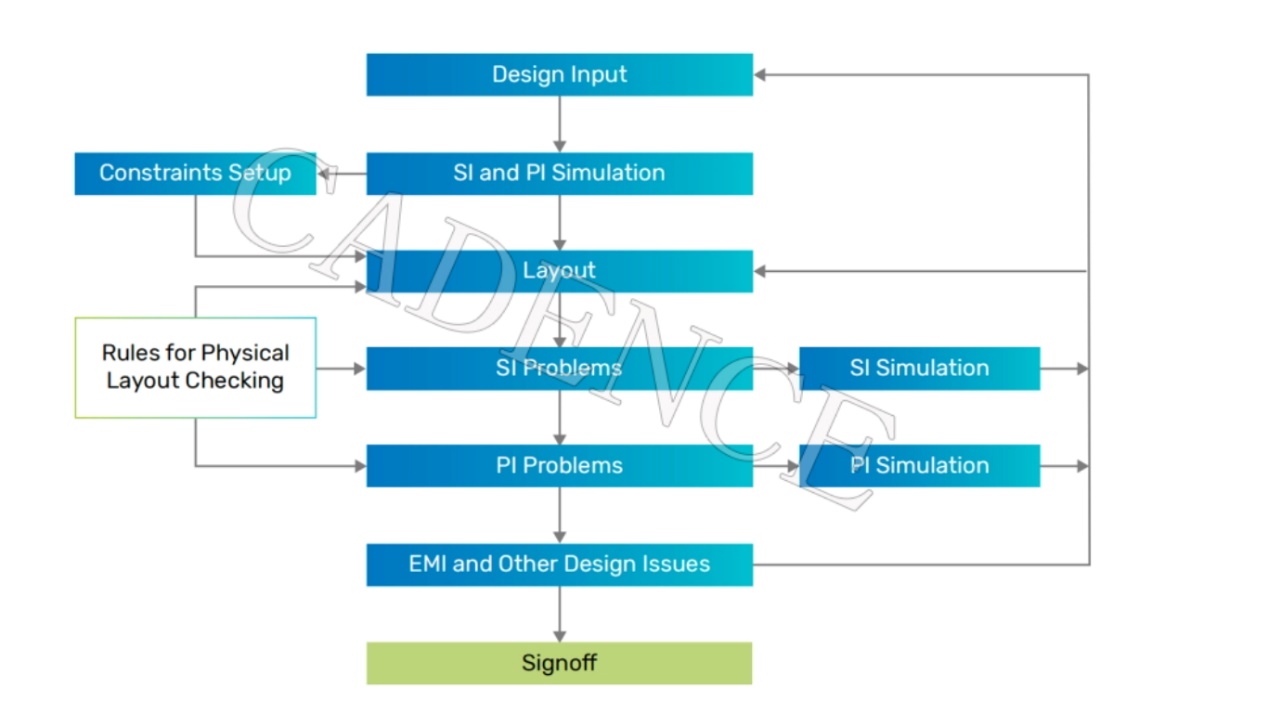

Dlatego, aby zapewnić pełną grę wydajności DDR5, wszystkie kluczowe punkty systemu muszą zawierać układy, opakowanie i płytkę PCB do analizy integralności sygnału wpływu zasilania.Jednak analiza tego poziomu jest złożonym zadaniem. Ma wysokie wymagania dotyczące narzędzi sprzętowych i programowych używanych do analizy symulacji dla platformy obliczeniowej. Trudność i złożoność projektowania.

W pełni uwalniają potencjał DDR5, Cadence

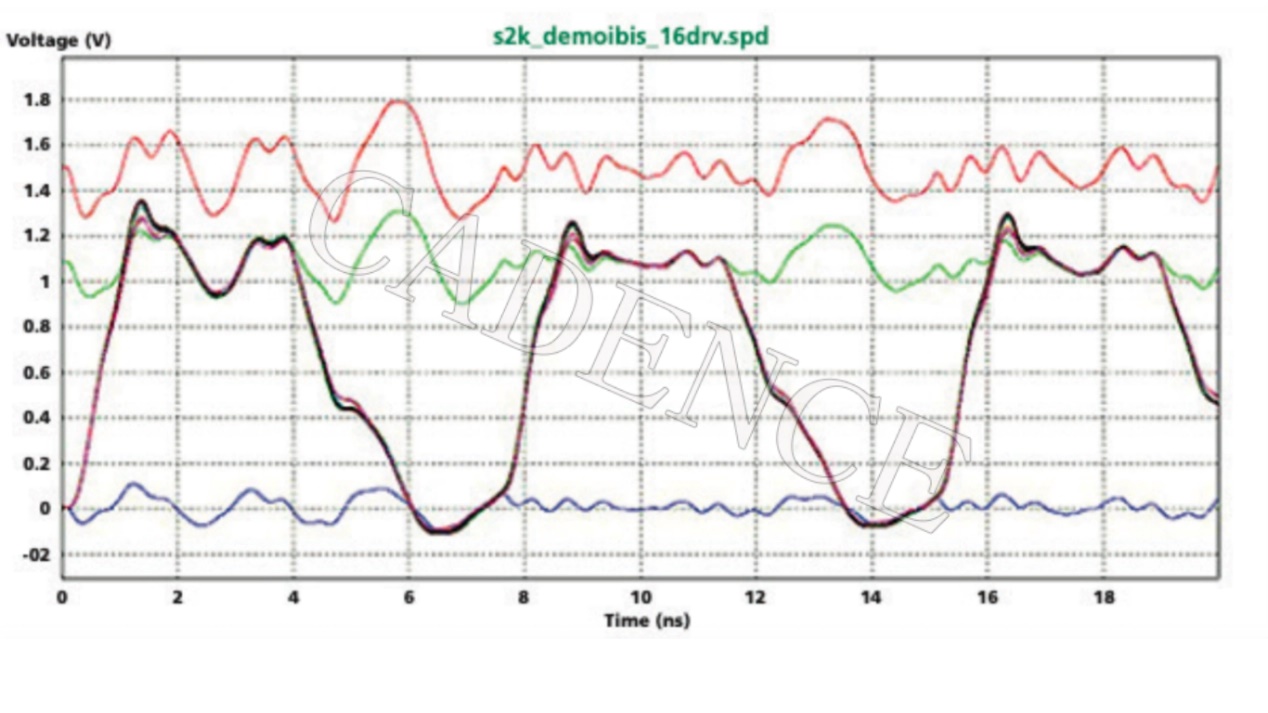

Już w 2005 r. Po raz pierwszy zadebiutowała koncepcja „uwzględnienia wpływu zasilania”. Jest to metoda symulacji zaawansowanej integralności sygnału, która może analizować sygnały i szum energetyczny w tym samym czasie (ryc. 1).Rozwiązanie integralności sygnału, które uwzględnia wpływ zasilania, musi rozważyć refleksję, string, sekwencyjne i inne efekty oraz wyposażone w odpowiednie techniki symulacji i reguł.Warto zauważyć, że w celu skutecznego wdrożenia symulacji integralności sygnału, która uwzględnia wpływ zasilania, konieczne jest wykonanie w fazie analizy po regularnej kontroli i okablowaniu, ponieważ następuje interakcja/sprzężenie płaszczyzny i sygnału Po zakończeniu okablowania.

Dlatego często należy zapewnić pełne rozwiązanie, które uwzględnia wpływ zasilania:

l Zestaw rozwiązań szybkiej inspekcji do tłumienia sygnału i zasilania sygnałów

L może symulować symulator domeny czasu dużych obwodów (wyniki wielu sieci sygnałowych i sieci zasilania)

L Modelowanie sieci mocy i sieci sygnałów

l Wysokie wejście/wyjście (I/O) Modelowanie buforu

Rysunek 1: Wynik integralności sygnału zarówno wpływu zasilania

Chociaż wiele narzędzi na rynku obsługuje podstawowe standardy modelowania we/wy, które uwzględniają wpływ zasilania, wraz z ciągłym opracowywaniem technologii interfejsu pamięci, wymagania rynku dotyczące narzędzi integralności sygnałów również rosną. Sygnał sprzężenia, zasilanie i sygnał uziemienia na PCB są rzadkie.

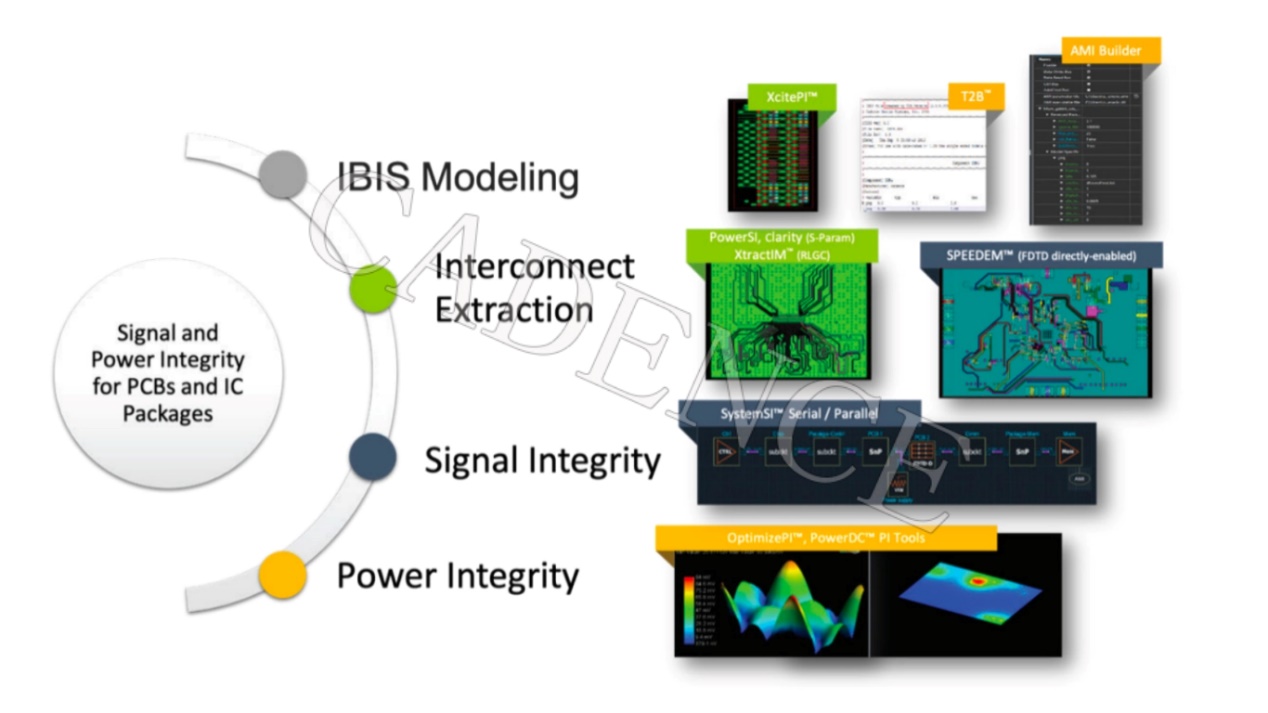

W związku z tym, jako wiodące przedsiębiorstwo w dziedzinie symulacji EDA, technologia SIGRITY X uruchomiona przez Cadence zapewnia analizę integralności sygnału wpływu zasilania DDR4 i DDR5.

Technologia SIGRITY X nie tylko zdaje sobie sprawę z dokładnej ekstrakcji sprzężonych sygnałów, zasilaczy i sygnałów uziemienia na układach, opakowaniach i PCB, ale także może wykonywać efektywną symulację na temat efektów odbicia, straty, bandidal i synchronicznego wyjścia przełącznika (SSO) w tym samym czas.Projektanci korzystający z technologii SIGRITY mogą szybko przekształcić model poziomu tranzystorowego na model IBI na poziomie behawioralnym, który rozważa wpływ energii, dzięki czemu w ciągu kilku godzin może zapewnić precyzyjne, wydajne i kompleksowe, biorąc pod uwagę symulację efektów zasilania, co znacznie Skraca pierwotnie liczbę pierwotnie musi być ponumerowana. Cykl projektowania nieba.(Rysunek 2)

Rysunek 2: Narzędzie integralności sygnału kadencji i integralności mocy do opakowania PCB i IC

Technologia Sigrity X upraszcza przepływ pracy, zapewnia symulację synchroniczną projektową i dokładność poziomu podpisania do ostatecznej weryfikacji.Sygnały, zasilanie i problemy cieplne można rozwiązać na każdym etapie projektowania, zmniejszając w ten sposób liczbę iteracji między zespołami projektowymi i analizami.Projektanci mogą uruchomić silnik na poziomie jądrowym w projektowaniu szmatki do symulacji o wysokiej wymierności, zapewniając w ten sposób projektowanie o wysokiej jakości projekty do weryfikacji.Później zespół analityczny wykorzystał dużą równoległą symulację silnika SIGrity, aby wykonać pełną symulację systemu, aby zapewnić, że cała „chip-pakowanie-pcb-powłoka” spełnia specyfikacje projektowe i przygotowuje się do podpisania.

Zalety te sprawiają, że SIGrity X jest najlepszym rozwiązaniem dla pamięci DDR5 i interfejsu 112G.Jego złote standardowe modelowanie interkonnect łączy symulację domeny czasowej (symulacja obwodu i kanału) analizy szeregowej/rozwiązania (SERDES) i obsługuje interfejs modelowania algorytmu IBIS (AMI), który daje unikalne zalety kadencji, w ten sposób może wyodrębnić i podpisać zgodność interfejsu. kompletne rozwiązania.

Ponadto technologia SIGRITY XTRACTIM i CLARITY 3D Solver może być stosowana w połączeniu, co pozwala inżynierom tworzyć kompletne modele opakowań zawierające sygnały sprzęgające, zasilanie i uziemienie modele połączeń dla różnych rodzajów opakowań, które skutecznie nadają się do projektowania opakowań i charakterystyki pakietów Przerwa pomiędzy.

Ponadto technologia Sigrity SystemsI obsługuje model IBIS, który może szybko połączyć się z wpływem zasilania i modelem połączeń, który uwzględnia wpływ zasilania. Projektant może szybko określić najgorszą sytuację za pomocą tej technologii i porównać go z nim z nim i porównać go z nim Standard JEDEC w celu zapewnienia, że DDR4/DDR5 interfejs (w tym wymagania dotyczące szybkości kodu beztłuszczowego) spełnia wszystkie istotne specyfikacje.

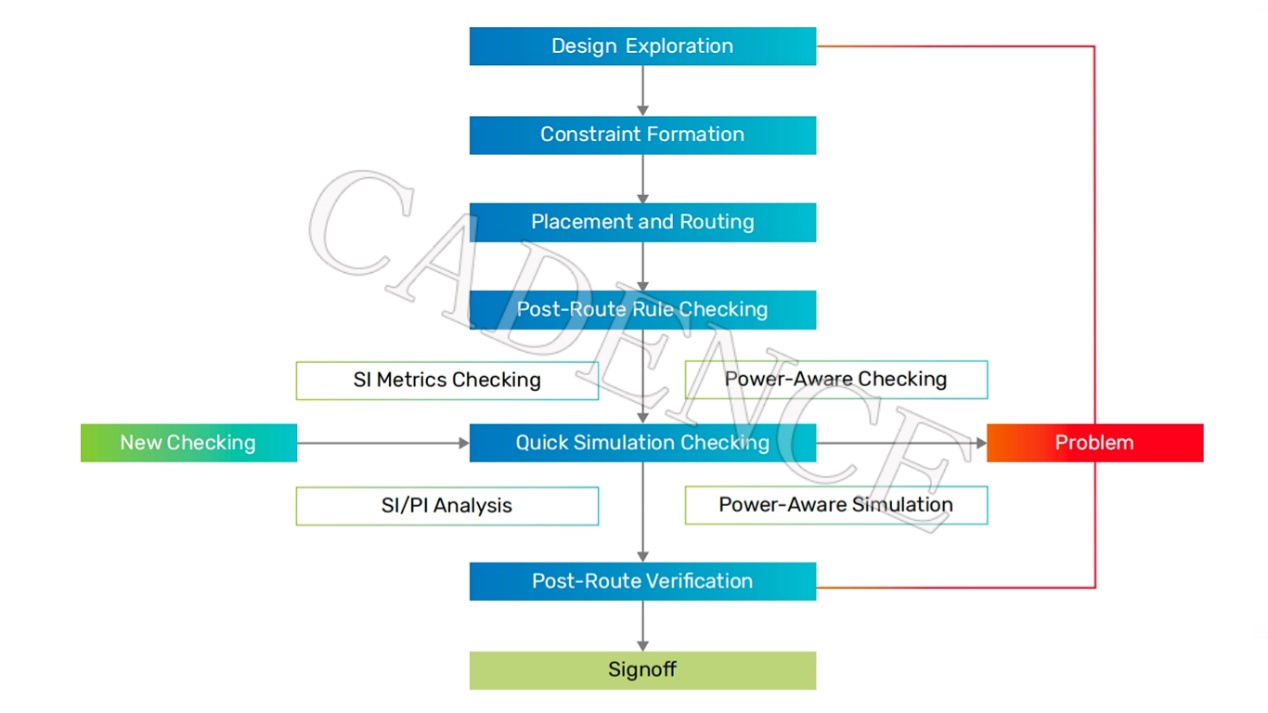

Rycina 3 to proces kontroli i symulacji, który uwzględnia wpływ zasilania, który jest wyraźnie sprzeczny z tradycyjnym procesem projektowym opartym na ograniczeniu (ryc. 4).Proces projektowania tradycyjnych sterowników ograniczeń obejmuje głównie cztery części: okablowanie przed Layout, tworzenie ograniczeń, kontrola zasad i weryfikację po zawodach.

Rysunek 3: Kadencja uwzględnia proces ograniczenia wpływu na wpływ zasilania

VS

Rysunek 4: Przykład tradycyjnego procesu projektowania sterowników ograniczenia

Wśród wielu obecnych technologii symulacyjnych często występują rozłączenia między analizą sygnału a siecią dystrybucji energii (PDN), a niektóre inne niedociągnięcia.W normalnych okolicznościach, zgodnie z złożonością modelu przypraw, czasami używaj symulacji dziedziny czasowej, aby wygenerować dokładne modele oporności/indukcyjności/kondensatorów (RLC), a czasem zakłada idealną płaszczyznę uziemienia.Uzyskany z tego modelu domeny czasowej opiera się na prostej odpowiedzi częstotliwości ekstrakcji symulacji. Chociaż jest on wygodniejszy, jest nieco niewystarczający pod względem dokładności. W przypadku wyższych częstotliwości inżynierowie używają parametrów S tworzonych przez mieszane urządzenie rozwiązywane.

W rzeczywistości istnieje również wydajna metoda łączenia metody ograniczonej różnicy czasowej (FDTD) z mieszanym urządzeniem rozwiązywanym w celu rozszerzenia pokrycia na linię sygnału, zasilania i uziemienia.

Udanym przypadkiem praktyki tej metody jest narzędzie silnika SIGRITY SIGRITY 2000. Integruje i integruje wyjście kilku roztworów w celu rozwiązania okablowania obwodu, linii przesyłowych i problemów pola elektromagnetycznego oraz może lepiej wyświetlać interakcję danych i zasilanie/płaszczyznę uziemienia w różnych czasy.I użyj metody FDTD do analizy układu opakowania IC i PCB.Zapewnia ważną podstawę odniesienia do dalszej optymalizacji projektowania obwodu.

Podczas wejścia na etap końcowego podpisywania inżynierowie zwykle stosują metody modelowania pełnego fali 3D w celu uzyskania wyższej dokładności.Ale to pochłonie więcej zasobów obliczeniowych i zwiększy czas symulacji.Aby złagodzić ten problem, można przyjąć technologię podziału i równoległości.W związku z tym, stosując solver Clarity 3D do analizy analizy elementów skończonych (MES), a następnie łącząc technologię Sigrity Xtractim, wyniki każdej analizy są ponownie przydatne w celu utworzenia modelu parametrów S na podstawie odpowiedzi częstotliwościowej, osiągając w ten sposób Cały system do całego systemu lub w -głębokości i precyzyjnej analizie projektowania.

Podsumować

W tym samym czasie, co skok technologiczny, technologia została ulepszona i nieuniknione jest stawianie nowych wyzwań dla projektantów.W drodze do pamięci DDR5 i nowych wyzwań, z ostrym „ostrym ostrzem” Cadence Sigrity X, inżynierowie mogą spokojnie poradzić sobie ze złożonymi problemami integralności sygnału, zapewniając, że produkt jest nie tylko zgodny ze specyfikacjami. On również świeci w IN Wydajność, dodając kolejną cegłę do drogi przyszłych innowacji.