Новости

Эпоха DDR5 приближается, и новые проблемы нельзя игнорировать

- автор:ROGER

- Освободить:2023-12-04

В безумии искусственного интеллекта (ИИ), машинного обучения (ML) и интеллектуального анализа данных наше стремление к обработке данных показывает беспрецедентный рост индекса.Столкнувшись с этой перспективой, ширина пропускной способности памяти стала ключевыми «артериями» в эпоху цифровых технологий.Среди них технология DDR (двойная скорость передачи данных), известная по скоростям передачи данных и более высокой пропускной способностью как динамическая память о случайном доступе (DRAM), значительно способствует улучшению производительности компьютера.От рождения технологии DDR в первом поколении в 2000 году до DDR5 в 2020 году, каждая генерация технологии DDR достигла значительных улучшений в различных аспектах, таких как пропускная способность, производительность и энергопотребление.

Сегодня, будь то ПК, ноутбук или искусственный интеллект, различные отрасли ускоряются, чтобы перейти к новой эре DDR5.В этом году рынок искусственного интеллекта поколения процветает, а серверы ИИ, используемые в приложениях крупных моделей, энергично способствуют спросу на DDR5.При восстановлении рынка спроса на память поставщики чипов памяти показали производственную мощность DDR5 в четвертом квартале этого года, чтобы постепенно заменить текущий DDR4.

Новая эра DDR5 прибыла, однако некоторые проблемы также препятствовали дальнейшему развитию отрасли.

DDR5 ERA: Проблемы дизайна, лежащая в основе ультра -высокой производительности

В июле 2020 года был официально опубликован стандарт технологий памяти DDR5, отмечая, что технология памяти открыла новую главу.DDR5 привлек широкое внимание с помощью более высокой пропускной способности и производительности.По сравнению с предыдущим DDR4, самое большое преимущество DDR5 заключается в том, что он значительно снизил потребление мощности и удвоило пропускную способность.В частности, достигнут самый высокий уровень протокола текущего выпуска DDR5. 6,4 Гбит / сЧастота такта также увеличилась с 1,6 ГГц до 3,2 ГГц.

Когда мы исследуем более подробную информацию о DDR5, мы также обнаруживаем, что эта новая технология принесла некоторые дополнительные технические проблемы.Например, напряжение источника питания DDR5 уменьшается на 0,1 В на 1,2 В от DDR4, достигая 1,1 В. Хотя более низкое напряжение питания снижает энергопотребление и продлевает срок службы батареи, оно также вызывает некоторые технические проблемы, такие как технические проблемы, такие как технические проблемы, такие как некоторые технические проблемы, такие как некоторые технические проблемы, такие как некоторые технические проблемы, такие как некоторые технические проблемы, такие как, например, как Некоторые технические проблемы, такие как, такие как технические проблемы, такие как, такие как некоторые технические проблемы. Например, это, скорее всего, будет нарушено шумом, что делает целостность сигнала более сложностью, потому что количество шума между напряжением между напряжением во время сигнального переключателя меньше и может повлиять на конструкцию.

Другое значительное изменение DDR5 отличается от того, как чип управления питанием (PMIC) DDR4 интегрируется на материнскую плату. DDR5 передал IC управления питанием (PMIC) из материнской платы в двойной модуль прямой памяти (DIMM).Это обеспечивает управление питанием, регулирование напряжения и последовательность питания -физическую ближе к устройству хранения на модуле, что также помогает обеспечить целостность источника питания (PI) и улучшить управление методом работы PMIC.

Кроме того, когда общее количество битов данных остается неизменным, количество каналов DIMM от 1 канала до 2 каналов также является важным прогрессом. Передавая данные в две узкие каналы передачи, его можно более эффективно сгенерировать и генерировать более эффективно назначать назначение. Сигналы часов для повышения целостности сигнала.

Очевидно, что разработка стандарта DDR5 также учитывала проблему целостности сигнала, и передача PMIC в модуль также будет оказывать соответствующие преимущества.Тем не менее, дизайнеры все еще должны учитывать общий эффект целостности сигнала источника питания.Как упомянуто выше, DDR5 имеет скорость передачи данных до 6,4 Гбит / с и тактовую частоту системы 3,2 ГГц. Мощный шум может вызвать более очевидные проблемы в этой высокоскоростной работе, что повлияет на производительность и стабильность системы.Если целостность мощности и целостность сигнала анализируются отдельно, проблема шума питания может быть пропущена.

Следовательно, для того, чтобы дать полную игру для производительности DDR5, все ключевые моменты системы должны включать чипы, упаковку и ПХБ для анализа целостности сигнала влияния питания.Тем не менее, анализ этого уровня является сложной задачей. Он имеет высокие требования для аппаратных и программных инструментов, используемых для анализа моделирования для базовой вычислительной платформы. Сложность и сложность проектирования.

Полностью освободить потенциал DDR5, Cadence

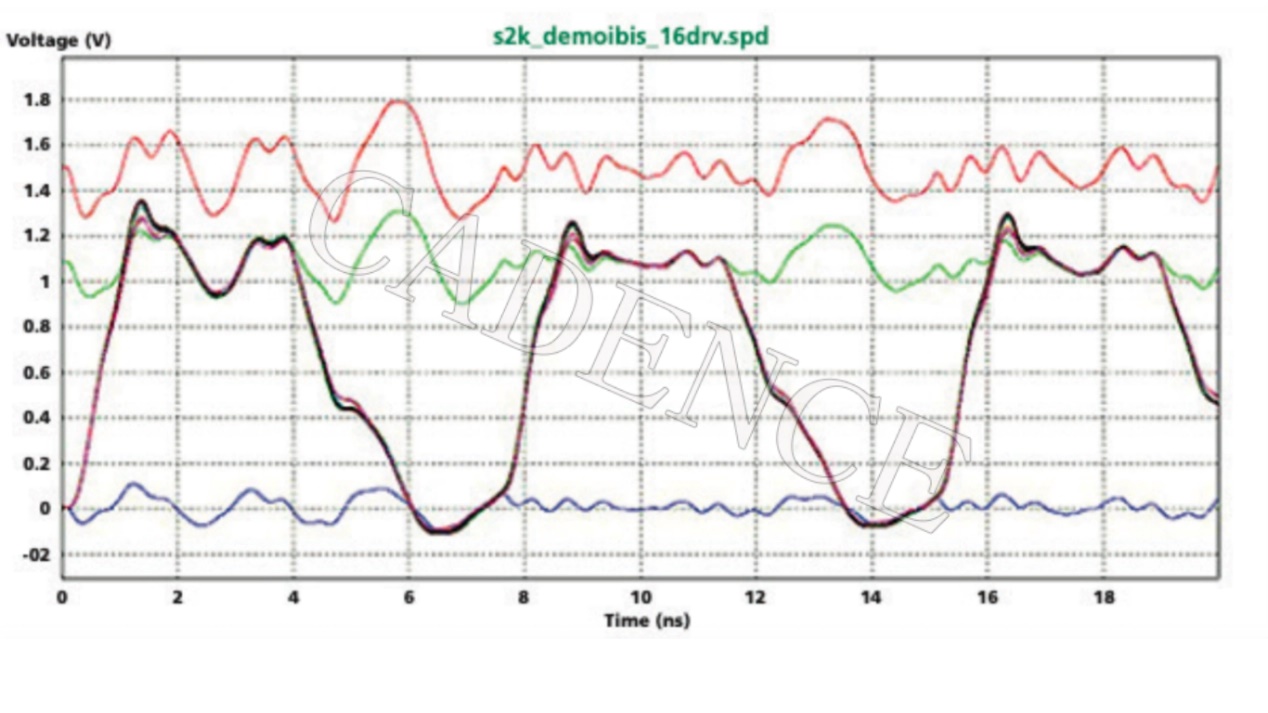

Уже в 2005 году концепция «с учетом влияния питания» дебютировала в первый раз. Это метод моделирования целостности расширенного сигнала, который может анализировать сигналы и шум питания одновременно (рис. 1).Решение целостности сигнала, которое учитывает влияние источника питания, должно учитывать отражение, строки, последовательные и другие эффекты, а также оснащены соответствующими методами моделирования и проверки правил.Стоит отметить, что для эффективного реализации моделирования целостности сигнала, которое учитывает влияние источника питания, необходимо выполнить на этапе анализа после регулярного осмотра и проводки, потому что взаимодействие/связь плоскости и сигнал происходит После завершения проводки.

Следовательно, полное решение, которое учитывает влияние источника питания часто необходимо предоставить:

l Набор решений быстрой проверки для ослабления сигналов и источника питания на сигналах

L может симулировать симулятор доменов времени больших цепей (результаты множества сигнальных сетей и сетей питания)

L мощность электроэнергии и моделирование сети сигналов

L Входной/вывод (ввод) буферный

Рисунок 1: Результат целостности сигнала как влияния источника питания

Хотя многие инструменты на рынке поддерживают основные стандарты моделирования ввода/вывода, которые учитывают влияние источника питания, благодаря непрерывной разработке технологии интерфейса памяти, требования рынка для инструментов целостности сигнала также увеличиваются. Точный инструмент извлечения для Сигнал связи, источник питания и сигнал заземления на печатной плате редки.

В связи с этим, как ведущее предприятие в области моделирования EDA, технология Sigrity X, запущенная Cadence, обеспечивает анализ целостности сигнала влияния источника питания для DDR4 и DDR5.

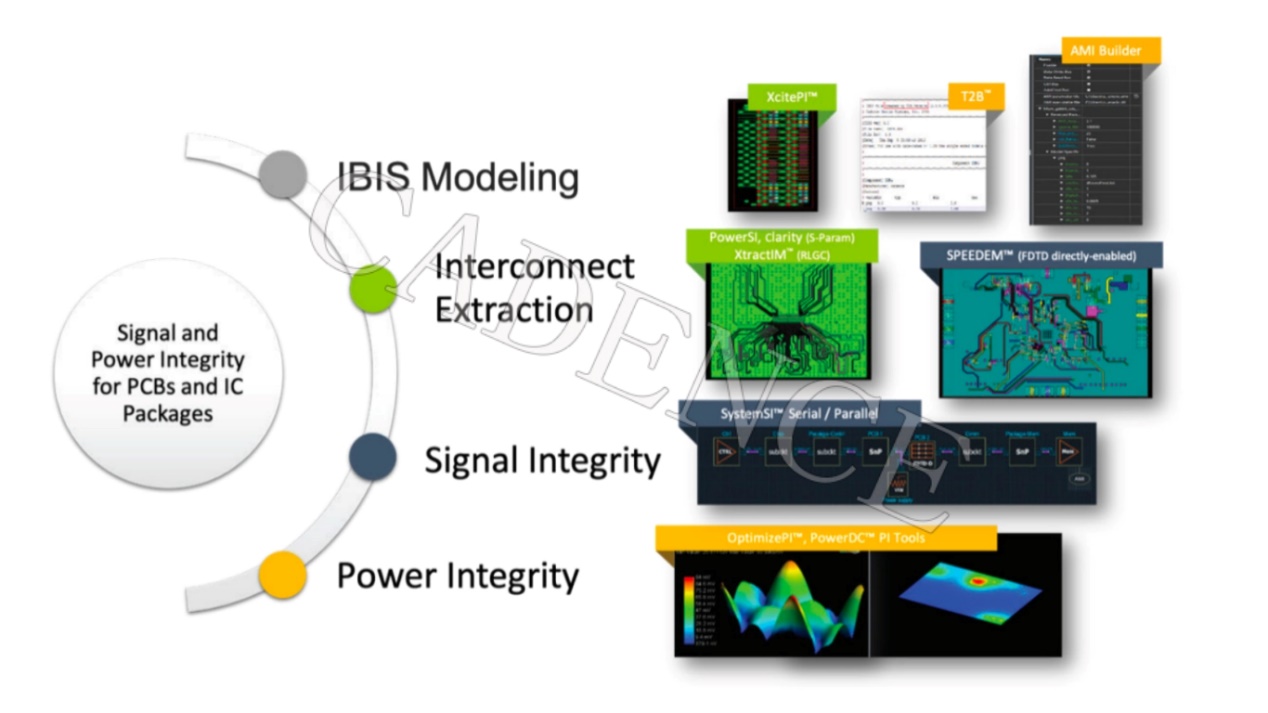

Технология SIGRITY X не только реализует точную извлечение связанных сигналов, источника питания и наземных сигналов на чипах, упаковке и печатной плате, но также может также эффективно моделировать отражение, потерю, бандидальную и синхронное выключатель (SSO). время.Дизайнеры, использующие технологию Sigrity, могут быстро преобразовать модель транзисторного уровня в модель IBIS поведенческого уровня, которая учитывает влияние власти, так что в течение нескольких часов она может обеспечить точное, эффективное и всеобъемлющее, учитывая моделирование эффектов питания, что значительно Захватывает первоначальное количество первоначально необходимо пронумеровать. Цикл дизайна Sky.(фигура 2)

Рисунок 2: Инструмент целостности и целостности мощности каденции для печатной платы и упаковки IC

Технология Sigrity X упрощает рабочий процесс, обеспечивает синхронное моделирование проектирования и точность уровня подписания для окончательной проверки.Сигналы, мощность и проблемы с теплом могут быть решены на каждой стадии проектирования, тем самым уменьшая количество итераций между командами дизайна и анализа.Дизайнеры могут запускать двигатель ядерного уровня при проектировании ткани для рисования для моделирования с высокой оценкой, тем самым обеспечивая высококачественную конструкцию для аналитических команд для проверки.Позже, группа по анализу использовала крупномасштабный параллельный моделирование двигателя Sigrity, чтобы сделать полное моделирование системы, чтобы гарантировать, что весь «пакетный пакет-pcb-shell» соответствует спецификациям проектирования и подготовлена к подписанию.

Эти преимущества делают Sigrity X лучшим решением для памяти DDR5 и интерфейса 112G.Его золотистое стандартное моделирование взаимодействия объединяет моделирование доменного домена (моделирование схемы и канала) анализа последовательных/решений (SERDES) и поддерживающего интерфейс моделирования алгоритма IBIS (AMI), который дает уникальные преимущества CADENC Полные решения.

Кроме того, в сочетании можно использовать технологию SIGRITY XTRACTIM и Clarity 3D RELVE Разрыв между.

Кроме того, технология SIGRITY Systems поддерживает модель IBIS, которая может быстро подключиться к влиянию источника питания и модели взаимосвязи, которая учитывает влияние источника питания. Проект может быстро определить наихудшую ситуацию с помощью этой технологии и сравнить ее с Стандарт jedec, чтобы гарантировать, что DDR4/DDR5 Интерфейс (включая требования к скорости кода) соответствует всем соответствующим спецификациям.

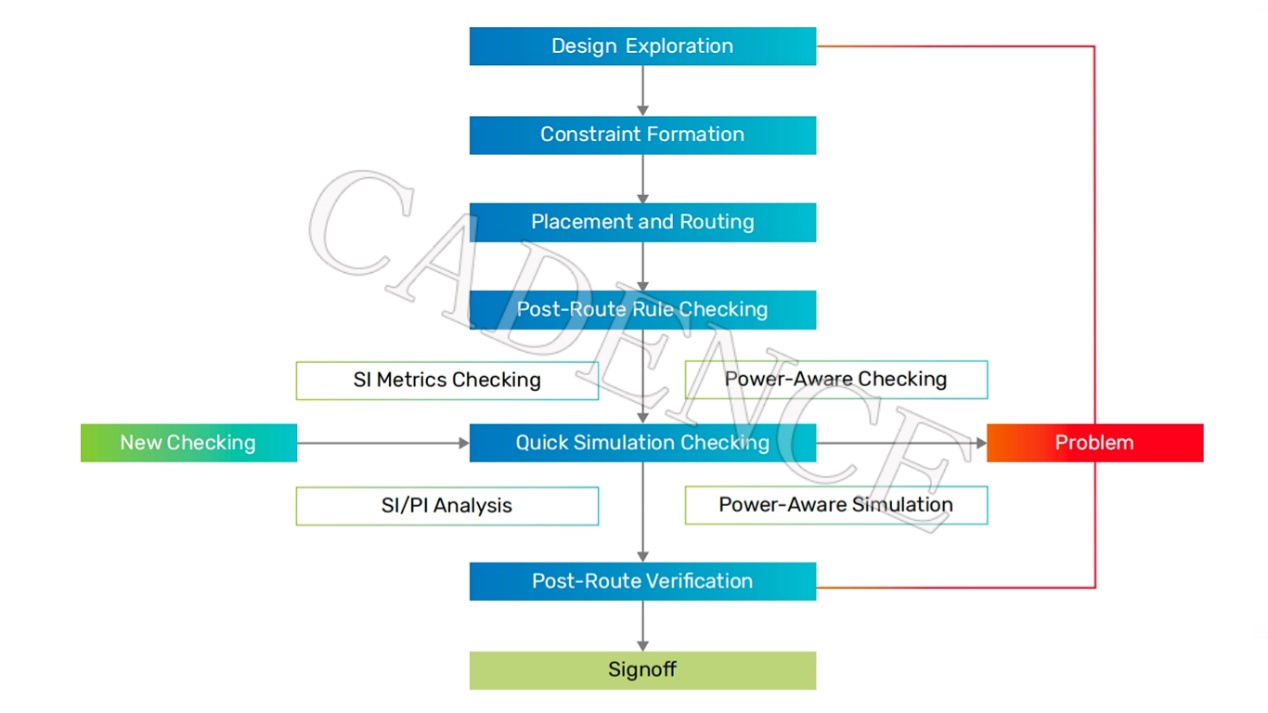

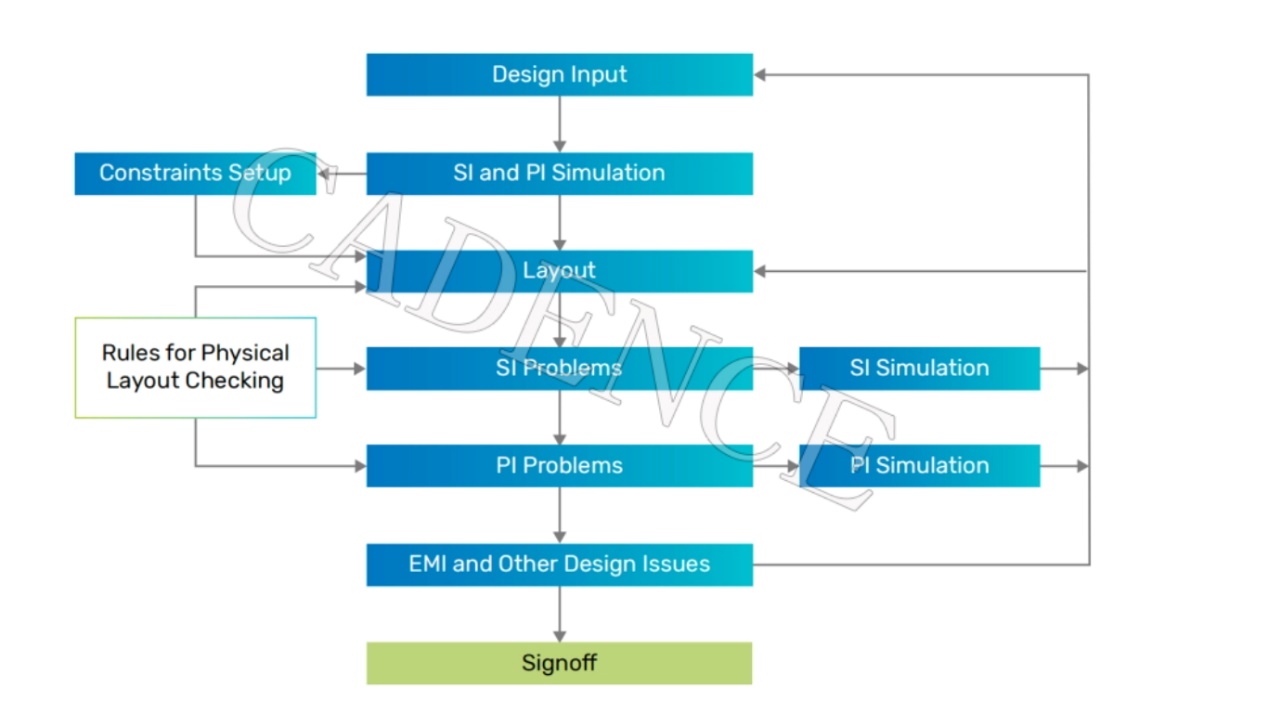

Рисунок 3 -это процесс проверки и моделирования, который учитывает влияние источника питания, которое резко контрастирует с традиционным процессом проектирования, вызванного ограничением (рис. 4).Процесс проектирования традиционных драйверов ограничений в основном включает в себя четыре части: предварительная проводка, формирование ограничений, проверка правил и проверку пост -проводной.

Рисунок 3: Cadence учитывает процесс ограничения влияния источника питания

ПРОТИВ

Рисунок 4: Пример традиционного процесса проектирования драйвера ограничения

Среди многих современных технологий моделирования часто существуют разъединения между анализом сигнала и сетью распределения мощности (PDN), и есть некоторые другие недостатки.При нормальных обстоятельствах, в соответствии с сложностью модели специй, иногда используйте моделирование временной области для генерации моделей точного сопротивления/индуктивности/конструктов (RLC), а иногда и предполагает идеальную плоскость заземления.Модель домена времени, полученная из этого, основана на простой частотной характеристике извлечения моделирования. Хотя она более удобна, она немного недостаточна с точки зрения точности. Для более высоких частот инженеры будут использовать параметры S, созданные с помощью смешанного решающего устройства.

Фактически, существует также эффективный метод объединения метода ограниченной разницы во времени (FDTD) со смешанным решающим устройством для расширения покрытия до сигнала, источника питания и линии заземления.

Успешным примером практики этого метода является инструмент двигателя Sygrity Speed Speed2000 Cadence. Он интегрирует и интегрирует выходные решения для решения проводки цепей, линий передачи и проблем с электромагнитным полем и может лучше отображать взаимодействие данных и мощности/заземления при разных раз.И используйте метод FDTD для анализа макета упаковки IC и печатной платы.Он обеспечивает важную справочную основу для дальнейшей оптимизации конструкции схемы.

При входе на окончательный этап подписания инженеры обычно имеют тенденцию использовать 3D -методы моделирования с полной волной для получения более высокой точности.Но это потребляет больше вычислительных ресурсов и увеличит время моделирования.Чтобы облегчить эту проблему, может быть принята технология разделения и параллелизации.В этом отношении, используя 3D -решатель Clarity для анализа анализа конечных элементов (FEM), а затем комбинируя технологию Sigrity Xtractim, результаты каждого анализа пересмотрены для формирования модели параметров A на основе частотной характеристики, тем самым достигая Вся система на всю систему или в ходе и точном анализе проектирования.

Подведем итог

В то же время, что и технологический скачок, технология была улучшена, и неизбежно сталкиваться с новыми проблемами для дизайнеров.На пути к памяти DDR5 и новыми проблемами, с острым «острым лезвием» Sadence Sigrity X, инженеры могут спокойно справиться со сложными проблемами целостности сигнала, гарантируя, что продукт не только согласуется со спецификациями. Он также сияет в Производительность, добавление еще одного кирпича к дороге будущих инноваций.