Noticias

Chip MIPS de 1 GHz destinado a la interfaz hombre-máquina

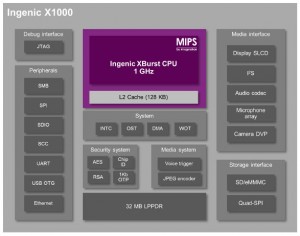

El núcleo tiene lo que Imagination Technologies, propietarios de núcleos MIPS, describe como un conjunto de características de "nivel móvil" con una unidad de punto flotante de doble precisión e instrucciones de aceleración multimedia / audio para decodificación de audio sin pérdidas. También hay un bloque de procesamiento multimedia y un subsistema de seguridad para AES y RSA de hasta 2.048 bits.

La potencia es 90 µW / MHz y 200 µW en espera.

El primer miembro de la familia es el X1000, destinado a aplicaciones como altavoces conectados, juguetes inteligentes, análisis de imágenes (reconocimiento de matrículas de automóviles, detección de rostros y huellas dactilares) o electrodomésticos inteligentes.

Multimedia

El códec de audio del motor multimedia admite una resolución de 24 bits y una relación señal / ruido de hasta 95 dB.

También hay un motor de reconocimiento de voz de baja potencia siempre encendido con filtros de hardware para detectar y actuar sobre comandos de voz. "Por ejemplo, los desarrolladores pueden usar una matriz de cuatro micrófonos para realizar la cancelación de ruido y el posicionamiento de la voz", dijo Imagination, que está promoviendo el microcontrolador.

Para las cámaras, hay un codificador que codifica 1,280 x 720 imágenes en <30ms.

Desarrollo

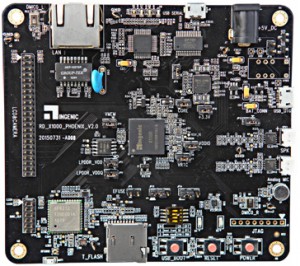

Para el desarrollo hay una placa que ejecuta Linux, marca Phoenix, que tiene una X1000 con 16Mbyte flash, una ranura micro SD (hasta 32GB), 802.11b / g / n Wi-Fi, Bluetooth 4.0, 10 / 100M Ethernet, USB OTG , tres puertos de micrófono y JTAG. Se proporcionan encabezados de expansión para una pantalla, cámara y ZigBee.

Para el desarrollo hay una placa que ejecuta Linux, marca Phoenix, que tiene una X1000 con 16Mbyte flash, una ranura micro SD (hasta 32GB), 802.11b / g / n Wi-Fi, Bluetooth 4.0, 10 / 100M Ethernet, USB OTG , tres puertos de micrófono y JTAG. Se proporcionan encabezados de expansión para una pantalla, cámara y ZigBee.

"Si los desarrolladores desean integrar rápidamente estos nuevos chips en sus productos, Ingenic también suministrará otro módulo informático llamado Halley2 que incluye el SoC X1000, 16Mbytes de memoria flash, un chip de Wi-Fi y Bluetooth dedicado y un IC de administración de energía". dijo Imaginación.

| UPC | CPU XBurst 1.0GHz, basada en MIPS Hardware FPU, SIMD 16kbyte L1 I-cache 16kbyte L1 D-cache 128kbyte L2 caché unificado |

| Memoria | Admite LPDDR de 16 bits, DDR2, DDR3 32Mbyte LPDDR en paquete |

| Monitor | Interfaz paralela SLCD de 8, 9 y 16 bits |

| Cámara | Interfaz paralela de 8 bits, hasta 2.0Mpixel Codificación JPEG de hardware 1.280 × 720 30 fps Soporte de entrada CCIR656 |

| Audio | Códec de audio con ADC estéreo y DAC Controlador DMIC con motor de activación por voz I2S / SPDIF para códec de audio externo Interfaz PCM, modo maestro y esclavo |

| Otro interfaces | yo2C (x3) SPI USB 2.0HS OTG MMC / SD / SDIO (x2) UART full-duplex (x3) Interfaz flash serie Interfaz de tarjeta inteligente I2S PCM MAC Ethernet |

| Seguridad | Memoria de 1kbit OTP Hardware RSA (2048 bits) y AES (256 bits) Arranque de seguridad |

| Paquete | 13 x 13 x 1.2 mm, BGA-190, paso de 0.8 mm |

| OS | Linux 3.0 y posterior |