News

The DDR5 era is approaching, and new challenges cannot be ignored

- Author:ROGER

- Release on:2023-12-04

In the frenzy of artificial intelligence (AI), machine learning (ML), and data mining, our desire for data processing shows unprecedented index growth.Facing this prospect, the width of memory bandwidth has become a key "arteries" in the digital age.Among them, DDR (DOUBLE DATA RATE) technology, known for double data transmission rates and higher bandwidth as a dynamic random access memory (DRAM), has greatly promoted the improvement of computer performance.From the birth of the first generation of DDR technology in 2000, to DDR5 in 2020, each generation of DDR technology has achieved significant improvements in various aspects such as bandwidth, performance and power consumption.

Today, whether it is PC, laptop or artificial intelligence, various industries are accelerating to move towards the new era of DDR5.This year, the generation AI market is booming, and AI servers used in large model applications have vigorously promoted the demand for DDR5.With the recovery of the demand for memory market, memory chip suppliers have shown the production capacity of DDR5 in the fourth quarter of this year to gradually replace the current DDR4.

The new era of DDR5 has arrived, however, some challenges have also hindered the further development of the industry.

DDR5 era: design challenges behind ultra -high -speed performance

In July 2020, the DDR5 memory technology standard was officially released, marking that memory technology opened a new chapter.DDR5 has attracted widespread attention with higher bandwidth and performance.Compared with the previous DDR4, the biggest advantage of DDR5 is that it has significantly reduced power consumption and doubled the bandwidth.Specifically, the highest rate of DDR5's current release protocol has reached 6.4GbpsThe clock frequency also increased from 1.6GHz to 3.2GHz.

When we explore more details of DDR5, we also find that this new technology has brought some additional technical challenges.For example, the power supply voltage of DDR5 decreases by 0.1V by 1.2V from DDR4, reaching 1.1V. Although the lower power supply voltage reduces power consumption and extend the battery life, it also brings some technical challenges, such as such as technical challenges, such as such as technical challenges, such as, such as some technical challenges, such as, such as some technical challenges, such as, such as some technical challenges, such as, such as some technical challenges, such as, such as some technical challenges, such as, such as technical challenges, such as, such as some technical challenges. For example, It is more likely to be disturbed by noise, which makes the signal integrity more challenging, because the amount of noise between the voltage between the voltage during the signal switch is less and may affect the design.

Another major change of DDR5 is different from the way the power management chip (PMIC) of DDR4 is integrated on the motherboard. DDR5 transferred the power management IC (PMIC) from the motherboard to the dual -column direct memory module (DIMM).This enables the power management, voltage regulation and power -on sequence to physical closer to the storage device on the module, which also helps ensure the power supply integrity (PI) and enhance the control of the PMIC operation method.

In addition, when the total number of data bits remains unchanged, the number of DIMM channels from 1 channel to 2 channels is also an important progress. By transmitting data into two narrow channel transmission, it can be more effectively generated and generated more effectively Assign clock signals to improve signal integrity.

Obviously, the development of the DDR5 standard has also taken into account the signal integrity problem, and the transfer of PMIC to the module will also exert the corresponding advantages.However, designers still need to consider the overall effect of the signal integrity of the power supply.As mentioned above, DDR5 has a data rate of up to 6.4Gbps and the 3.2GHz system clock frequency. Power noise may cause more obvious problems in this high -speed operation, which will affect system performance and stability.If the power integrity and signal integrity are analyzed separately, the problem of the noise of the power supply may be missed.

Therefore, in order to give full play to the performance of DDR5, all key points of the system must include chips, packaging, and PCB for signal integrity analysis of the influence of power supply.However, the analysis of this level is a complex task. It has high requirements for the hardware and software tools used for simulation analysis for the underlying computing platform. The difficulty and complexity of design.

Fully release the potential of DDR5, Cadence

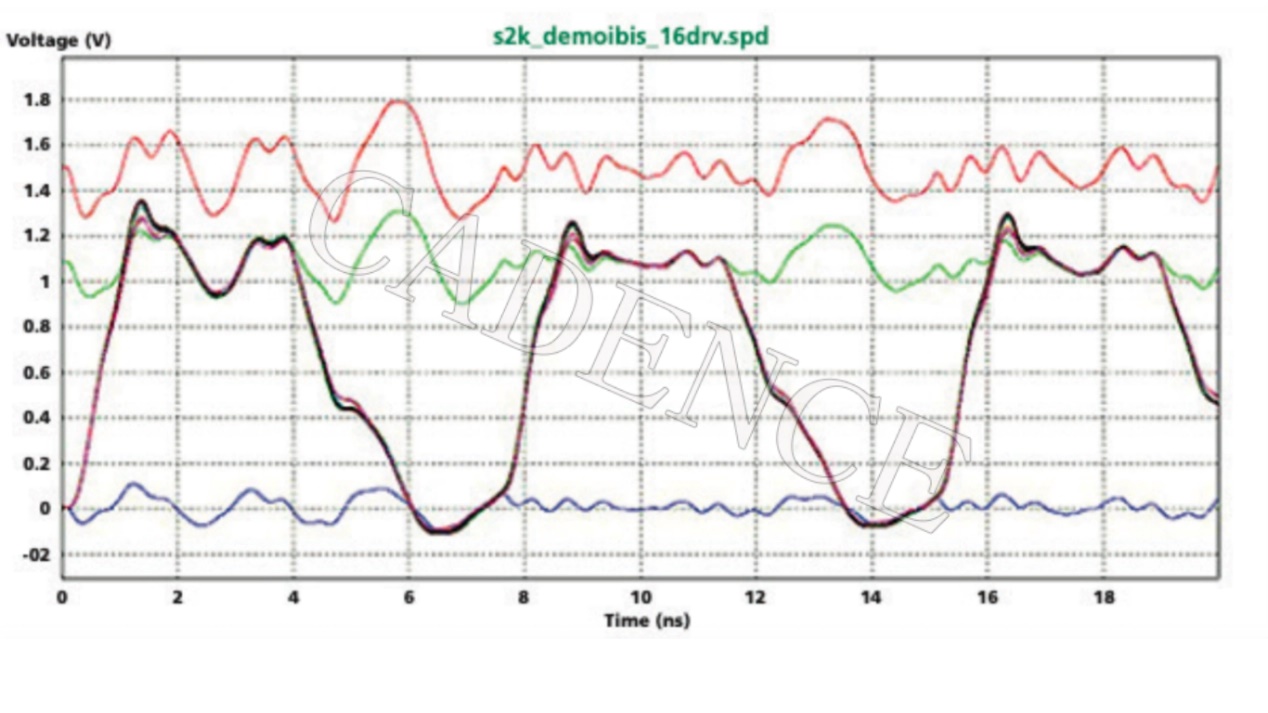

As early as 2005, the concept of "taking into account the influence of power supply" debuted for the first time. It is a advanced signal integrity simulation method that can analyze signals and power noise at the same time (Figure 1).The signal integrity solution that takes into account the influence of the power supply must consider reflection, stringing, sequential and other effects, and equipped with corresponding simulation and rules inspection techniques.It is worth noting that in order to effectively implement the signal integrity simulation that takes into account the impact of power supply, it is necessary to perform in the analysis phase after regular inspection and wiring, because the interaction/coupling of the plane and signal occurs after the wiring is completed.

Therefore, a complete solution that takes into account the influence of power supply often needs to be provided:

l A set of fast inspection solutions for signal attenuation and power supply on signals

l can simulate the time domain simulator of large circuits (the results of multiple signal networks and power networks)

L power network and signal network modeling

l High -level input/output (I/O) buffer modeling

Figure 1: The result of the signal integrity of both the influence of the power supply

Although many tools on the market support the basic I/O modeling standards that take into account the influence of power supply, with the continuous development of memory interface technology, the market's requirements for signal integrity tools are also increasing. The accurate extraction tool for the coupling signal, power supply and ground signal on PCB is rare.

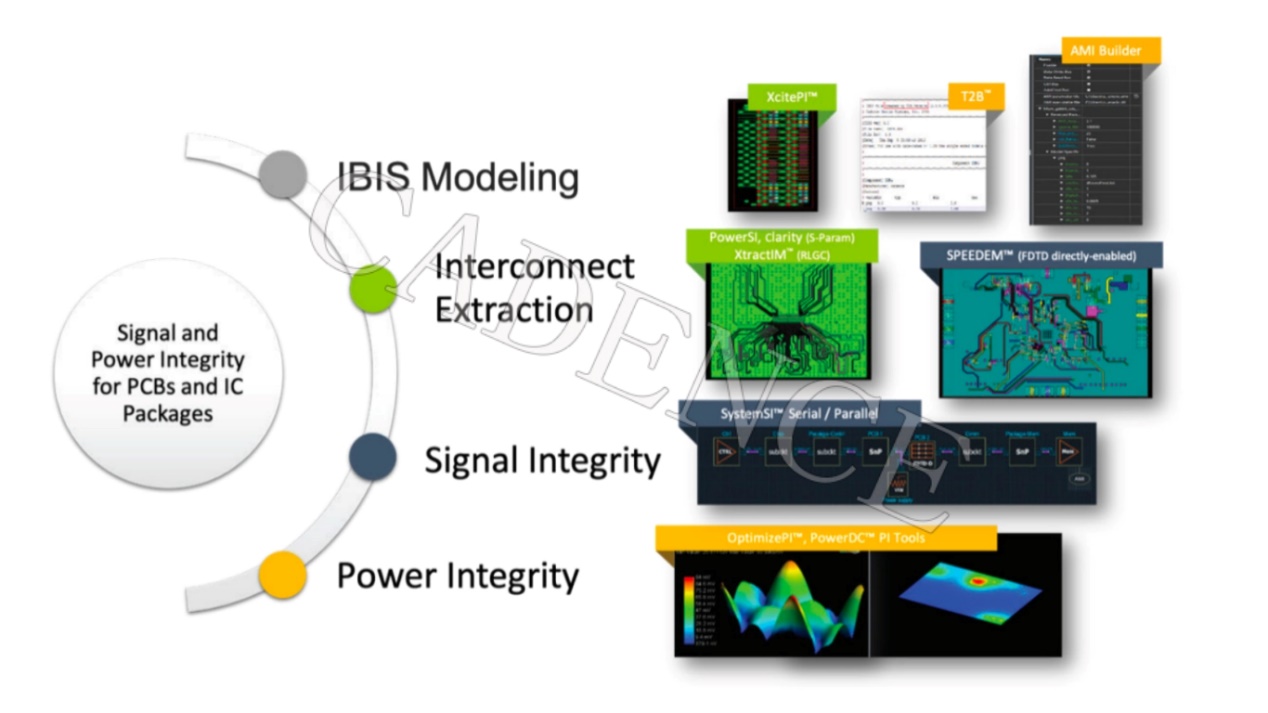

In this regard, as a leading enterprise in the field of EDA simulation, the SIGRITY X technology launched by Cadence provides a signal integrity analysis of the influence of power supply for DDR4 and DDR5.

SIGRITY X technology not only realizes the precise extraction of coupled signals, power supply and ground signals on chips, packaging and PCB, but also can also make efficient simulation on reflection, loss, bandidal, and synchronous switch output (SSO) effects at the same time.Designers using Sigrity technology can quickly convert the transistor -level model into a behavioral -level IBIS model that considers the influence of power, so that within a few hours, it can provide precise, efficient and comprehensive considering simulation of power supply effects, which greatly shortens the original number of originally needs to be numbered. Sky design cycle.(figure 2)

Figure 2: Cadence signal integrity and power integrity tool for PCB and IC packaging

SIGRITY X technology simplifies the workflow, provides design synchronous simulation and the accuracy of the signing level for final verification.Signals, power, and heat problems can be solved at each design stage, thereby reducing the number of iterations between the design and analysis teams.Designers can run the nuclear -level engine in the design of the drawing cloth for high -precision simulation, thereby providing high -quality design for analysis teams to verify.Later, the analysis team used the large-scale parallel simulation engine of Sigrity to make full system simulation to ensure that the entire "chip-packaging-PCB-shell" meets the design specifications and prepare for the signing.

These advantages make Sigrity X the best solution for DDR5 memory and 112G interface.Its golden standard interconnect modeling combines the time domain simulation (circuit and channel simulation) of the serial/solution (Serdes) analysis and supporting the IBIS algorithm modeling interface (AMI), which gives Cadence unique advantages, thereby Can extract and interface compliance signing provides complete solutions.

Further, Sigrity Xtractim and Clarity 3D Solver technology can be used in conjunction, which allows engineers to create complete packaging models containing coupling signals, power supply and grounding interconnect models for various types of packaging, which effectively make up for the packaging design and package characteristics The gap between.

In addition, Sigrity SystemsI technology supports the IBIS model that can quickly connect to the influence of power supply and the interconnection model that takes into account the influence of power supply. The designer can quickly determine the worst situation through this technology and compare it with the JEDEC standard to ensure that DDR4/DDR5 The interface (including the bitless code rate requirements) meets all relevant specifications.

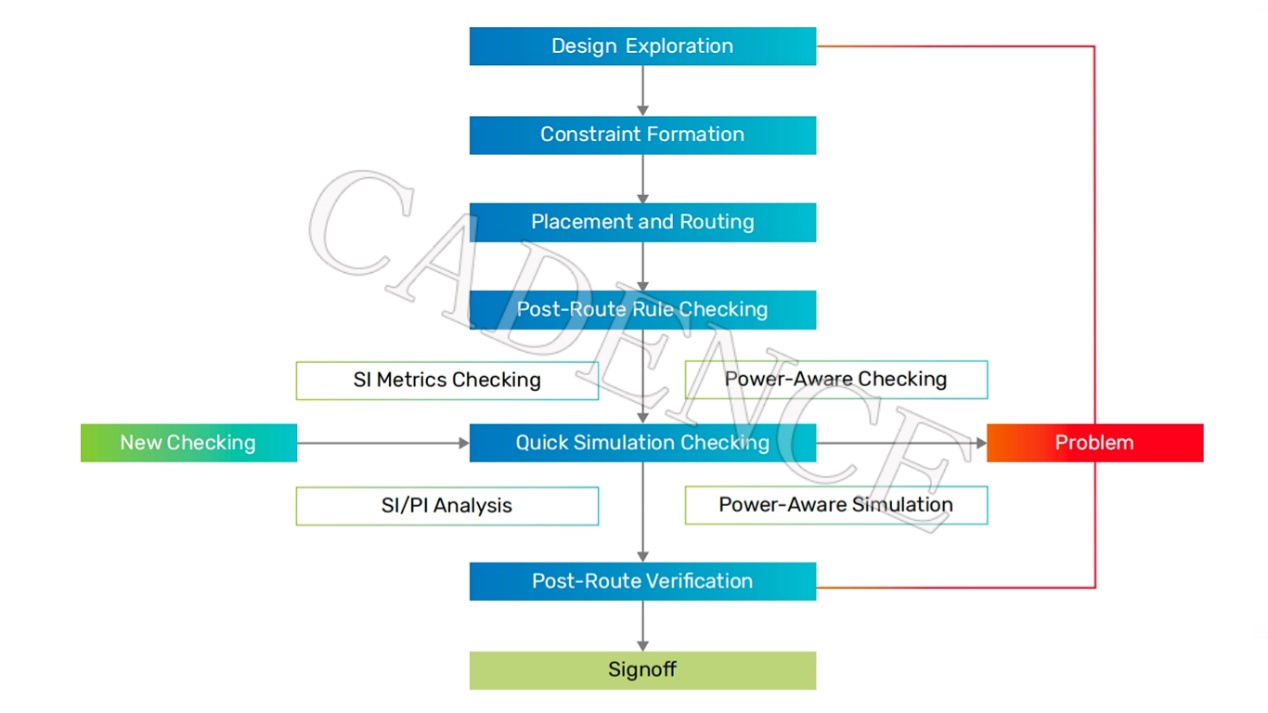

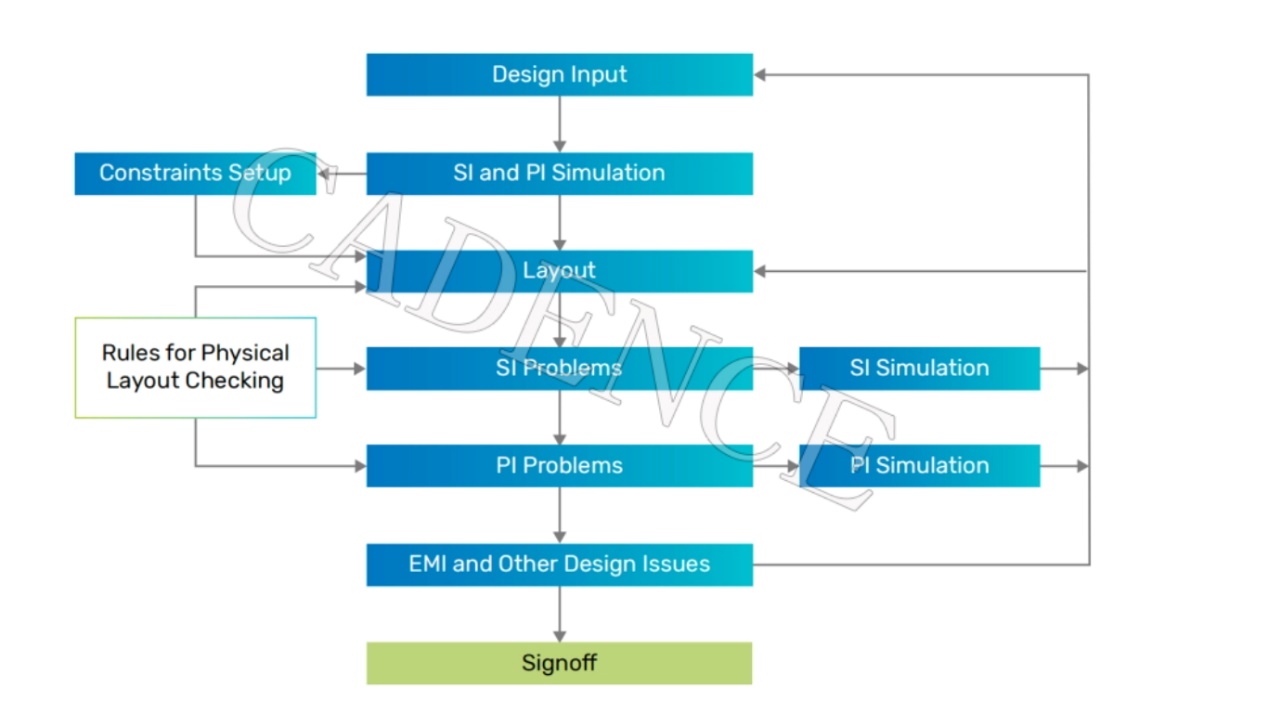

Figure 3 is the inspection and simulation process that takes into account the influence of the power supply, which is in sharp contrast to the traditional constraint -driven design process (Figure 4).The design process of traditional constraint drivers mainly includes four parts: pre -layout wiring, constraint formation, rules inspection, and post -wiring verification.

Figure 3: Cadence takes into account the process of constraint driver of the influence of power supply

VS

Figure 4: Example of traditional constraint driver design process

Among the many current simulation technologies, there are often disconnects between signal analysis and power distribution network (PDN), and there are some other shortcomings.Under normal circumstances, according to the complexity of the spice model, sometimes use time domain simulation to generate accurate resistance/inductance/capacitors (RLC) models, and sometimes it assumes an ideal ground plane.The time domain model obtained from this is based on the simple frequency response of simulation extraction. Although it is more convenient, it is slightly insufficient in terms of accuracy. For higher frequencies, engineers will use the S parameters created by a mixed solving device.

In fact, there is also an efficient method to combine the limited difference time domain (FDTD) method with the mixed solving device to expand the coverage to signal, power supply and grounding line.

The successful practice case of this method is Cadence's Sigrity Speed2000 engine tool. It integrates and integrates the output of several solutions to solve the circuit wiring, transmission lines and electromagnetic field problems, and can better display the data and power/ground plane Interaction at different times.And use the FDTD method to analyze the layout of IC packaging and PCB.It provides an important reference basis for the further optimization of circuit design.

When entering the final signing stage, engineers usually tend to use 3D full -wave modeling methods to obtain higher accuracy.But this will consume more computing resources and increase the simulation time.To alleviate this problem, division and parallelization technology can be adopted.In this regard, by using the Clarity 3D Solver for a finite element analysis (FEM) analysis, and then combining Sigrity Xtractim technology, the results of each analysis are re -combined to form a S parameter model based on frequency response, thereby achieving the entire system to the entire system Or in -depth and precise analysis of design.

Summarize

At the same time as the technological leap, the technology has been improved, and it is inevitable to lay new challenges for designers.On the way towards DDR5 memory and new challenges, with the sharp "sharp blade" of Cadence Sigrity X, engineers can calmly cope with the complex issues of signal integrity, ensuring that the product is not only consistent with the specifications. It also shines in performance, adding another brick to the road of future innovation.